一个电路板从射频设计到实现是经过什么步骤?

描述

一个电路板从设计到实现是经过什么步骤?

从顶层设计来讲,首先是射频方案的选择。

射频框架

射频方案设计来设计去,就那三种设计方案,超外差,零中频,低中频。

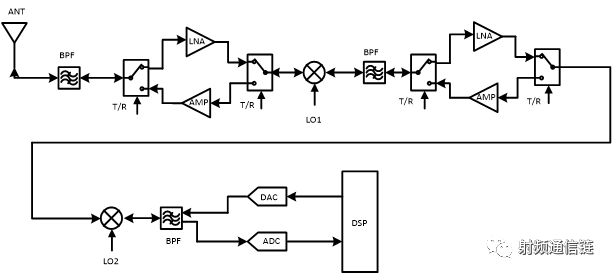

超外差

超外差方案实现了频谱搬移,所以可以通过频谱搬移、中频滤波器把很多干扰频率滤除,而且相对而言超外差方案如果不考虑对别人的发射影响,超外差方案只在接收的抗干扰上有优势。

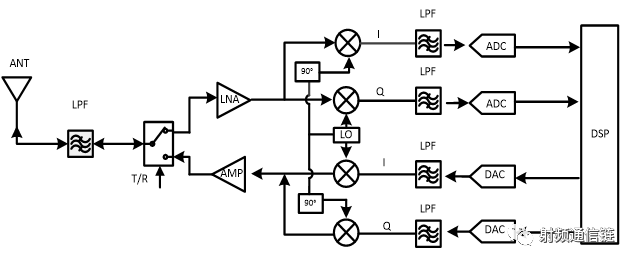

零中频

零中频架构,将射频直接变成基带信号。所以零中频在尺寸、功耗上都很有优势。这也是方案时选择这个方案最重要的考虑。

因为零中频是正交变换,所以硬件的不一致,会导致零中频方案出现因为差分正交不平衡带来的频谱拓展。

低中频方案,为了规避零中频存在的问题,在ADC之前做了一次变频处理。因为是在FPGA做处理,所以相对超外差方案比,尺寸和功耗有优势。

方案选择的原则就是侧重什么就选择相应的方案

侧重射频指标的一般用超外差,因为中频滤波器的存在,可以比较容易的实现高指标。

侧重尺寸和功耗的,一般选择零中频方案。

低中频的方案主打的也是功耗和尺寸,对于一些实时更新的收发设计,零中频设计在直流和偏差会存在差异,一般采用低中频方案来规避。

落实到器件选择

器件的选择主要是锁相环、放大器、混频器和外围电路。

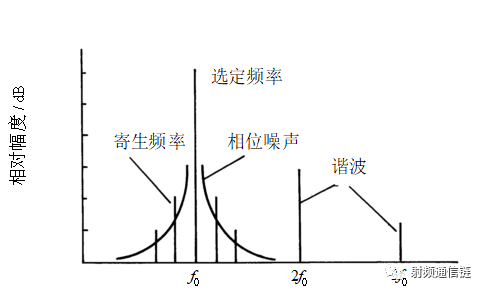

锁相环

锁相环的选型关系到发射和接收链路的关键指标,锁相环也是杂散的关键来源之一。所以锁相环的选择至关重要。

在功耗设计允许的条件下,相位噪声越高越好。

放大器

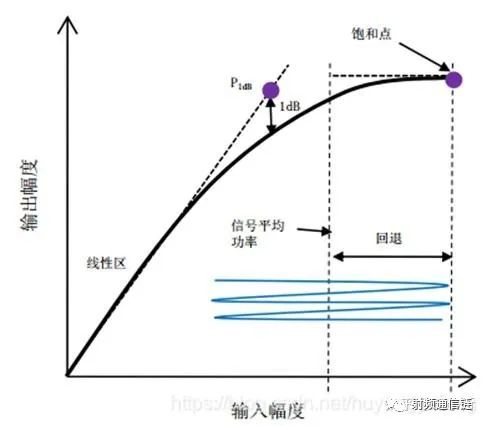

之前的文章我们讲过,收发电路的设计就是设计整个收发系统的线性,整个收发电路中用的最多的也是放大器

LNA决定接收系统的NF和IIP3。

PA决定了发射系统的EVM。

放大器的选型原则是线性越高越好,效率越高越好。

混频器

混频器作为频率变化的节点,它也是指标设计的关键节点。

很多人对指标的前后分配不知如何设计,

现有的混频器的p-1基本上都在10左右,混频器也是超外差方案相位噪声的卡点处。

所以混频器作为中间节点,就成为了指标分配的节点。

根据混频器的p-1和频率源的相位噪声,就可以设计混频前后的增益,动态范围,滤波器,宽带噪声等指标的设计分配。

外围电路

外围电路包括检波,ADC\DAC,运放,温度检测、电源等设计。

检波器的选择注意需要根据波形和切换时间选择到底是峰值还是RMS检波器。

外围电路的选择和设计主要是为了完成主要电路服务,在设计上按照需求选择合适的电路。

这里主要说一下电源

上面说到锁相环是杂散的关键来源之一。

还有一个杂散的关键来源就是电源,电路中因为P-1和器件的应用问题,所需要的电压也不同,为了提升整个设计的效率,通常会使用DC-DC。

而在DCDC的使用过程中,就可能会出现开关频率和cross频率,这两种频率会调制到锁相环和放大器上,形成杂散输出。

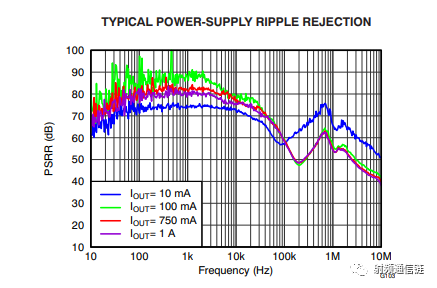

所以在DC设计时,需要注意DC的PSRR。一般来说杂散要求60dB,PSRR的要求就需要高于杂散的设计要求。

仿真、原理图设计

关键器件选择完毕,就需要设计原理图了,原理图的设计原则是能用简单设计就用简单设计,能用熟悉器件就用熟悉的器件。

仿真就不用说了,都是射频工程师的拿手好戏。

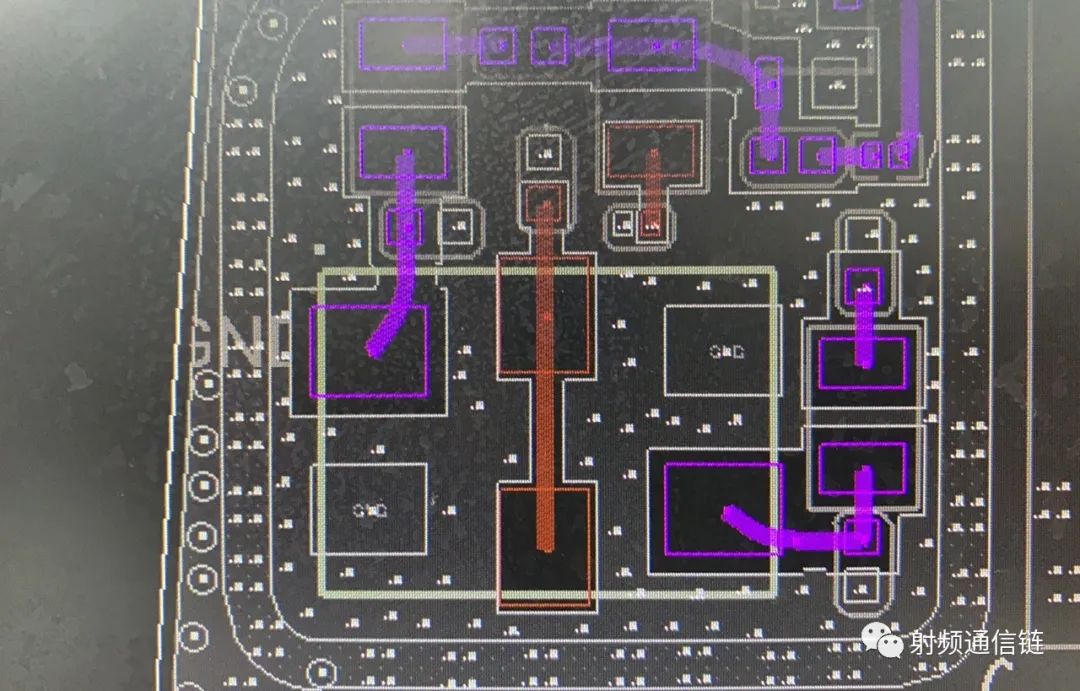

PCB设计

PCB的设计原则是敏感器件离电源越远越好,注意关键走线的阻抗和隔离。另外要强调一点,很多设计都说要数字地和模拟地隔离,对于射频PCB布局来说,最好一块地,隔离地可能会出现不想要的东西。

调试查问题

调试不怕出现问题,最怕的是出现问题却分析不出问题。

出现问题具体分析,最多的问题就是匹配,隔离等。

问题一般来说都没有想象的复杂,找到了之后可能就是一个走线,一个电感,甚至一个过孔。

结语

工程问题是基于可靠的理论实践,不会出现无法解释的问题。追本溯源,往往会射频设计并不难。

审核编辑:刘清

-

电路板测试步骤有哪些 电路板测试仪器有哪些2024-05-28 5648

-

电路板抄板的五大步骤2023-11-18 5553

-

射频电路的设计与实现2023-09-05 2512

-

射频PCB电路板的抗干扰设计2023-06-08 1078

-

射频印制电路板的设计如何解决信号干扰2023-05-16 1599

-

射频电路板设计技巧.zip2022-12-30 505

-

射频电路板设计法则2022-10-28 3045

-

射频电路板设计的要点2020-05-25 1934

-

电路板维修技术的步骤与技巧介绍2019-08-13 46152

-

射频电路板设计问题探讨2019-06-21 2065

-

射频计的热管理从选择电路板开始2017-11-14 1243

-

射频电路板设计技巧2017-01-28 1050

-

业余制作电路板方法及步骤2009-12-15 6312

全部0条评论

快来发表一下你的评论吧 !