eMMC的结构和电源配置

描述

最新的eMMC产品遵循JEDEC eMMC 5.1标准,该标准定义了eMMC的通信信号、命令、内部寄存器、特性,并为系统设计人员提供指导。它是工业应用和汽车应用的嵌入式存储解决方案的理想选择,这些应用需要在广泛的工作温度范围内具有高性能。eMMC也是Nand Flash的一种,属于并行类别,由于控制系统的不同以及速率差异,将eMMC独立出来,其容量可以覆盖到很大的区间,从1GB到256GB甚至更高,采用8位并行数据接口。

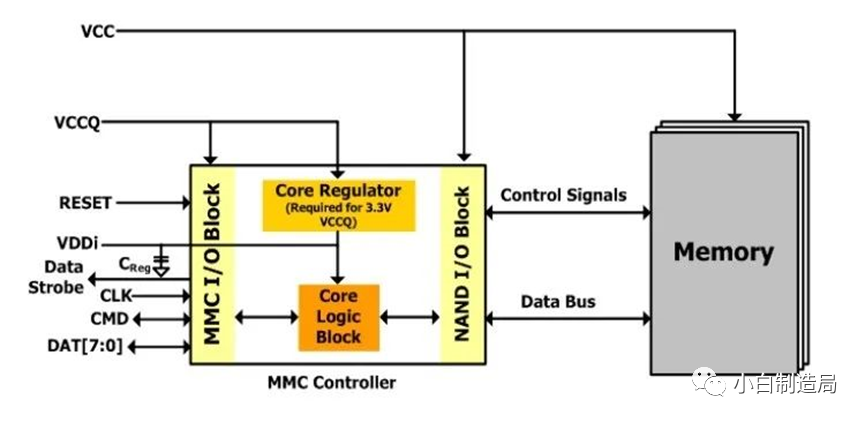

1.1 结构图

eMMC是使用MMC协议v5.1一个简单的读写内存。eMMC将TLC模式Nand和eMMC控制器封装在内部,作为一个JEDEC标准封装,为主机提供标准接口。eMMC控制器(三星称为FTL:过渡层)直接管理Nand Flash,包括ECC、损耗均衡、IOPS优化和读取感应、CMD/区块管理。

图1 eMMC结构

从图 1可以看到,eMMC包括控制器,MMC接口,Nand接口和Nand闪存单元。VDD(VCCQ)用于控制器电源(接口电源),VCC用于闪存电源。RESET用于复位。

1.2 数据接口定义

CLK

用于从 Host 端输出时钟信号,进行数据传输的同步和设备运作的驱动,频率为0-200MHz。在一个时钟周期内,CMD 和 DAT0-7 信号上都可以支持传输1个比特,即 SDR (Single Data Rate) 模式。此外,DAT0-7 信号还支持配置为 DDR (Double Data Rate) 模式,在一个时钟周期内,可以传输2个比特。

Host可以在通讯过程中动态调整时钟信号的频率(范围需要满足 Spec 的定义)。通过调整时钟频率,可以实现省电或者数据流控(避免 Over-run 或者 Under-run)功能。在一些场景中,Host还可以关闭时钟,例如 eMMC 处于 Busy 状态时,或者接收完数据进入Programming State 时。

CMD

CMD 信号是设备初始化和命令传输的双向通道,主要用于 Host 向 eMMC 发送 Command 和 eMMC 向 Host 发送对应的 Response。CMD信号有2种工作模式:

1#:漏极开路 ---> 用于初始化模式

2#:推拉模式 ---> 用于快速命令传输

DAT [7:0]

双向数据信号,DAT0-7 信号主要用于 Host 和 eMMC 之间的数据传输。在eMMC上电或软复位(即重置)后,只有 DAT0 可以进行数据传输(模式0)。完成初始化后,可配置 DAT0-3(模式4)或者 DAT0-7(模式8)进行数据传输,即数据总线可以配置为 4 bits 或者 8 bits 模式。

DAT信号在推挽模式下工作。数据线DAT0-DAT7内部上拉。进入4位模式后,eMMC立即断开线路DAT0、DAT2和DAT3的内部上拉。进入8位模式后,eMMC立即断开线路DAT0-DAT7的内部上拉。

Data Strobe

Data Strobe 时钟信号由 eMMC 发送给Host,频率与 CLK 信号相同,用于 Host 端进行数据接收的同步。Data Strobe 信号只能在 HS400 模式下配置启用,启用后可以提高数据传输的稳定性,省去总线 tuning 过程。

对于数据输出,该信号的每个周期指示数据上的两位传输(2x)-- 一位用于上升沿,另一位用于下降沿,对于CRC状态响应输出和CMD响应输出。

RESET

低电平复位,工作后为高电平。

1.3 eMMC的电源

表格 1是eMMC的电源配置,Nand区域(VCC)需要3V电压,而MMC控制器支持1.8V或3.3V双电压(VDD或VCCQ)。

表格 1 不同类型下的电源配置

| 类型 | 电压范围 | VCC | VCCQ |

|---|---|---|---|

| 4.51/5.0/5.1à3.3V | VCC: 2.7-3.6V; VCCQ(双电压): 1.70-1.95V/2.7-3.6V | NAND核心+NAND接口电压 | 嵌入式控制器内核eMMC接口电压 |

| 5.1à1.8V | VCC: 2.7-3.6V; VCCQ(单电压): 1.70-1.95V | NAND核心+NAND接口电压 | 嵌入式控制器内核eMMC和NAND接口电压 |

通电时电源电压必须单调上升,无下降;断电时电源电压必须单调下降,无颠簸。内部电压检测器在VCC和VCCQ下降时保证EMMC各项功能正常,其中VCC=2.7V-3.6V;VCCQ=1.70V-1.95V或者2.7V-3.6V。VCC和VCCQ在每个工作电压范围内达到稳定状态之前,主机不得发出任何命令。

图 2 eMMC理想上下电

如果VCC低于重置阈值,比如2.43V,VCCQ低于重置阈值,比如1.43V,内部WP线就会拉低以禁用闪存阵列编程/擦除操作。

1.4 硬件复位

使用硬件复位功能,主机必须将ECSD寄存器162字节,[1:0]位设置为0x1,以便在主机可以使用其之前启用该功能。执行复位操作之前,主机必须在尚未执行任何操作的情况下,根据JEDEC规范在RST_N引脚处至少保持1us的低电平。如果复位引脚回到高电平,则eMMC阻止任何操作,并进入预空闲状态,如图 3所示。

图 3 硬件复位

-

国产!全志T113-i 双核Cortex-A7@1.2GHz 工业开发板—eMMC配置核心板使用说明(二)2025-09-10 750

-

EMMC与SSD存储的比较2024-12-25 5941

-

RK3568修改eMMC分区大小2024-09-13 2594

-

eMMC总线协议解析2023-12-08 5262

-

如何把文件系统烧到EMMC并从EMMC加载2023-10-30 5614

-

EMMC主控固件读取及SD转emmc接线2023-08-10 1192

-

eMMC如何配置以在HS200模式下运行?2023-03-15 815

-

SD NAND与eMMC优劣势对比2022-06-17 3058

-

emmc,什么是emmc2011-08-23 83347

-

基于SD卡测试结构的EMMC测试座,EMMC测试治具说明书2011-04-28 11255

全部0条评论

快来发表一下你的评论吧 !