Xilinx FPGA IP之Block Memory Generator AXI接口说明

描述

之前的文章对Block Memory Generator的原生接口做了说明和仿真,本文对AXI接口进行说明。

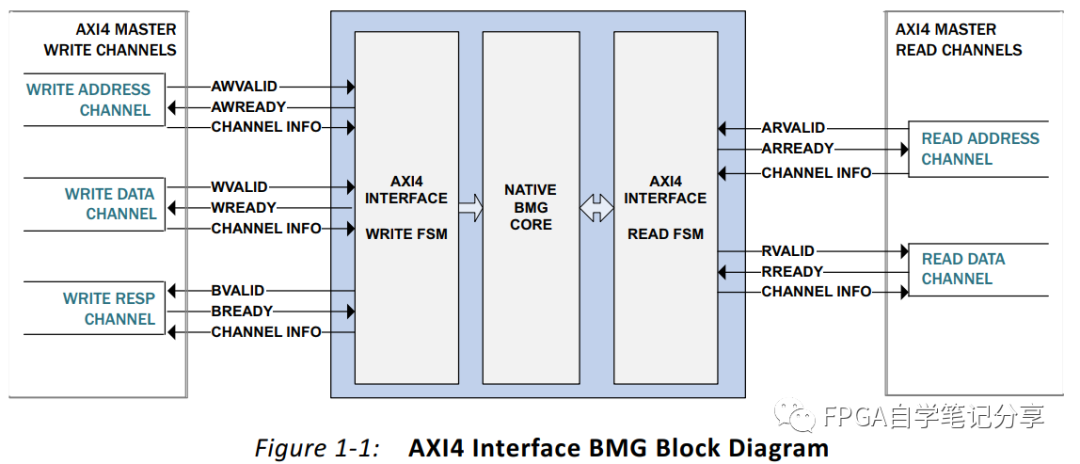

如下图所示,AXI4接口的BMG是基于原生接口进行包装的。有两种可用的AXI4接口样式:AXI4和AXI4- lite。

典型的应用场景包括:

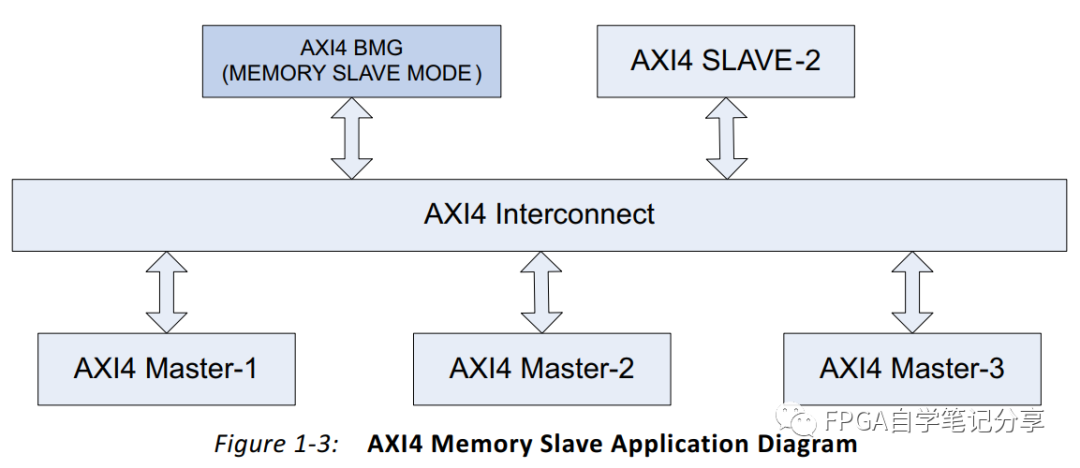

1、AXI4 Block Memories–Memory Slave Mode:内存从属模式下的AXI4块MEM,如下图所示。

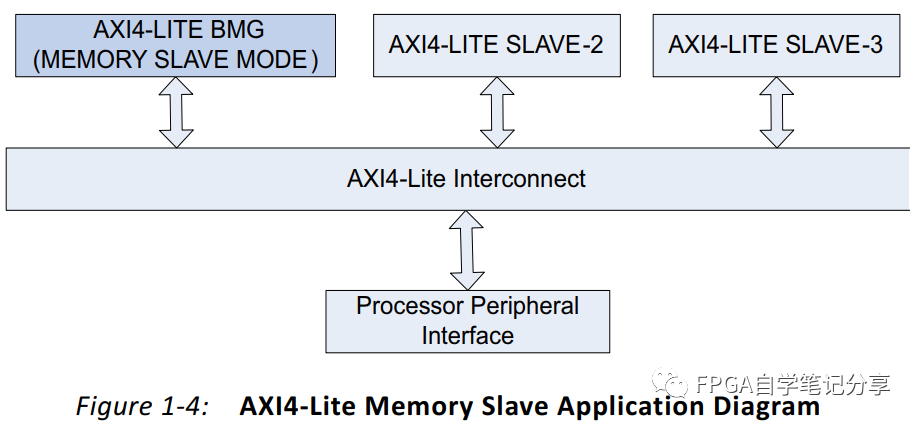

2、AXI4-Lite Block Memories–Memory Slave Mode:内存从属模式下的AXI4-Lite块MEM,如下图所示。

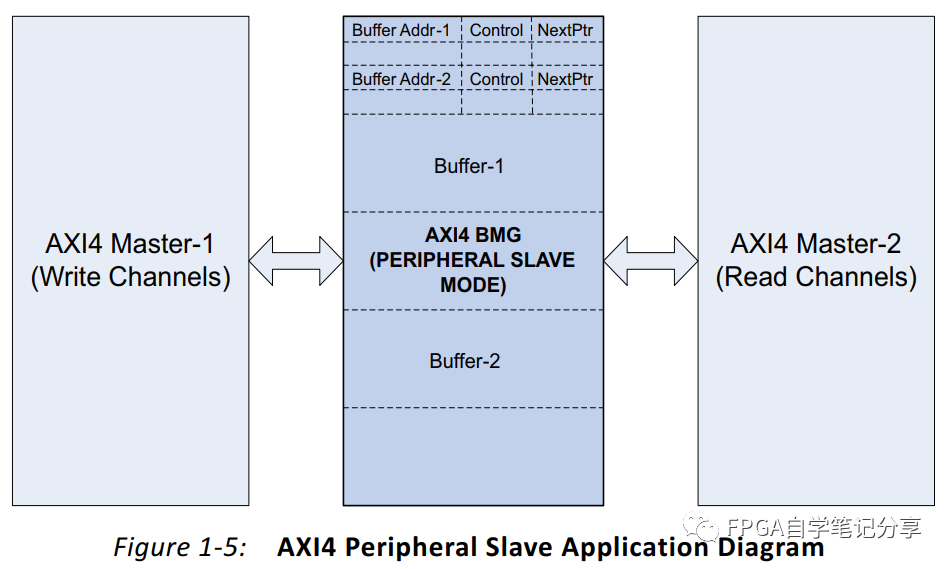

3、AXI4 Block Memories–Peripheral Slave Mode:外设从属模式下的AXI4块MEM,如下图所示。

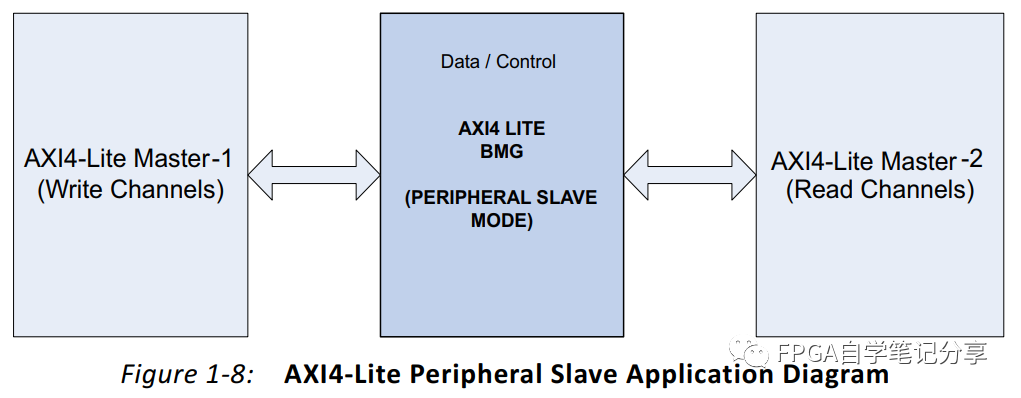

4、AXI4-Lite Block Memories–Peripheral Slave Mode:外设从属模式下的AXI4-Lite块MEM,如下图所示。

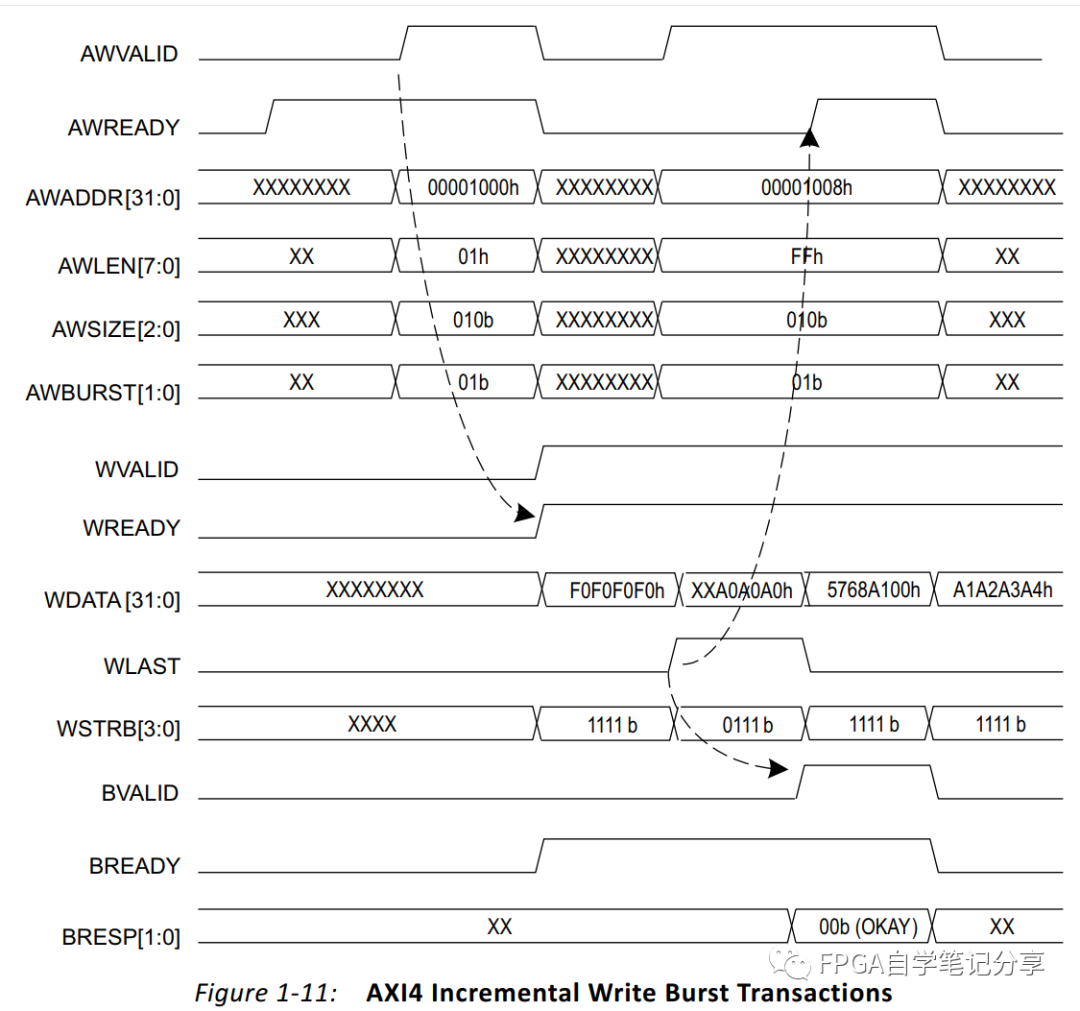

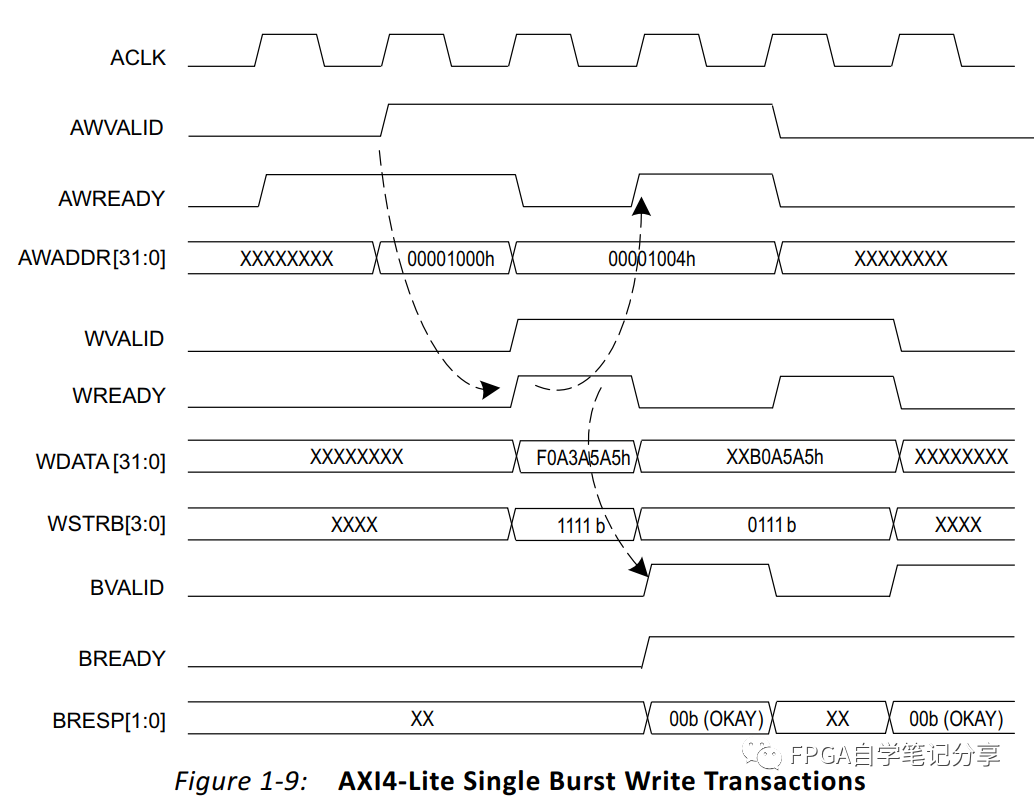

对于AXI4和AXI4-Lite接口的读写,就是标准的AXI4协议,AXI4和AXI4-Lite的写操作如下图所示。整个流程为:主端准备好写地址(AXI4还有AWLEN、AWSIZE、AWSIZE、AWBURST信息)然后拉高AWVALID信号,当AWREADY拉高后表示地址被接受。同时主端准备好写数据并拉高AVALID信号(不用等待从端拉高AWREADY),当WREADY拉高后表示数据被接受。在AXI4模式下,BURST的最后一个输出传输时要拉高WLAST信号。最后从端返回响应信号。详细的依赖关系可参考FPGA IP之AXI4协议3_通道间的依赖关系。

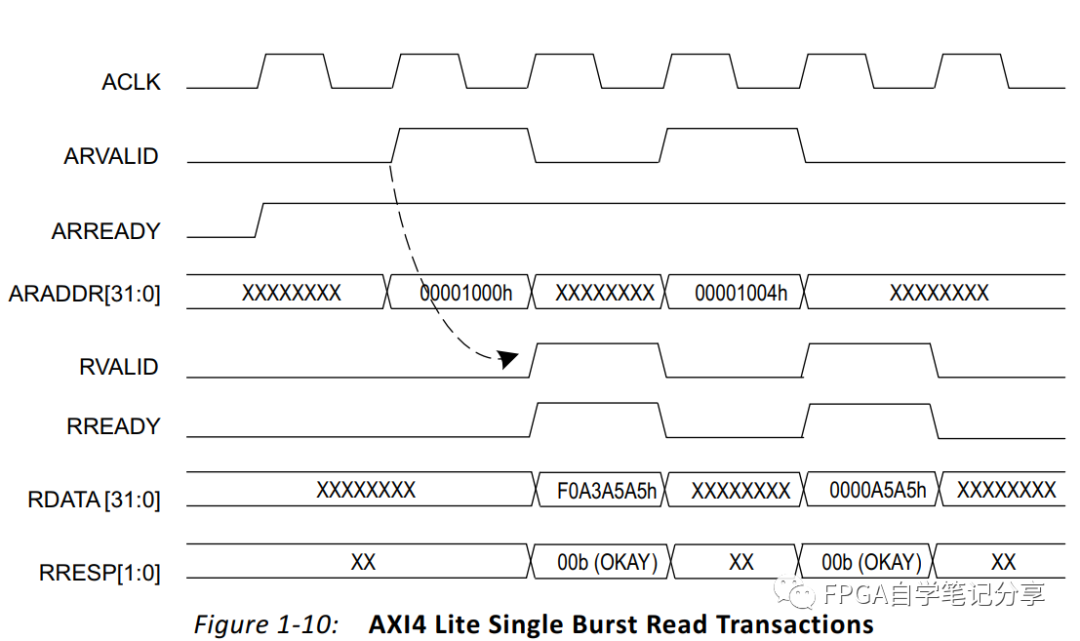

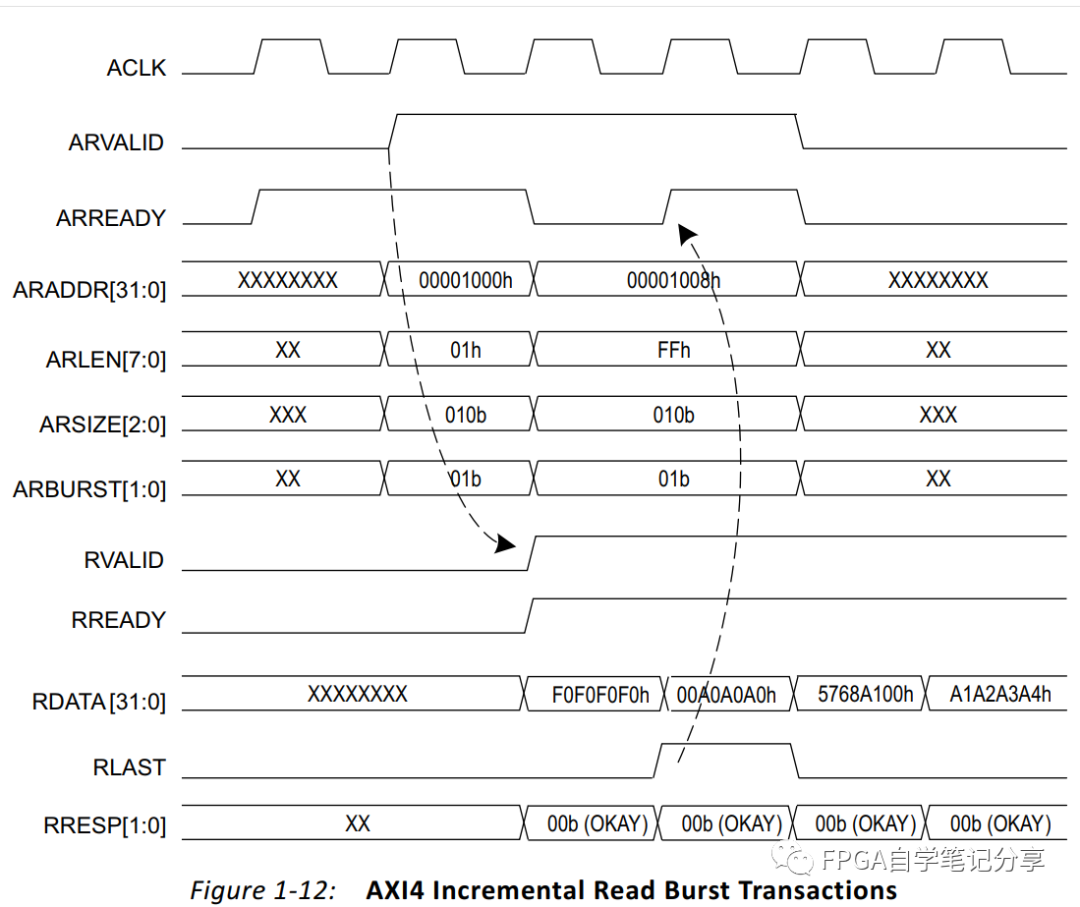

AXI4和AXI4-Lite的读操作如下图所示。整个流程为:主端准备好写地址(AXI4还有ARLEN、ARSIZE、ARBURST信息)然后拉高ARVALID信号,当ARREADY拉高后表示地址被接受。同时从端准备好写数据并拉高RVALID信号,当RREADY拉高后表示数据被接受。在AXI4模式下,BURST的最后一个输出传输时要拉高RLAST信号。最后从端返回响应信号。详细的依赖关系可参考FPGA IP之AXI4协议3_通道间的依赖关系

当然AXI4接口除了支持上图中的Incremental Burst(增量突发)模式外,还支持Wrap Burst、Narrow Transactions 、Unaligned Transactions 模式,这些仅是接口方式的差异,主要是对AXI4协议的支持上,和Block Memory关系不大,这里不再详细描述。

-

XILINX FPGA IP之AXI Traffic Generator2023-11-23 5630

-

Xilinx FPGA IP之Block Memory Generator功能概述2023-11-14 5105

-

XILINX FPGA IP之FIFO Generator例化仿真2023-09-07 3701

-

基于Xilinx FPGA AXI-EMC IP的EMIF通信测试2023-08-31 12683

-

AXI VIP当作master时如何使用2023-07-27 2470

-

XILINX FPGA IP之Clocking Wizard详解2023-06-12 9382

-

FPGA AXI4协议学习笔记(二)2023-05-24 3033

-

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法2022-10-09 5121

-

XILINX MIG(DDR3) IP的AXI接口与APP接口的区别以及优缺点对比2021-11-24 8710

-

Xilinx zynq AXI总线全面解读2020-12-04 9347

-

FPGA程序设计:如何封装AXI_SLAVE接口IP2020-10-30 5388

-

Xilinx FPGA片内ROM实例之ROM配置2019-01-09 4125

-

如何使用Xilinx AXI进行验证和调试2018-11-20 4860

全部0条评论

快来发表一下你的评论吧 !