什么是COP?能为开发者带来哪些优势?如何选择最佳COP器件?

描述

简介

使用可编程逻辑器件进行设计时,最关键的步骤之一就是为应用选择最佳的器件。在 AMD 成本优化产品系列中,有一些专门可供开发者选择的 FPGA 及异构 SoC。即 AMD 成本优化产品系列 Cost-Optimized Portfolio (COP) 目前包含 AMD 7 系列、 UltraScale+ 系列器件、所有 AMD Spartan 7 与 AMD Artix 7 系列以及 Z7020 以下的 AMD Zynq 7000 器件等。在 UltraScale+ 系列中,COP 包含 AMD Artix UltraScale+ 系列以及包含 ZU3T 的 AMD Zynq UltraScale+ 器件。

什么是COP? 能为开发者带来哪些优势

这些器件通常用于各种应用领域,其中包括机器人、医疗、工业、音频、视频、游戏系统、无人机、家庭自动化与联网等。对于开发者而言,COP 具有以下显著优势:

系统集成:可在单个器件内执行多种功能,尤其是在使用异构 SoC 时,在单个器件中集成多种功能可降低材料成本,还可减小产品物理尺寸。

上市时间:集成解决方案的开发时间更短,与基于 ASIC 的解决方案相比FPGA 的灵活性更高。AMD 还为开发者提供了大量开发板和 IP,以加速应用开发。开发板包括 AMD Kria KV260 和 KR260 入门套件、Avnet Ultra96-V2 和 ZUBoard 1CG 等。AMD 论坛、开发者计划以及 MicroZed Chronicles 等社区资源也非常丰富。

现场更新:随着产品规划及标准的发展,FPGA 及异构 SoC 可以在现场进行更新。必要时,还可消除对召回的需求。

低风险解决方案:集成解决方案使电路板的设计更加简单,还有助于降低与电磁干扰 / 兼容性 (EMI/EMC) 相关的风险。

架构灵活性:异构 SoC 及 FPGA 器件为开发者提供了在顺序处理和并行处理之间构建解决方案的能力,既可使用 SoC 中的硬内核,也可使用 FPGA 结构中的软处理器。此外,可编程逻辑还提供了任意接口连接功能。异构 SoC 器件的独特架构使开发者能够通过在可编程逻辑中创建自定义加速器来进一步提高系统性能,如使用 AMD Vivado 高层次综合 (HLS) 卸载 C 算法。

AMD 已经宣布 AMD 7 系列产品系列器件的供货至少会延长至 2035 年,以支持医疗、工业和汽车等许多 COP 应用所需的长期生产运行。COP 中包括一系列广泛的器件,这些器件可提供大量开发者能充分利用的架构特性。FPGA 及 SoC 器件都可分为 7 系列器件和 UltraScale+ 系列器件。7 系列中的 COP 器件包括 AMD Spartan 7 和 Artix 7 系列。AMD Spartan 7 器件可为开发者提供最低的成本、最小的封装以及最高的 I/O 逻辑比。如果需要多千兆位收发器,则 AMD Artix 7 可为开发者提供工作速率高达 6.6Gbps 的收发器。

如果需要在 7 系列范围内进行嵌入式处理,从 Z7007S 到 Z7020 的 AMD Zynq 7000 器件可为开发者提供单核或双核 Arm Cortex-A9 处理器和可编程逻辑。UltraScale+ MPSoC 系列可为开发者提供双核或四核 A53 处理器。

在 UltraScale+ 系列中,COP 包括 AMD Artix UltraScale+ 器件和 UltraScale+ MPSoC 系列中的 ZU1 至 ZU3T 器件,前者带有收发器,能够支持高达 16 Gb/s 的线路速率。

除了可编程逻辑和嵌入式处理器内核外,COP 系列中的 7 系列及 UltraScale+ 器件还包含如下架构特性:

系统监控器 / XADC:一款能够监控内部电压轨和温度的嵌入式 ADC,因此非常适合系统安全和安保实施。

PCIe:通过支持多条通道实现的 PCIe Gen 3 或 Gen 4 端点及根端口实施,可在芯片内外传输高带宽数据。

集成型内存:支持 BlockRAM 与 UltraRAM。BlockRAM 是灵活性极高的专用 36Kb 内存块。每个 BlockRAM 均提供两个读写端口,可以作为一个 36Kb 存储器或两个 18Kb 存储器来实现 UltraRAM 的目的是取代板外存储器,通过高达 14 Mb 的 UltraRAM 存储器实现更好的整体性能。

灵活的 I/O:I/O 支持各种接口,从通过高性能 I/O (HPIO) 实现的高速差分信号,到支持 3v3 标准的高密度和高范围 I/O (HDIO、HRIO),从而更容易与常用设备集成。

安全特性:多级安全功能,从使用 AES 的比特流加密到使用 AES、RSA 和 SHA 的安全启动。COP 中的部分器件还具有密钥管理与滚动功能。

如何选择最佳 COP 器件

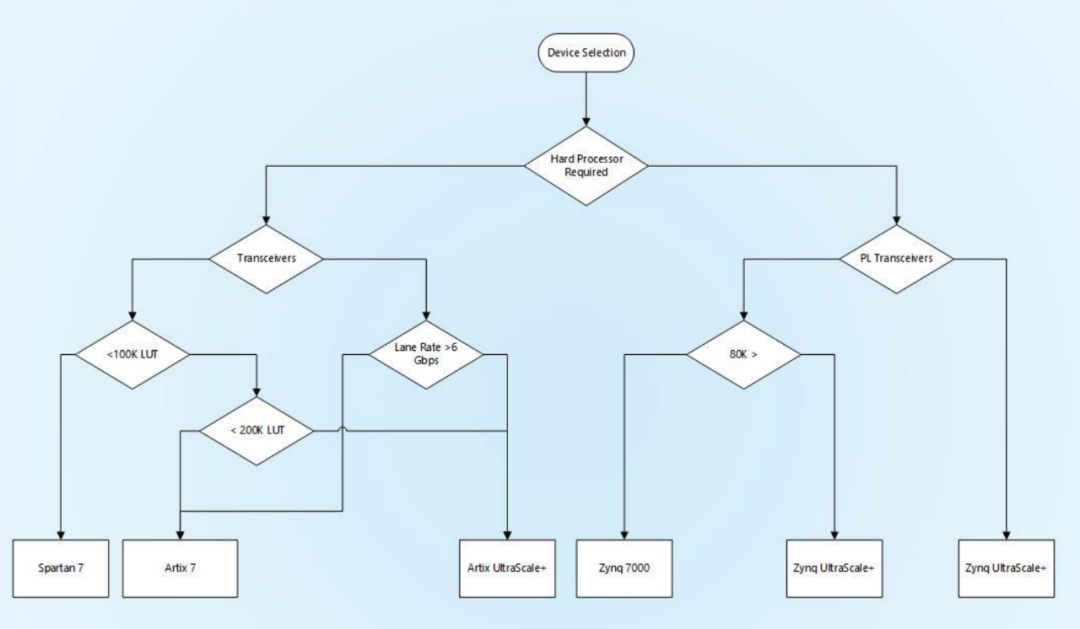

在 COP 器件之间进行选择可能是一项非常艰巨的任务,因此我们可将以下流程图作为指导,以帮助为您的应用选出最适合的器件。

第一个决定因素是:是否需要嵌入式处理器。根据这个问题的答案,我们可以在 AMD Zynq 7000 与 AMD Zynq UltraScale+ 器件或 AMD Spartan 7、AMD Artix 7 和 AMD Artix UltraScale+ 器件之间做出选择。

如果需要嵌入式处理器,我们则需要确定逻辑设计中是否需要 PL 收发器。所有 AMD Zynq 7000 MPSoC 器件都具有 PS GTR 高速收发器,用于实现 USB3.0、SATA 与 DisplayPort 等。如果需要收发器,则应选择 AMD Zynq UltraScale+ ZU3T,因为它提供 PL 收发器。

如果不需要 PL 收发器,则需要根据所需的逻辑资源的大小评估进一步的决策点。如果需要低于 80k 的 LUT,则应考虑 AMD Zynq 7000 系列器件。如所需的逻辑资源超过 80k,则应考虑 AMD Zynq UltraScale+ MPSoC。值得注意的是,在整个项目生命周期中确定逻辑资源大小时,经常会出现范围和需求变化,从而增加逻辑资源。因此,在完成初始尺寸估算时,最好将器件尺寸调整为大约满载的 60%。这既能为设计发展预留空间,又能随着规模的增大降低实施时序闭合问题的风险。

最后一个考虑因素可能是最终应用。大量边缘应用要求外形小巧,以符合尺寸、重量和功耗方面的要求。可编程逻辑器件处于系统的核心位置,因此尺寸受限的应用可从占位尺寸更小的器件中获得巨大优势。幸运的是,AMD Zynq UltraScale+ 和 AMD Artix UltraScale+ 器件采用集成扇出型封装 (InFO),与倒装芯片解决方案相比,该解决方案可减少组件板面积和高度。如果您不熟悉 InFO 封装,简单说它可以去除基板从而减少电路板面积和高度,所选器件的封装也可能是选择标准中的一个重要部分。

图 1. COP 器件选择流程图

如果不需要嵌入式处理,则必须确定是否需要收发器。如果需要,可以考虑 AMD Artix 7 或 Artix UltraScale+ 系列。如果不需要收发器,那么决策点就是价格、逻辑资源与 I/O 逻辑比。开发者通常会选择成本较低的 AMD Spartan 7 器件或逻辑密度较大的 AMD Artix 7 器件。对于逻辑密度较大的器件,可首选 AMD Artix UltraScale+ 系列器件。

案例研究

我们来看几个有关器件选择的简单案例。

1. 第一个案例是一个图像采集器,需要使用收发器以专有标准采集科学图像输出。捕获的图像必须能通过以太网下载,使用 PYNQ 框架。

该案例需要一款嵌入式处理器与下游网络通信还需要 PL 收发器通信来实现千兆位收发器链路。PL 还将执行图像捕获流水线和 DMA,以便向处理器系统提供图像数据。由于该应用使用 PL 收发器和嵌入式处理器,因此 ZU3T 是一个值得考虑的合适器件。

2. 第二个案例研究是 SMPTE UH-SDI 至 PCIe 采集卡。该卡将接收 US-SDI 帧,对其进行缓存并通过 PCIe 进行后续处理。这需要在输入和输出端采用高速收发器,以实现 12Gbps HD-SDI 所需的高数据速率,并支持 PCIe Gen3 x4(每通道 1Gb/s )。本案例中的决定因素是收发器的速度,AMD Artix UltraScale+ 是 COP 系列中唯一支持 16Gb/s 收发器的器件。

3. 最后一个案例是用于分析和测试除颤器生成的波形的医疗测试设备。这种测试设备采用 ADC 捕获除颤器生成的波形,FPGA 会将波形捕获到一个小型外部 SRAM 存储器中。一旦捕捉到波形并进行缓冲后,就会对数据进行处理和分析,以确保波形符合预期。在此本应用中,不需要收发器,而且逻辑尺寸估计小于 100k LUT,并留有余量。其中的主要驱动因素是并行接收和缓存数据。由于不需要嵌入式处理器,也不需要收发器,因此 AMD Spartan 7 FPGA 的逻辑资源指示 < 100k LUT 是开发者考虑的正确起点。

7

总结:

AMD COP 中提供的各种精细粒度器件意味着一种器件可以满足大多数应用需求。从 AMD Spartan 7 FPGA 产品中的最小封装,到 AMD Artix UltraScale+ 器件中带有 16Gb/s 收发器的紧凑型逻辑资源,再到高性能功率优化器件以及 AMD ZU3T 中带有收发器的异构 SoC,成本优化产品系列可为开发者提供了一系列可用于多种应用的器件。

注:所有性能和成本节约声明均由 Adiuvo 提供,未经 AMD 独立验证。性能和成本优势可能会受各种变量影响。本文的结果仅针对 Adiuvo,可能不具有广泛代表性。

审核编辑:刘清

-

探索COP8SA系列8位单片机:特点、性能与应用优势2026-04-19 86

-

探索COP8SG系列8位微控制器:特性、架构与应用解析2026-04-18 510

-

制冷机组cop一般多少 制冷系统cop怎么计算2023-08-17 25944

-

为什么全球都在关注COP262021-11-19 4149

-

全自动洗衣机微电脑芯片COP8780C11电子资料2021-04-09 540

-

Build 2018给你带来哪些全新的开发者体验2020-05-22 1031

-

英特尔升级游戏开发者竞赛:最佳艺术设计和最佳音效2018-11-05 3322

-

新手XGate-COP20快速使用手册 V1.002017-10-09 706

-

XGate-COP20快速使用手册 V1.002017-09-29 804

-

大部分VR开发者,都在用这些平台的硬件2016-08-26 2089

-

各位大神,labview中点云文件(.cop)是怎么生成的?2014-09-14 4340

全部0条评论

快来发表一下你的评论吧 !