DC-DC转换的PCB设计EMI布局方案

电源/新能源

描述

DC-DC转换器可以实现各种电压电平的高效电源转换和供电,但是随着需求的不断上升,需要更高功率密度更高效率以及更小的尺寸,DC-DC转换的PCB设计就更为重要了。

这篇文章主要是从:DC-DC转换组件选择、最小 EMI 布局、热管理方面进行分析。

一、路由注意事项

DC-DC转换器的PCB布线会对电磁干扰水平产生重大影响,正确的 PCB布线技术帮助最大限度地减少EMI。 走线长度和环路面积是DC-DC 转换器(尤其是高频开关转换器)PCB 设计中的关键因素。

1

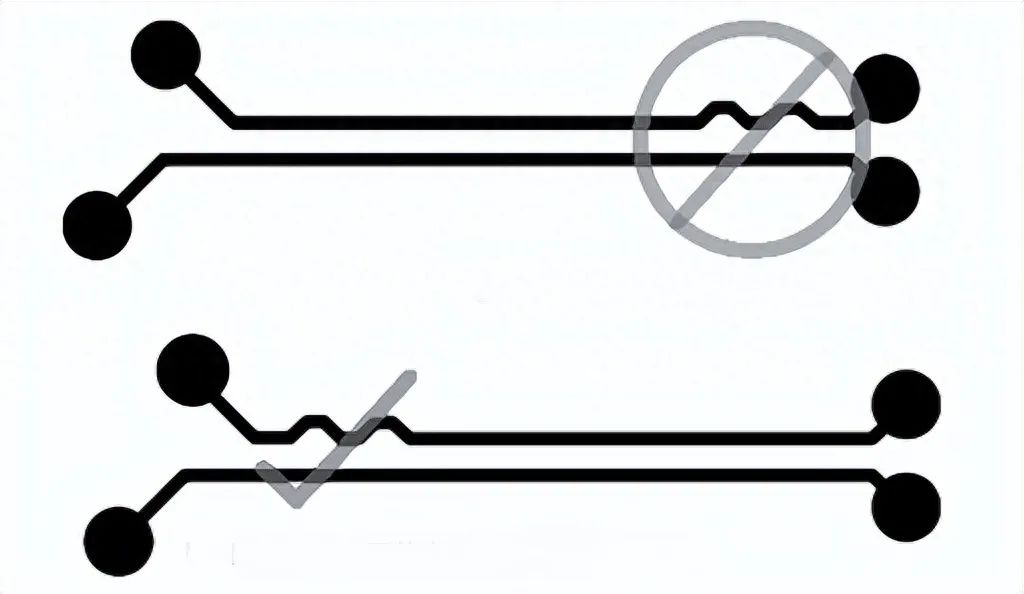

走线长度

在高频转换器中,承载高速开关信号的走线长度对于保持信号完整性和降低EMI至关重要。 较长的走线可以充当天线并辐射电磁能量,可能会对其他组件或电路造成干扰,此外,较长的走线可能会引起延迟、信号反射、寄生效应,从而导致转换器效率和稳定性降低。 因此走线长度应该尽可能短,尤其是对于高速时钟和数据时钟,适当的阻抗匹配技术和受控阻抗走线可u进一步优化信号传输并最大限度地减少信号衰减。 对于高速信号,重要的是差分对的走线长度在整个PCB板上相同,如果不匹配,应该在不匹配的边缘附近制作蛇形走线。

高速 DC-DC 转换器栅极信号的差分对走线匹配

2

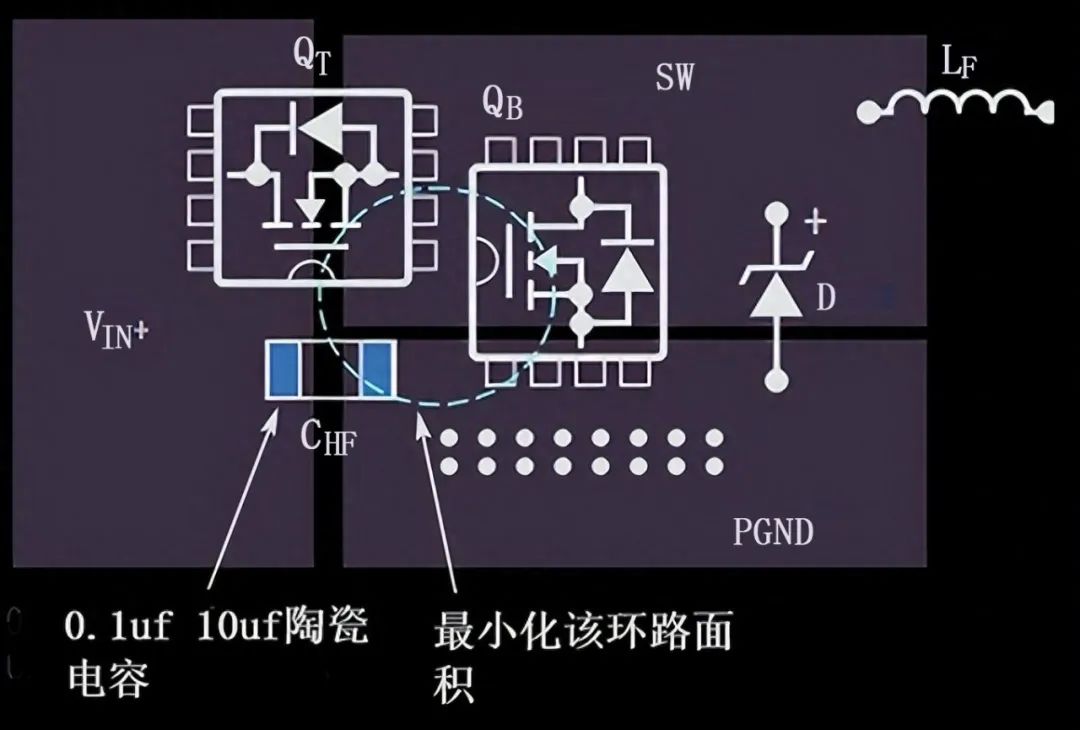

环路区域

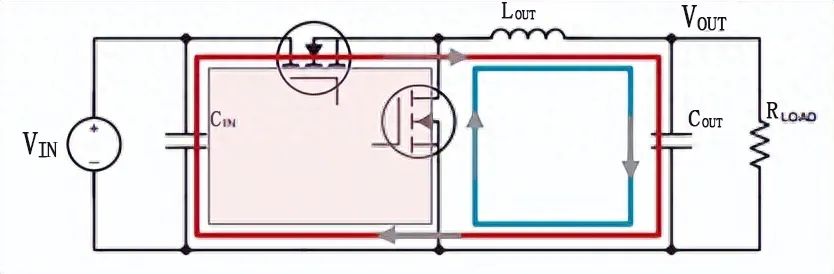

环路区域是指 PCB上的信号走线及其返回路径形成的封闭区域,在DC-DC转换器等高功率和高频电路中,最小化环路面积对于降低辐射 EMI 至关重要。 越大的环路面积会导致更多的磁通量与环路耦合,从而导致更高的 EMI。 最小化环路面积的主要措施是:通过将信号走线放置在靠近其返回路径的位置(例如利用接地层/紧密间隔的电源层)来最小化环路面积。

二、过滤器组件

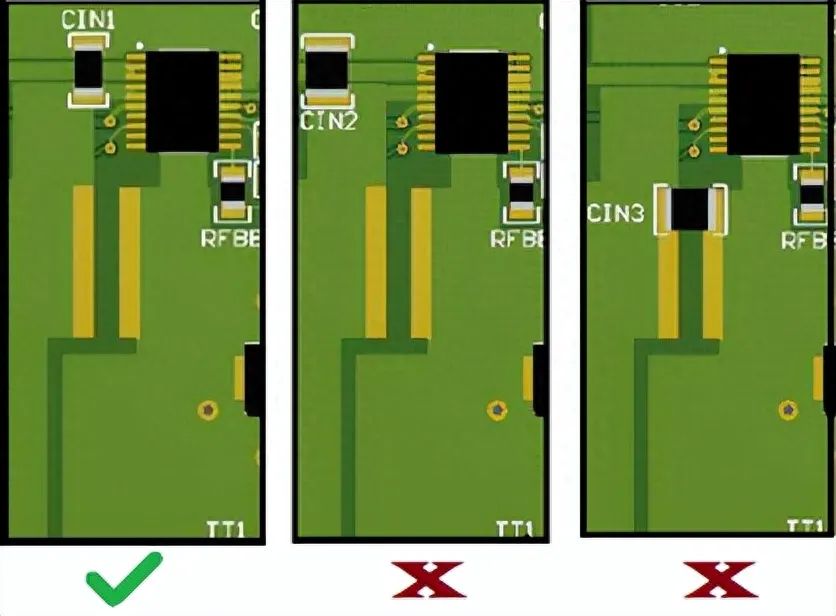

在关键信号和电源线中添加铁氧体磁珠和共模扼流圈等滤波器组件可以减弱传导电磁干扰并防止进一步传播。连接滤波电容时,正确的位置对于滤除 EMI 至关重要。

滤波元器件应该尽可能靠近 DC-DC转换器放置,在 IC 和有源元件的电源引脚附近正确放置去耦电容有助于抑制高频噪声并提高EMI性能。

DC-DC 转换器中去耦电容放置

三、寄生电感和电容

1

路径电感

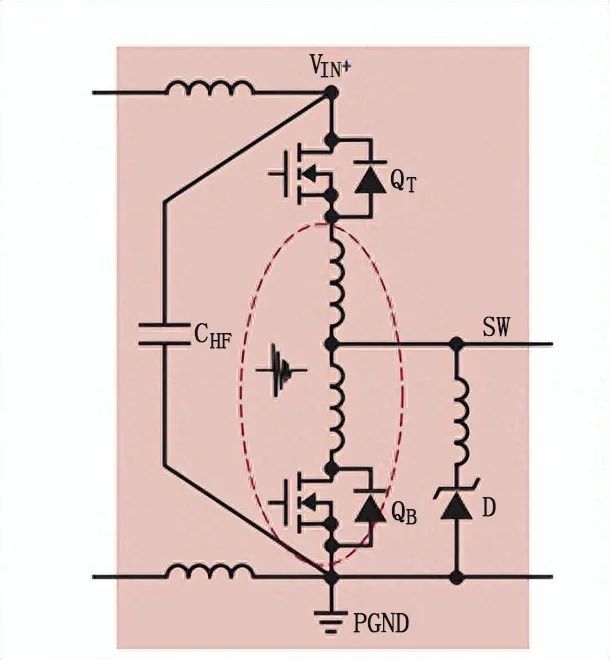

路径电感是导电路径(例如迹线/电线)的固有电感,取决于其物理尺寸和材料特性。在DC-DC 转换器等高频电路中,路径电感会影响转换器的效率和性能。

DC-DC 转换器中高 di/dt 环路产生的路径电感 高路径电感会导致电压下降,开关损耗增加以及转换器效率降低,还有可能导致电路中的电压过冲和振铃,影响信号完整性。 为了最大限度地减少路径电感,PCB工程师可以使用更宽的走线,更短的路径,或者利用专用的接地层/电源层为高电流/开关信号创建低电感返回路径。

利用接地层并最大限度低减少di/dt 环路

2

杂散电容

在高频电路中,杂散电容会与高速信号耦合,导致不必要的电容耦合并增加EMI,还可能会导致信号失真和退化。 为了最大限度低减少杂散电容,应该在信号走线、接地层、电源层之间保持适当的间距,适当的接地分段和隔离也有助于减少寄生电容。

四、DC-DC 转换器接地环路的影响

在设计DC-DC转换器时,PCB工程师必须要考虑电流环路并正确放置组件,这样可以让环路在物理上金科能小。

DC-DC 转换器中的电流环路

1

接地环路过长的影响

由于接地环路过长会导致以下问题:

电磁干扰:接地环路可以充当天线,导致 EMI 辐射到周围环境中。

噪声和信号衰减:流经接地环路的电流会在不同接地点之间产生电压差,可能会导致不需要的噪声被引入敏感信号路径,从而导致信号衰减和信噪比降低。

共模噪声:接地环路可能导致共模噪声耦合到敏感的模拟或数字电路中。这种噪声会破坏信号精度,尤其是在低电平模拟测量或高速数字通信中。

寄生接地电流:循环电流可以在不同接地点之间流动,从而导致寄生接地电流。寄生电流会产生电压降并影响转换器的性能,从而导致效率低下和潜在的热问题。

接地反弹:接地环路可能会导致接地参考平面之间存在电压差,从而导致接地反弹。接地反弹是指开关事件期间接地电压的瞬态增加,这可能会破坏信号完整性并影响数字电路的正常运行。

2

接地环路缓解措施

星形接地:将所有接地点汇聚到一个参考点,有助于消除接地环路并减少出现接地相关问题的可能性。

地平面:在 PCB 上使用坚固的接地层可确保电流的低阻抗返回路径,从而降低接地环路的风险。

地面分割:对不同功能块或组件的接地层进行适当的分割可以防止接地电流相互干扰。

将模拟地和数字地隔离:在物理上分离模拟和数字接地层可以防止敏感模拟电路和噪声数字电路之间的干扰。

跟踪路由:确保承载高电流或高频信号的走线具有低电感返回路径(例如,使用短而宽的走线或接地过孔)有助于最大限度地减少接地环路的可能性。

五、层堆叠

层堆叠指构成 PCB 的不同导电层和介电层的排列和配置,在确定电路板的性能、功能、可制造方面非常重要,下面就来分析一下层堆叠的重要性:

1

信号完整性和 EMI 控制

通过仔细选择信号层和接地层/电源层的布置,工程师可以确保高速信号的受控阻抗、减少串扰并提高抗噪能力。

2

接地和配电

层堆叠可以将接地层和电源层在整个 PCB 中恰当分布,接地层为信号提供低阻抗返回路径,最大限度地减少接地反弹和噪声。 充足的电源分配可确保高效供电,从而减少电压降和功率损耗。

3

热管理

层堆叠会影响 PCB 的热性能。 通过为电源和接地层分配专用铜层并仔细放置散热通孔,工程师可以有效地散发电源组件产生的热量并确保适当的热管理。

4

可制造性和组装

正确的层布置、钻孔对齐以及明确的堆叠规格可以实现顺利的制造和组装,从而降低生产过程中出现缺陷和错误的风险。

5

多层设计和小型化

通过层堆叠工程师可以设计紧凑和小型化的 PCB。

6

EMC 合规性

层堆叠有助于管理信号返回路径、最小化环路面积并降低 EMI ,从而有助于 PCB 符合EMC 法规。

7

信号路由和分区

层堆叠有助于 PCB 上不同功能块之间的有效信号路由和分区。通过将敏感的模拟、数字、电源电路隔离在不同的层上,工程师可以增强信号隔离并减少干扰。

六、DC-DC转换器 PCB的走线尺寸调整

走线宽度需要仔细考虑,走线宽度直接影响 PCB 的载流能力、功率损耗和热性能,下面是确定 PCB 走线宽度的关键因素:

1

载流量

确定 DC-DC 转换器电路中每条走线将承载的最大电流,包括流经 MOS 管、电感和电容等功率组件以及高电流信号走线的电流,最大电流应考虑瞬态尖峰和潜在的过流情况。

2

温升及允许温度

使用以下公式根据最大电流和走线宽度计算走线的温升: ΔT = (I^2 * R_trace) / (k * A)

ΔT 是温升

I 是电流

R_trace 是走线电阻

A 是走线的横截面积

k 是 PCB 材料的热常数

3

走线电阻

使用以下公式计算走线电阻:R_trace = ρ * (L / A) ρ是走线材料(铜)的电阻率 L是走线的长度 A是走线的横截面积(宽度*厚度)

4

电压降

根据设计要求中指定的最大电流和允许电压降,计算走线上可接受的电压降。

5

铜的重量和厚度

确定 PCB 的铜重量和厚度。标准铜重量包括 1 盎司(35 µm)、2 盎司(70 µm)和 3 盎司(105 µm)。

较厚的铜可实现更高的载流能力,但会增加 PCB 成本和可制造性方面的考虑。

6

走线宽度计算

使用计算出的电流、走线电阻和电压降值,使用在线走线宽度计算器或考虑 PCB 铜厚度和材料的 PCB 设计软件来计算所需的走线宽度。

7

尺寸空间限制

确保确定的走线宽度适合可用区域,且不违反间隙和间距要求。

8

散热

确保计算出的走线宽度和铜重量能够实现高效散热,并且不会导致温升过高,尤其是对于高电流走线。

编辑:黄飞

-

关于PCB设计和降低DC-DC转换器EMI的解决方案(二)2021-03-15 9457

-

半桥DC-DC转换器PCB设计指南2023-06-05 1871

-

DC-DC 的 PCB布局设计小技巧2025-03-11 7249

-

DC-DC经典PCB布局2013-09-09 1903

-

DC-DC降压转换器电路布局与设计和实践2019-07-11 13571

-

低EMI DC/DC变换器的PCB设计2020-02-04 5332

-

PCB设计的高度集成DC-DC转换器优化方案2021-02-03 3873

-

DC-DC中PCB设计的layout2021-09-13 8471

-

DC-DC的PCB设计2022-09-06 1820

-

DC/DC转换器的基板布局-DC/DC转换器的PCB板布局概述2023-02-23 2605

-

DC-DC降压转换器PCB布局的技巧2023-06-19 3256

-

DC-DC转换器PCB设计的一些要点2023-10-23 1933

-

DC-DC的PCB设计注意的点2024-01-17 1308

-

DC电源模块的 PCB设计和布局指南2024-03-05 3107

-

通过布局提高DC-DC转换的效率2024-09-26 416

全部0条评论

快来发表一下你的评论吧 !