降压DCDC有输入输出电压差吗

描述

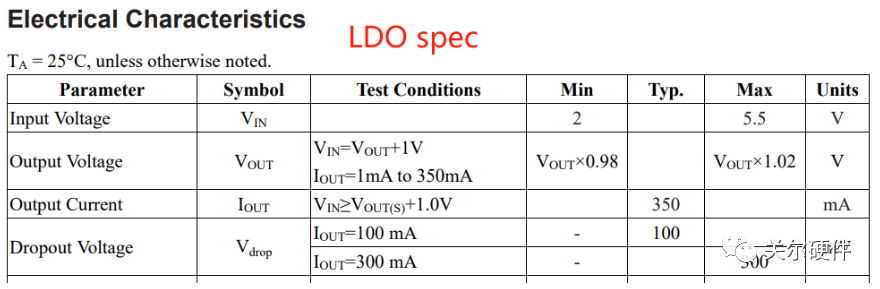

在LDO specfication里面,有Dropout Voltage(输入输出电压差)的参数。如下图,输出电流100mA时,典型压差是100mV;输出电流是300mA时,MAX压差是300mV(线路阻抗不变下,流过电流越大,压降也就越大。二极管的压降也是电流越大,压降越大。)。

降压DCDC是否也有输入输出电压差尼?答案是肯定的。

1、100% Duty cycle的DCDC

DCDC TMI3408F上管PMOS(Vgs电压为负时导通,不需要BOOST电容),下管NMOS。因为上管PMOS的S端为高(等于输入端电源),G端为低时,就导通。也就是说,该DCDC可以实现100% Duty cycle,输入输出的压差就是输出电流乘以上管PMOS的阻值,及BUCK电路电感内阻的压差,该输入输出的压差就比较小。(note:TMI3408F是低压输入,输入电压范围2.5V~5.5V。)

2、Maximum Duty Cycle的DCDC

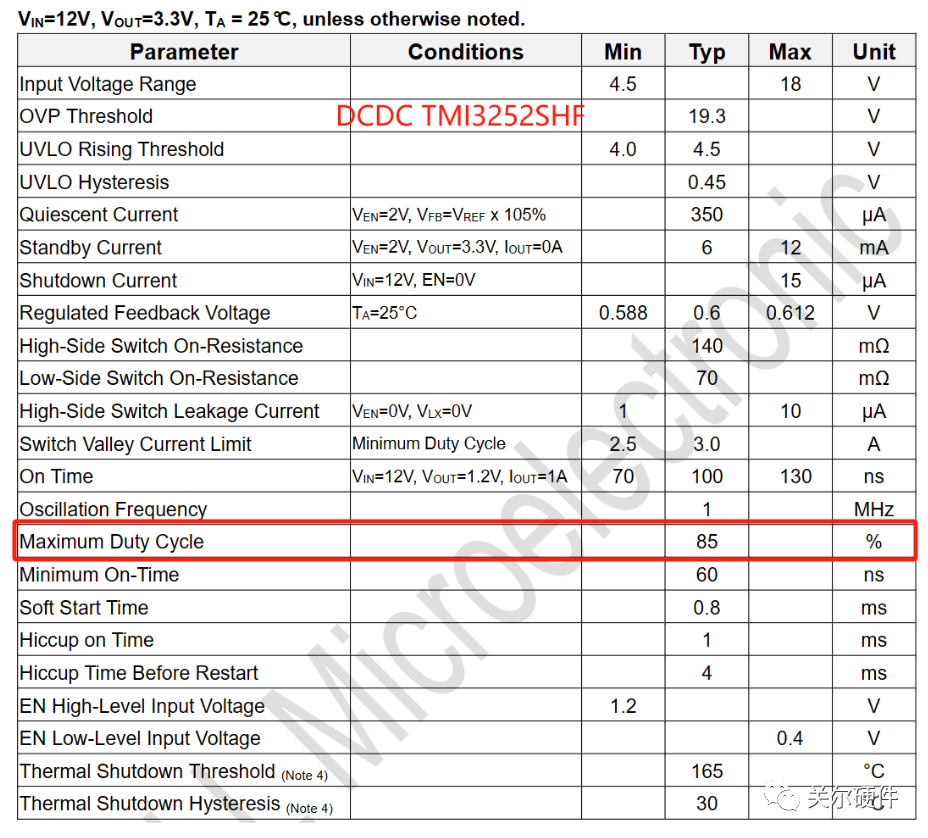

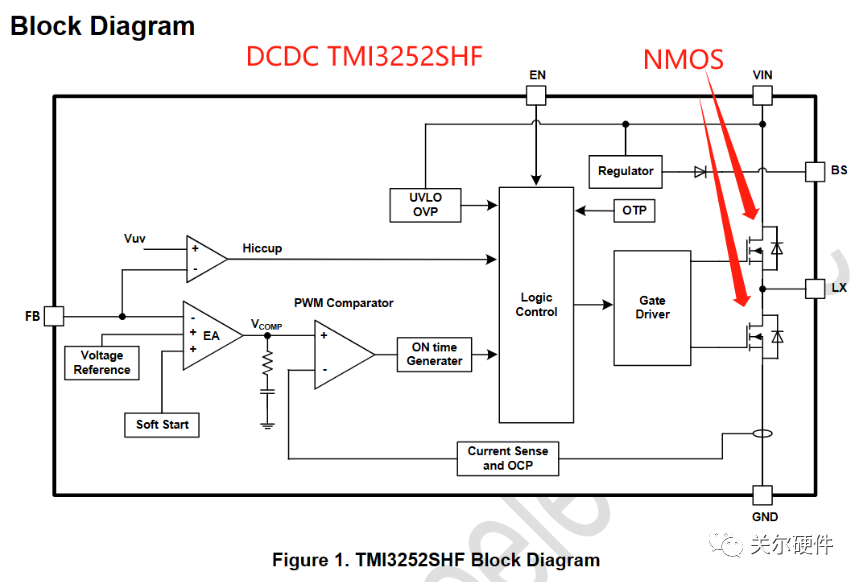

TMI3252SHF的上下管都是NMOS管,Vgs电压为正时导通,即上管NMOS的S端为正,G端也要为正,且比S端还要高,因此电路需要BOOST电容。由于BOOST电容的充放电,及Vgs的电压要大于某阈值,上管NMOS才会导通。当Vgs小于阈值时,上管NMOS就会关闭,就没办法达到100% Duty cycle。因此,该DCDC就会有Maximum Duty Cycle的参数,如TMI3252SHF的maximum duty cycle是85%,即输出电压的最大值只能是输入电压的85%,还需要减去PMOS的压降(电流乘以上管PMOS的Rds(on))。(note:TMI3252SHF是高压输入,输入电压范围4.5V~18V。)

小结,DCDC芯片有个Boost管脚的芯片,无法做到100% DutyCycle,因为有CBoost电容(电容放电时,导致Vgs电压低于mos管导通阈值)。DCDC芯片上管使用PMOS时,可以做到100% Duty Cycle。

-

线性稳压器IC的输入输出电容设计和纹波对策2025-05-24 1699

-

DCDC基础:输入输出电容的选择及计算2023-04-06 22169

-

运放参数解析:输入输出电压范围2023-10-01 13621

-

LDO输入输出电压差2011-06-16 12603

-

输入输出电压差2015-05-08 4423

-

7533和78L05这种LDO输入输出电压的压差有没有限制2020-12-31 6432

-

DCDC与LDO的特点与区别2021-02-24 5520

-

DC-DC降压芯片有输入输出压差范围吗2022-01-11 1672

-

运算放大器输入和输出共模与差分电压范围2013-09-26 1475

-

介绍作为表示线性调整器基本性能之一的输入输出电压差2018-05-29 6917

-

DC-DC降压芯片是否有输入输出压差范围要求?2021-11-09 1382

-

小白讲解单片机GPIO输入输出2021-12-17 1024

-

DC-DC降压芯片的输入输出压差范围的要求2023-02-17 10504

-

DCDC直流降压型电压变换原理详解2023-04-18 7373

-

输入输出电压差与效率的关系2024-01-05 1865

全部0条评论

快来发表一下你的评论吧 !