PCIe在AI加速器中的作用

描述

从线上购物时的“猜你喜欢”、到高等级自动驾驶汽车上的实时交通信息接收,再到在线视频游戏,所有的这些都离不开人工智能(AI)加速器。AI加速器是一种高性能的并行计算设备,旨在高效处理神经网络等AI工作负载并提供近乎实时的处理方案,从而实现一系列应用。

为了让AI加速器有效地完成自己的工作,数据必须要以极快的速度在AI加速器(作为设备)与CPU和GPU(主机)之间进行快速且低延时的移动,而实现这一切的关键就在于PCI Express(PCIe)高速接口。

PCIe大约每三年更新换代一次,带宽也会随之翻倍,而这正是我们数据驱动的数字世界所需要的。作为PCIe规范的最新版本,PCIe 6.0可提供:

每个引脚64 GT/s的数据传输速率

一种新的低功耗状态,从而实现更低的功耗

经济高效的性能

高性能的完整性和数据加密(IDE)

向后兼容前几代

尽管PCIe过去可能通过PC上的插槽,连接显卡和扫描仪等外围设备,但得益于带宽的不断增加,PCIe的作用现在已远不止于此。本文将详细介绍PCIe如何满足AI加速器的日益增长的要求。

AI无处不在,PCIe也是如此

GlobalData的数据表明,AI正在芯片组领域中迅速普及,预计到2030年,超过40%的芯片组中都将包含AI硬件。人工智能(AI)和机器学习(ML)工作负载的复杂性仍在不断增加。事实上,AI和ML训练模型的规模大约每隔几个月就会翻一番。为了确保有效性,AI系统必须能在不牺牲性能或增加延迟的情况下,通过AI开发管道移动大型数据集。不妨看一看下面这些带宽密集型工作负载示例:

4K和8K高清视频 — 需要更多计算能力和内存

高分辨率和高动态范围 — 实现机器视觉和实时感知

多摄像头阵列和4D传感 — 实现深度和运动推理

所有这些趋势都表明,AI加速器的关键在于提供强大的并行计算能力,让语音激活和高等级自动驾驶汽车等应用能够做出近乎实时的响应。这些高性能机器既可以采用超大芯片的形式,例如用于深度学习系统的Cerebras晶圆级引擎(WSE);也可以是GPU、大规模多核标量处理器或空间加速器,通过将数十到数百个芯片组合到一起,打造出具有数百petaFLOPS处理能力的大型系统,用以处理大型神经网络。

PCIe发挥着高效的桥梁作用

由于能够处理AI和ML工作负载,AI加速器可以增强数据中心服务器中CPU的处理能力,而PCIe则充当两者之间的桥梁。就其作用而言,PCIe具有以下优势:

最大限度提高芯片到芯片接口的带宽,无论是用于大规模计算阵列中的AI加速器,还是边缘的AI加速器

提供扩展容量,以便在多个主机和多台设备之间移动数据,因为PCIe插槽可以支持各种类型的扩展卡,包括AI加速器

支持通过多线程技术跨多个芯片并行处理工作负载

实现主机和设备之间的通用互操作性,使得能够在系统运行时无缝添加或移除AI加速器卡

提供低功耗PCIe 6.0 L0p模式,能够以更少的通道支持所需的数据流量,从而可以降低功耗,帮助最大限度地减少碳足迹

提供数据保密性、完整性和重发保护功能,确保传输中的数据免受嗅探、篡改、删除、插入或重发数据包攻击

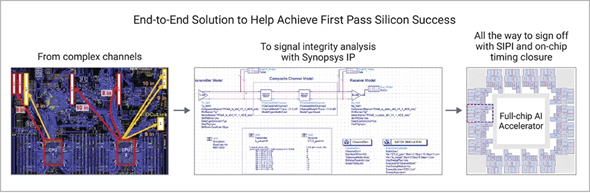

要充分利用这种安全的高速接口,经验证的PCIe物理层(PHY)和具有IDE安全性的控制器IP是关键,而相关的专业知识也对帮助开展相应设计至关重要。功耗和信号完整性方面的考量则突显了专家支持的重要作用。AI加速通常需要许多高速通道。PCIe的多个通道同时切换会产生大量功耗,这使得电源完整性成为一个问题。如果在同时切换过程中出现IR压降等问题,则不利于充分发挥全部性能。信号完整性也很重要,因为系统中在AI加速器和CPU之间传输的信号必须完好无损。新思科技内部拥有功耗和信号完整性方面的专家,他们能够模拟多通道环境,指导开发者在设计芯片时将支持PCIe的PHY放置在合适位置,从而实现最佳性能。

新思科技是PCIe IP和PCIe协议验证解决方案(包括验证IP)的行业领导者,新思科技的PCIe专家也是PCI-SIG联盟(负责编写PCIe总线规范)的主要贡献者。新思科技的PCIe产品组合,以及各种具有向后兼容性的组件,包括:

新思科技PHY IP,通过自适应数字信号处理(DSP)算法来优化数字均衡,以跨底板、网络接口卡(NIC)及芯片到芯片通道实现高能效

新思科技控制器IP,具有与新思科技IDE安全IP模块紧密集成的架构,其中包含多个接口,旨在尽可能降低延迟并提高吞吐量

新思科技验证IP,可加速测试平台开发,并且具有内置验证计划、验证序列和功能覆盖范围

用于新思科技ZeBu硬件加速系统和新思科技HAPS原型系统的新思科技协议接口卡、在线和虚拟解决方案,可实现软件驱动的系统验证、性能分析、认证和流片前合规性测试

除了端到端PCIe IP解决方案,新思科技的IP核组合还包括内存、处理器及其他用于AI加速器的接口IP。全栈式AI驱动型电子设计自动化(EDA)套件Synopsys.ai现已搭载能够显著加快专用AI加速器设计的功能。在验证方面,AI SoC需要更快的流片前硬件辅助验证解决方案。新思科技的ZeBu Server 5和HAPS系统提供了超快且容量超大的硬件辅助验证(HAV)系统,有助于完成各种复杂SoC设计的所有系统级验证用例。

PCIe接下来的发展方向如何?

下一代PCIe有望达到速度惊人的2.048TB。随着越来越多的设备和系统融入AI,任何能够满足AI速度需求的创新都是利好消息。对于现今和未来的AI加速器来说,不断发展的PCIe高速接口有望与之携手共进,让日常生活变得更加智能。

审核编辑:汤梓红

-

#硬声创作季 电子制作:磁性加速器Mr_haohao 2022-10-19

-

关于长整加速器的工作步骤:2018-03-17 3382

-

请问66ak系列芯片加密加速器的调用?在程序设计中如何调用此加速器?2018-06-19 4061

-

PCIe的SmartNIC如何改变方案加速规则2021-01-07 1911

-

使用AMD-Xilinx FPGA设计一个AI加速器通道2023-02-21 1447

-

【书籍评测活动NO.18】 AI加速器架构设计与实现2023-07-28 37395

-

《 AI加速器架构设计与实现》+第2章的阅读概括2023-09-17 3956

-

实时频谱分析仪(RSA)在加速器中的应用2009-10-17 764

-

快速晶闸管在加速器电源系统中的应用2009-07-08 844

-

什么是AI加速器 如何确需要AI加速器2022-02-06 6064

-

AI和数据中心:PCIe 6.0,你是懂加速的2023-07-12 8297

-

粒子加速器的加速原理是啥呢?2023-12-18 4897

-

家居智能化,推动AI加速器的发展2024-02-23 6019

-

Hitek Systems开发基于PCIe的高性能加速器以满足行业需求2024-03-22 1557

-

边缘计算中的AI加速器类型与应用2025-11-06 969

全部0条评论

快来发表一下你的评论吧 !