物理约束实践:I/O约束

描述

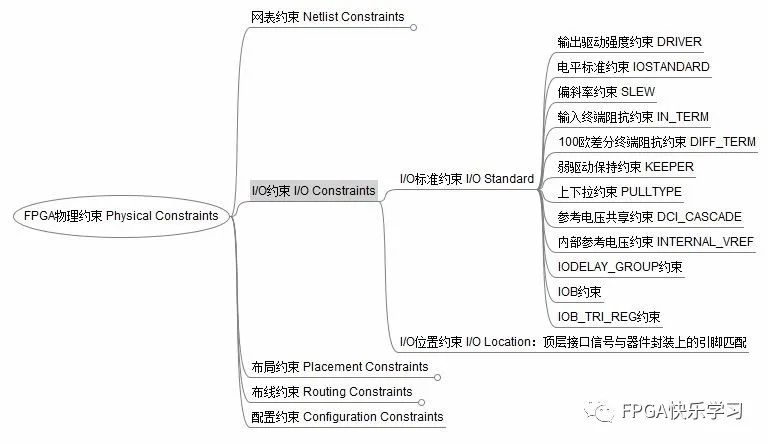

I/O约束(I/O Constraints)包括I/O标准(I/OStandard)约束和I/O位置(I/O location)约束。

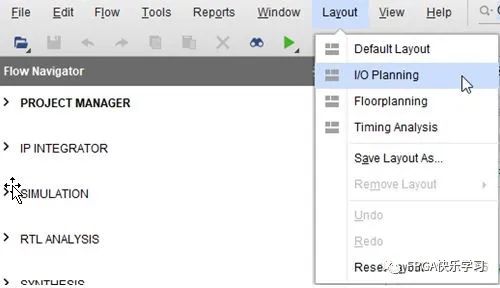

以Xilinx Vivado开发工具为例,点击OpenImplemented Design,打开实现设计(Implemented Design)页面。接着如图1所示,在菜单上点击Layout-> I/O Planning,打开I/O约束页面。

图1 I/OPlanning菜单

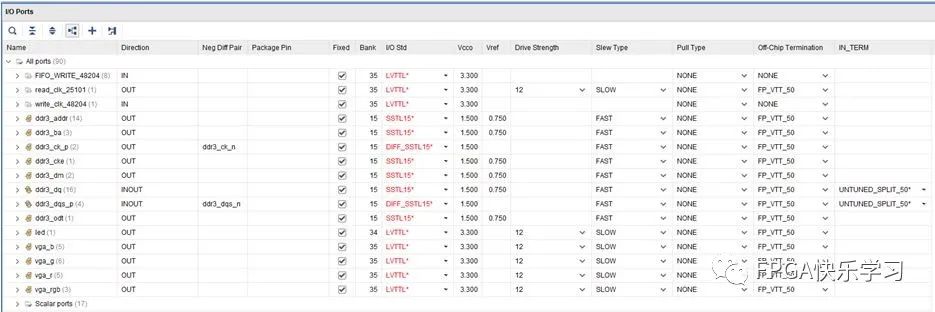

I/O约束页面如图2所示,在该页面中,Allports一列中按照总线的方式进行分类,可以进一步展开看到每一个具体的I/O引脚的约束信息。这里的I/O标准约束包括了电平标准(I/O Std)、输出驱动强度(Drive Strength)、上下拉类型(Pull Type)、偏斜率类型(Slow Type)、输入终端阻抗(IN_TERM)等。由于I/O标准和FPGA外部所连接的外设芯片息息相关,每个外设芯片所对应的I/O标准不同,在FPGA中的约束设置也有所不同。

图2 I/O约束页面

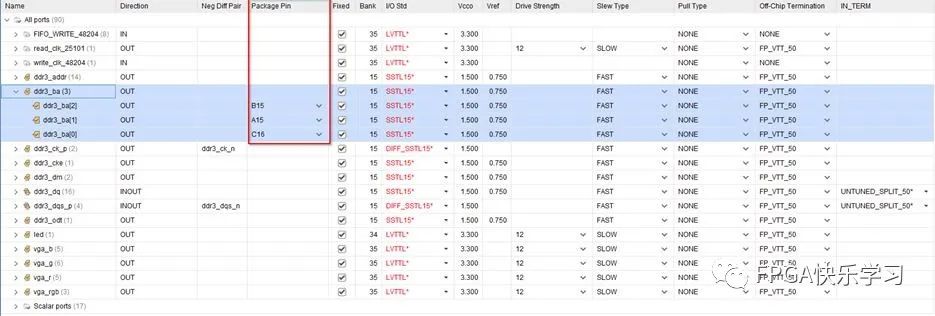

如图3所示,展开一组名为ddr3_ba的总线,其下的3个I/O引脚详细的约束信息都一目了然。Package Pin一列即I/O的位置约束信息,通常对应着一些字母和数字组合的位置代号,如图示的B15、A15、C16,即FPGA器件封装上对应着的具体的物理引脚的代号。通过这样的位置约束,就将FPGA顶层模块代码中的I/O信号和器件封装上的引脚映射在一起了。

图3 I/O位置约束

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA I/O口时序约束讲解2023-08-14 3262

-

请问物理约束文件ADC可做哪些约束?2023-08-11 594

-

约束、时序分析的概念2023-05-29 1821

-

XDC约束技巧之I/O篇(下)2023-04-10 2645

-

XDC约束技巧之I/O篇(上)2023-04-06 2822

-

物理约束实践:网表约束DONT_TOUCH2022-11-12 5053

-

Xilinx FPGA管脚物理约束介绍2022-07-25 6184

-

简述Xilinx FPGA管脚物理约束解析2021-04-27 6490

-

如何约束内部生成的i2s o时钟?2019-04-12 1651

-

XDC约束及物理约束的介绍2019-01-07 7417

-

物理约束之布局约束2018-09-26 3384

-

物理约束之IO约束2018-09-21 2677

-

FPGA设计约束技巧之XDC约束之I/O篇 (上)2017-11-17 13737

-

Adam Taylor玩转MicroZed系列74:物理约束2017-02-08 519

全部0条评论

快来发表一下你的评论吧 !