一种用于LVTSCR器件SPICE仿真的简单的宏模型等效电路建模方法。

描述

SCR在CMOS技术的ESD保护中发挥着越来越重要的作用。一个主要的挑战是为这些器件在ESD应力条件下开发有效的紧凑仿真模型。

前言

本文介绍一种用于LVTSCR器件SPICE仿真的简单的宏模型等效电路建模方法。

LVTSCR介绍

随着先进技术中器件特征尺寸的不断减小,集成电路越来越容易受到静电放电(ESD)的影响。可控硅整流器(SCR)通常用于为高频引脚提供防ESD损坏的片内保护。与其他ESD器件相比,SCR占用更小的面积,具有更低的寄生电容。在CMOS技术中,通常在可控硅结构中引入MOS触发器件以降低其固有损耗可控硅回吸触发电压。这种器件称为低压触发可控硅(LVTSCR),具有比标准SCR更低的snapback触发电压。

实现LVTSCR建模的主要障碍是雪崩电流,雪崩电流是偏压条件的复杂函数。尺寸缩小带来的问题,隧穿电流变得重要。模型需要包含对非常快的瞬态激励的响应,如CDM,因为它是ESD的主要失效模式。

一种新的宏观建模方法用于模拟MOS器件中的snapback已经被报道。该模型采用标准元素构造,没有显式雪崩电流源。它利用了现有的先进的SPICE模型,提供了极大的简单性,高灵活性,合理的准确性和广泛的可用性。该方法还有一个优点,即它与大多数商业模拟器兼容。

LVTSCR中的Snapback

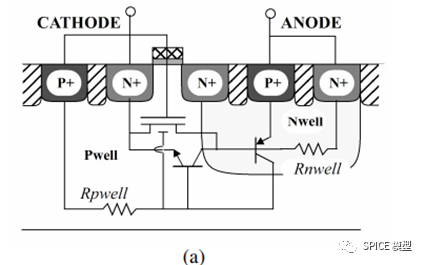

LVTSCR结构示意图

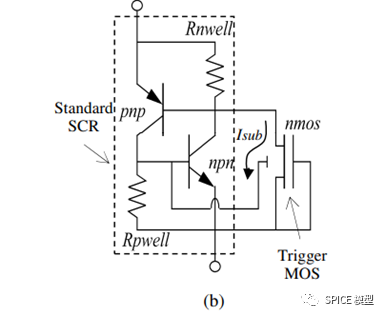

LVTSCR宏模型等效电路示意图

LVTSCR器件的snaback物理特性:

结构可以看做一系列的PNPN扩散结,可以理解为一个PNP和一个NPN相连。添加MOS作为触发器件,实现低snaback触发电压。Nwell,Pwell电阻被考虑。

原理:

LVTSCR中的snaback是由于NMOS衬底电流触发的正反馈,主要是由NMOS Drain/Bulk 结或NPN和PNP的Base/Collector 结雪崩击穿引起的。当正电压施加到anode时,结是反向偏置的。当结电压达到其击穿电压时,由于碰撞电离,许多空穴和电子对在耗尽层中产生。当产生的电子移动到漏极或集电极时,空穴被注入到NMOS的Pwell或Bulk。电子空穴流形成了NMOS器件的衬底电流Isub,即从漏极流向NMOS器件的衬底,或从NPN的集电极流向基极。在晶体管外部,Isub通过Rpwell电阻从NPN的基极流向发射极(从NMOS的Bulk到源极)。当Rpwell电阻上的压降大于NPN的导通电压(-0.7V)时,NPN导通。这导致额外的电子电流到达Drain/Bulk (Base/Collector)结耗尽区,并进一步增加产生的电子-空穴对。最终,NPN和PNP都被打开,阳极和阴极之间的电压下降并保持在一个降低的水平。

LVTSCR器件的snaback建模的关键效果

Snapback之前,当NMOS占主导地位时,Drain/Bulk结起作用,isub是Vgs,Vds的函数。发生Snapback后,碰撞电离电流与Vgs的关系变得微弱。PNP, NPN占主导作用。这里介绍一种宏模型建模方法,使用标准的MOSFET, BJT模型。雪崩效应,dv/dt效应,GIDL效应和电容本质上包含在MOS和BJT模型中。BJT Mextram模型中包含了模拟雪崩击穿效应的方程,所以可以先用BJT Mextram简单验证一下SCR的Snapback行为。

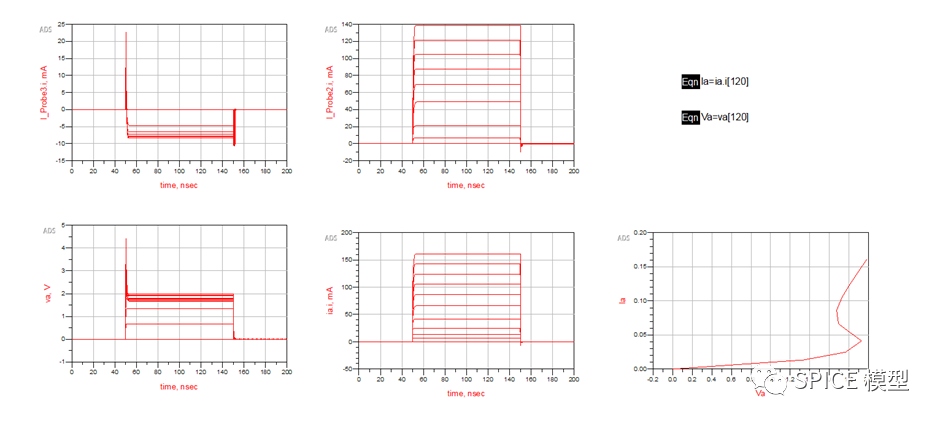

ADS中验证电路

仿真结果

审核编辑:刘清

-

微变等效电路用于分析什么2024-08-16 3522

-

微变等效电路和小信号等效电路分析方法的区别2024-07-16 4105

-

微变等效电路和小信号等效电路的区别2024-07-15 4657

-

诺顿等效电路和戴维南等效电路的区别2023-12-07 9334

-

锂离子电池的等效电路建模2023-11-23 3184

-

含受控源网络戴维宁等效电路的一种求解方法2023-11-18 510

-

什么是等效电路模型?等效电路元件有哪些?2023-06-01 25438

-

电子电路仿真基础:SPICE模型的种类2023-02-14 3527

-

画等效电路图的技巧及步骤2023-01-09 3278

-

实用干货!20种电子元器件等效电路总汇2020-07-05 2899

-

诺顿定理的等效电路说明2019-06-23 47353

-

电源旁路之SPICE仿真与现实的差距2018-09-26 1675

-

等效电路图的八种画法2018-08-21 270277

-

一种新型的共模扼流圈等效电路模型2010-05-04 1177

全部0条评论

快来发表一下你的评论吧 !