FPGA中块RAM的分布和特性

描述

导读:

在选择FPGA时,关注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因为它们是FPGA架构中的两个核心资源,对于设计的性能和资源利用至关重要。

BRAM(Block Random Access Memory,随机存取内存块),块RAM是嵌在FPGA内部、固定大小(容量)的硬IP。

为什么要嵌入丰富的块RAM?对于需要大量存储器的应用,比如需要大规模的数据存储,如图像、视频、音频等,块RAM是一个理想的选择。块RAM提供了高密度的存储,能够有效地存储和检索大量数据;对于需要频繁访问的数据,块RAM可以用作数据缓存;一些算法可能需要大量的中间数据存储,使用块RAM可以提供快速且容量大的存储,用来支持这些算法的运行;异步时钟域之间的数据传输通常需要使用FIFO(First-In-First-Out)缓冲区。

在FPGA开发中,使用块RAM的多少取决于设计的性质和对性能的需求。在设计过程中,通过合理的资源规划和优化,可以有效地利用块RAM以满足应用的需求。

注:以xilinx7系列690T为例

块RAM的分布

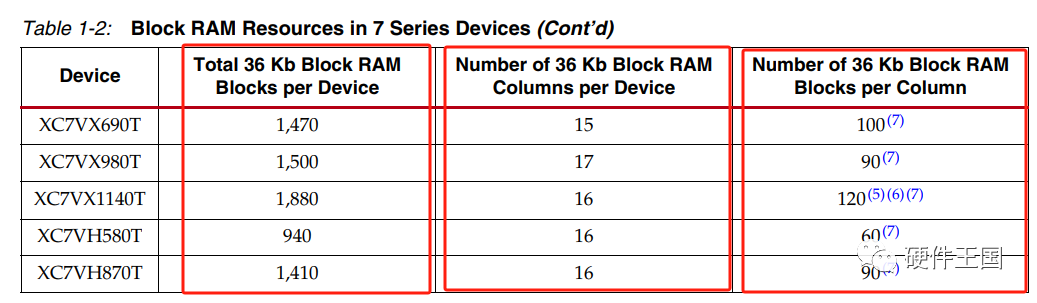

图1:产品选型指南

一些应用可能更加侧重于逻辑资源,而另一些应用可能更加侧重于存储资源,如上图1所示,以690t为例,Block RAM总数目为1470,总容量为52920kb。上图中的Distributed RAM 是 FPGA中的一种内置存储器资源。与块RAM不同,分布式RAM分散在FPGA的逻辑区域中,而不是集中在特定的块中。分布式RAM主要由可编程逻辑元件(LUTs)和触发器(Flip-Flops)组成。每个LUT都有一些存储单元,用于存储少量的数据。这些存储单元可以被组合起来,形成一个分布式的存储器。简单的说Distributed RAM就是FPGA用内部的逻辑单元拼凑而来的。一般较少使用,本文不重点讨论。

图2:7系列 块RAM资源

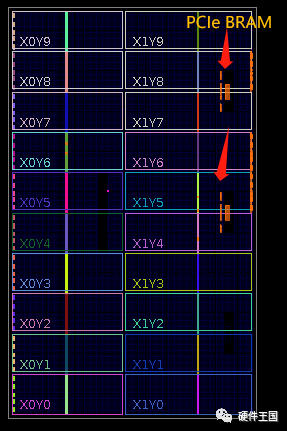

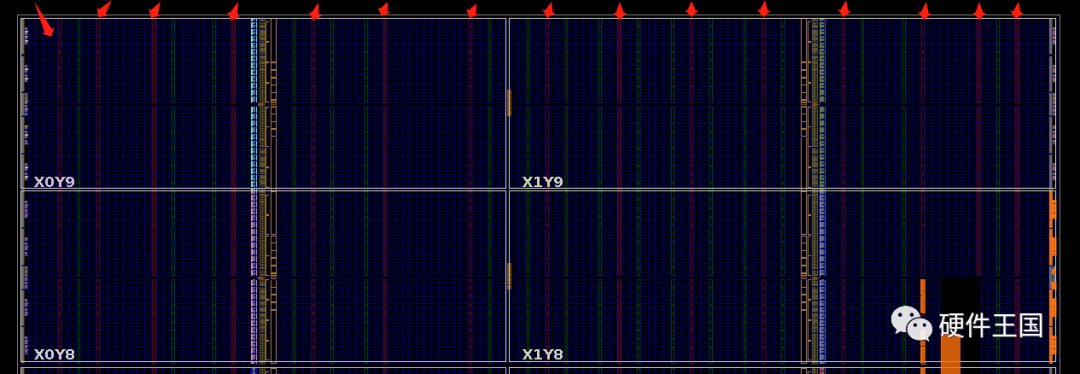

如图2可知,690T一共包含1470个块RAM,一个有15“列” 36Kb的BRAM,每“列”有100个36Kb的BRAM。结合下文图3、图4用Vivado打开实际device(690T)的视图说明,看过我前面文章的读者可知,690T一共20个时钟区域,图4是将图3最上方4个时钟区域放大后的截图,先看图4,其中每一个小红箭头代表1“列”36kb的BRAM,一共15个小红箭头(每以列共100个36kb的BRAM)。细心的读者可能发现,图2的表格一共有15列,每列100个,总数应该是1500个,为什么图2的表格总数只有1470?答案就在图3里面,因为有一些BRAM已经分配给一些高速硬核使用了,比如690T的PCIe 硬IP。

图3:Device视图

图4:Device视图(图3最上方4个时钟区域放大截图)

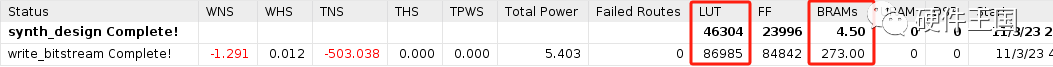

图5:工程“综合实现”后的资源消耗指示图

图5是笔者基于690T开发的一个实际工程综合实现后的资源消耗,BRAM一共使用273个,评估你所选择的FPGA是否合适,最主要就是看逻辑资源和BRAM使用情况,当然特殊要求除外(如DSP、其他硬IP等)

块RAM的特性和按“列”分布原因

FPGA块RAM的特性很多,读者不在这里细述每一个特性,读者自行参考厂商原文档,因为是硬IP。可能每个厂商支持的特性各不相同,使用时需要注意几点的是:

- 每个块RAM均可存储最多36 Kbits的数据(每个厂商的内嵌的块大小可能不一样);

- 支持将一个单独的36Kb块RAM分成两个独立的18Kb块使用(具体看厂商规格书);

- 两个相邻的块RAM可以组合成一个更深的64K x 1内存(具体看厂商规格书);

- 支持端口模式(简单双端口(SDP)、真双端口(TDP)。(具体看厂商规格书)。

FPGA中的块RAM按列分布的设计选择通常是出于性能和资源利用的考虑。这种设计决策涉及到FPGA内部架构和数据流的优化。

- 性能优化: FPGA内部的块RAM通常是在每个列中集中分布。这样设计有助于减小数据路径的长度,从而减小延迟,提高访问速度。如果块RAM散布在整个FPGA芯片上,可能需要更长的路径来连接块RAM和其他逻辑单元,导致性能下降。

- 资源共享: FPGA中的资源是有限的,通过将块RAM集中在每个列中,可以更好地进行资源共享。这有助于防止资源争用和碎片化,使得在某一列中的块RAM更容易分配给邻近的逻辑单元,减少资源冲突。

- 时序和布线简化: FPGA中的时序分析和布线操作通常是按列进行的。将块RAM集中在每一列中可以简化时序分析,减小时序问题的复杂性,使得设计更容易达到目标时钟频率。

总结

按列分布块RAM是一种有效的设计选择,有助于提高性能、优化资源利用,并简化时序和布线操作。不过,具体的FPGA架构和设计工具可能会有一些差异,因此在具体的FPGA系列和工具链中可能会有一些微妙的差异。

-

FPGA芯片内部结构解析(2)2023-08-15 1974

-

块RAM存储器中的地址冲突场景2026-04-24 7076

-

Quartus II 中定制的RAM是分布式的还是块的2014-03-10 2904

-

介绍FPGA开发板内部ram操作2020-09-10 2322

-

Vivado的多种RAM编写方式2020-09-29 4650

-

在FPGA设计中如何用LUT组建分布式的RAM2021-07-28 1540

-

FPGA内嵌的块RAM在FFT算法中的应用2011-09-27 1450

-

采用FPGA与IP来实现DDR RAM控制和验证的方法2017-11-24 4858

-

技术控:FPGA中RAM使用技巧探索2018-03-28 10865

-

Spartan-6 FPGA块RAM的技术参考资料免费下载2019-02-15 1694

-

详细介绍关于FPGA开发板内部ram是如何操作的2020-07-20 2783

-

FPGA的RAM存储资源详细资料说明2020-12-09 3262

-

使用FPGA调用RAM资源的详细说明2020-12-30 2198

-

FPGA在一个时钟周期可以读取多个RAM数据吗?2023-10-18 2241

-

fpga双口ram的使用2024-03-15 2488

全部0条评论

快来发表一下你的评论吧 !