芯片设计复杂性处理之层次结构概念分析

EDA/IC设计

描述

几十年来,一种结构层次结构一直是处理芯片设计复杂性的主要手段。它并不总是完美的,也没有理想的方法来分而治之,因为这需要专注于正在执行的分析。事实上,大多数系统都可以从各种不同的层次结构中查看,同样正确,并共同形成一个异层次结构。

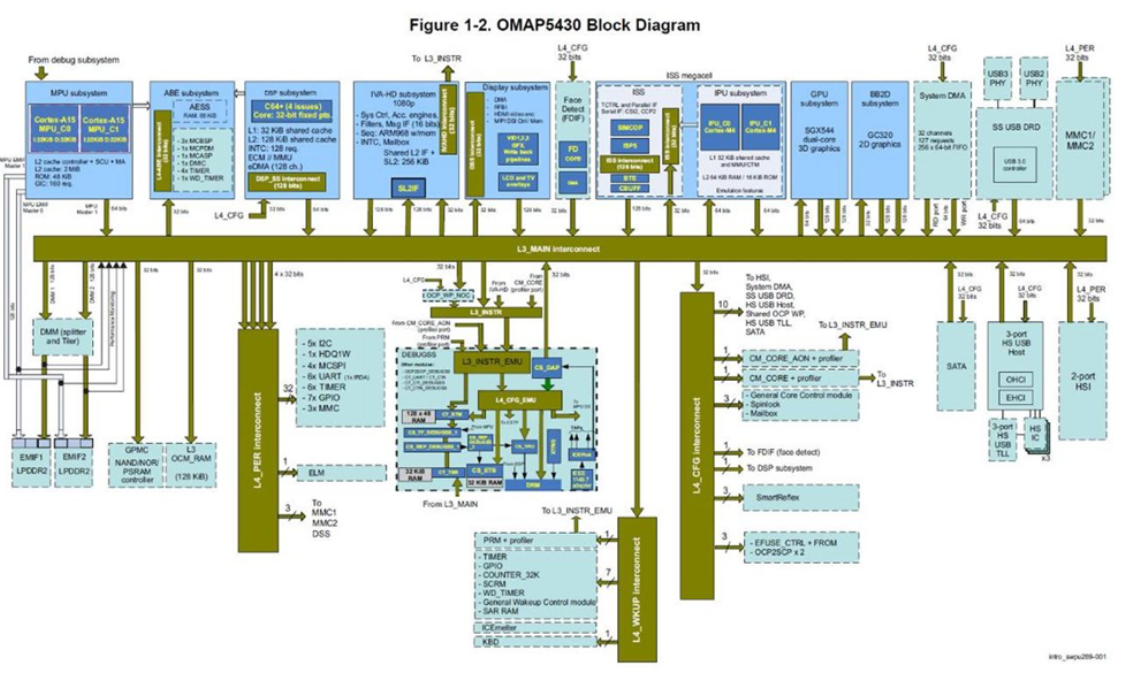

考虑当今使用的层次结构形式的最简单方法是要求工程师从概念上设计一个系统。他们可能会开始绘制一个包含大块的框图,其中包含 CPU、编码器、显示子系统等标签。这不是一个功能层次结构,尽管许多划分的块被认为是提供功能的。这也不是纯粹的结构分解,因为在芯片中,一切都变成了晶体管的无定形海洋。

该图大致遵循为印刷电路板设计开发的层次结构,即引脚层次结构。在最低级别,您可能使用了逻辑库,例如德州仪器 (TI) 7400 系列。这些设备有引脚映射。层次结构的下一个级别是电路板级别,以及连接到背板的引脚。两者之间几乎没有任何层次结构,原理图只是分布在多个“图纸”上。后来,当系统变得更加复杂时,也支持结构层次结构。

图1:2013年左右复杂芯片的典型框图。来源:德州仪器

这种形式的层次结构提供了一种封装,允许每个块的开发在某种程度上变得孤立,并将相互依赖性最小化。顶层成为这些块相互连接的方式。然后,每个分割的块都可以经历类似的分解。

使用层次结构的原因有很多。“容量是其中之一,”Ansys产品营销总监Marc Swinnen说。“问题变得太大了,你必须把它分解成碎片。另一个是并行工程。你有多个团队想要同时进行设计,所以你把它分解并分别处理零件。三是重用。您希望重用其他人设计的块。其中一种微妙的形式是标准单元库,它本身就是一种层次结构形式。第四个原因是数据量的可管理性。第五个原因是重复的结构,比如内存、多核,你只是自然地重用。第六个原因是混合域,例如模拟/数字,每个块中都有不同的设计风格。你将使用不同的工具,所以你把它们分层分解。

容量

随着设计规模越来越大,许多算法需要越来越多的时间才能运行。分解它们可以缩短执行时间并减少所需的资源。Synopsys数字实现小组高级产品经理Jim Schultz表示:“对于大型设计,当您进入物理实现阶段时,这些非常大的设计可能需要数天甚至数周的时间才能完成。“如果你把事情搞砸了,成本可能会很高。等级制度是一种分而治之的方式。它让我们知道我们可以一次关闭设计的一个部分。随着我们不断增加功能,芯片越来越大,这不仅与运行时有关,还与资源耗尽有关——放置所有这些可重用实例所需的内存量超过了容量。

为了能够进行分层分析,必须确保为每个块正确设置了边界条件。然后,您需要在顶层跨边界进行分析。

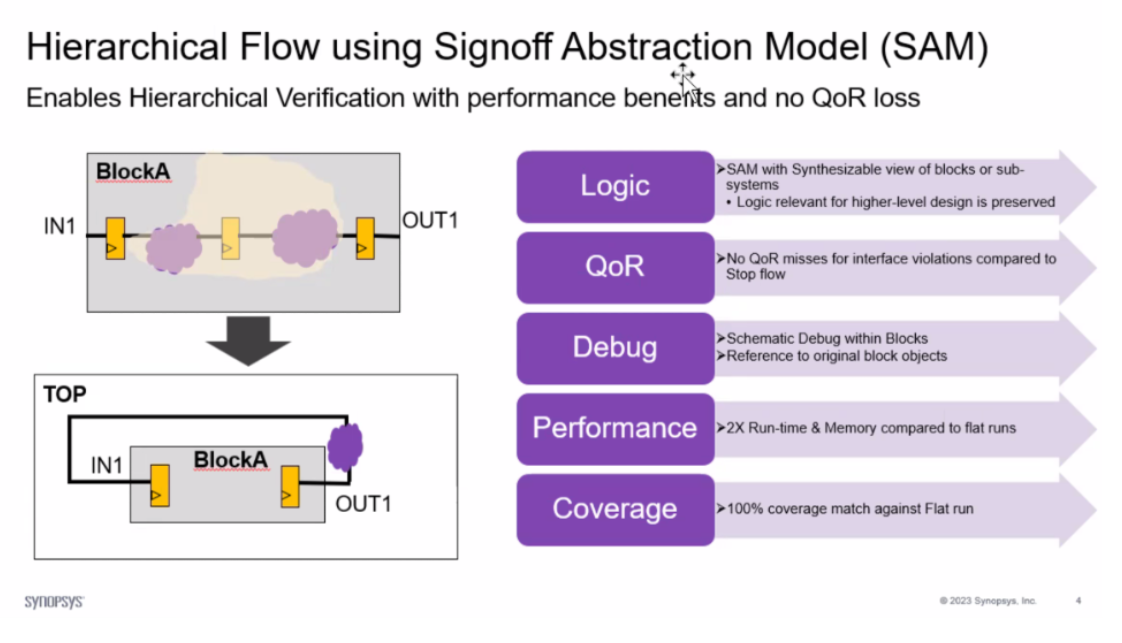

“平面分析需要花费大量时间,但可以提供完全的准确性,”Synopsys 产品经理 Rimpy Chugh 说。“在层次结构中采用黑盒方法可以提高速度,但会失去准确性。这需要一种专门的解决方案(见图2),其中可以保留模块的接口逻辑,从而同时获得速度和准确性的好处。可以在 IP 级别生成抽象模型,然后在 SoC 级别使用它。

图 2:使用抽象模型的分层流程。来源:Synopsys

并行工程

设计团队不再局限于一栋建筑。“许多设计正在被划分,以便一个团队在一个层次结构上工作,另一个团队在另一个层次结构上工作,它们可能在同一栋建筑中,也可能分布在世界各地,”是德科技 EDA 数据和 IP 管理产品管理总监 Simon Rance 说。“这可能会带来挑战,因为团队现在的工作速度不同。拥有稳定的层次结构变得很重要,因为以后很难进行更改。这通常只是作为最后的手段发生,但相反,我们看到团队粘合或捏造以使其发挥作用。它可能很丑陋,但我们在小芯片上看到了更多的挑战。

重用

层次结构需要以自上而下和自下而上的方式发挥作用。“在人体中,专门的细胞组织成系统和器官,这些系统和器官构成了构成人的基石,”Cadence 高级产品营销经理 Brian LaBorde 说。“同样,晶体管组形成电路或逻辑门,这些电路或逻辑门构成组装成系统的宏。在过去的几十年里,我们看到越来越大的IC,有许多不同的专用电路,都集成在一个芯片上。这些布局的分区是虚拟的,由布局数据库中的层次结构表示。

数据管理 所有设计都会产生大量数据,并且必须对其进行管理

。是德科技的 Rance 表示:“无论是针对汽车的 ISO 26262 标准,还是针对军用航空航天的 MIL882 标准,工程生命周期管理都需要满足功能安全标准,因此您拥有许多资产,从文档到验证、测试标准、验证测试计划和结果。“所有这些都需要保留在层次结构中,以便具有完全的可追溯性。无论如何,跟踪层次结构中的所有内容是很困难的,但您也获得了设计之外的所有内容,例如验证和测试计划。当某些东西在测试中失败,甚至在现场更糟时,你回去做发现,找出可能失败的东西。如果你没有将所有这些数据和元数据附加到层次结构中,你就永远找不到它。

重复结构 许多设计都包含重复结构

,无论是存储单元、小型处理器阵列还是接口。但这些阵列中隐藏着危险。“假设你有16个CPU内核排列在一个4X4网格中,”Ansys的Swinnen说。“原则上,这些都是相同的,但实际上它们具有不同的边界条件。每个边缘周围的环境都不同。如果要进行优化,则需要对每个进行单调,因为它们在边界处都有独特的寄生效应。总是有这种权衡。你如何保持可重用性,同时找到那些独特的?当你看到像热这样的事情时,情况会变得更糟。

多域 虽然模拟和数字有很大不同,但开发流程的其他方面也利用了工具的分离。“EDA的整个想法是把这个复杂的问题,简化成一个结构性问题,把它切开,让问题变得非常简单,”Siemens Digital Industries Software的技术支持总监Ron Press说。“这就是扫描对DFT的作用。过去,即使他们有单独的内核,他们也试图在一个大的平面图像中完成所有事情。然后你必须等到设计的后期,你就会遇到一个更大的问题。现在,随着分布式设计团队和内核的重用,人们需要尽可能多的即插即用。他们将完成DFT的设计,为该内核制作图案,然后将其插入顶层。只要它有某种类型的隔离,例如包装链,他们就可以单独处理该部分,完成 DFT 设计,并完成他们的图案。这使得这些团队变得独立,并使整个过程变得更加容易。

结构层次结构的问题

没有一个系统是完美的,这种形式的层次结构确实会产生一些问题。“在这些边界处设计约束肯定会产生开销,”Synopsys 的 Schultz 说。“你必须分解约束并正确定义它们,并将它们向下推到块边界。确保正确定义这些边界是一个大问题。另一个反对它的因素是,在设计上,当你把一些东西分解成碎片,你说这些是我的分区,当我去物理实现它时,我不会跨这个边界进行优化。你无法优化——这个边界现在是固定的。如果需要在该层次结构中进行优化,则无法进行。你自己是有限的。

这可能会影响多个工具和流程。“如果他们使用分层DFT进行顶层计划,他们可能会计划将如此多的引脚连接到内核,”西门子出版社说,“然后事实证明,内核不需要太多的模式,而他们为其分配了类似数量的引脚的另一个内核需要更多的模式。如果他们很早就从顶层开始冻结了他们的设计,那么他们的模式交付就不会那么有效。

建立错误的层次结构可能会以多种方式限制您。Schultz补充道:“其中一个大问题,尤其是对于大型SoC而言,网络和通信会造成拥塞。“我们看到整个芯片出现拥塞,尤其是当设计分区不佳时。我看到块通过其他块进行通信,您必须创建馈通。这可能会导致设计出现大量拥塞。此外,当你做这样的事情时,要满足你的时序要求要困难得多,因为你无法轻松优化完整的路径。你必须单独优化每个区块,并希望路径都成功。

边界处可能会发生微妙的变化。“当你毗邻两个街区时,它们之间有一种逻辑上的联系,但那里没有物理上的东西,”Swinnen说。“针脚只是相互接触,但没有电线。但是在你的网表中,你有一根应该在那里的电线。它应该有一个电阻,一个电容。您有逻辑线路,但没有物理线路。然后是馈通,电线进入块的一侧,穿过块,然后从另一端出来。有引脚,有物理线,但没有逻辑线。从逻辑上讲,它不存在。你不会在原理图上画出来。

有些工具可以处理糟糕的层次结构,但修复它们会产生其他问题。Schultz 说:“当你开发 RTL 并综合它时,你有一个逻辑层次结构。“当你进行物理设计时,这些逻辑层次结构必须一对一地映射到物理分区。最终发生的事情是,在我的逻辑层次结构中,我可能有一个孩子在与该逻辑层次结构下的孩子交谈,而这个逻辑层次结构实际上正在与另一个父母之下的东西交谈很多,而这两个父母成为他们自己的物理分区。这两个父母可以物理地放置在芯片的两侧。逻辑层次结构不利于物理实现。处理这个问题的方式是通过 RTL 重组。现在我们开始移动东西并修复逻辑,但这不是纯粹的 RTL 或逻辑设计者会知道的事情。只有当您考虑到物理层次结构时,才会出现该信息。两者之间需要有沟通,才能真正优化物理层次结构。

这发生在流中的其他位置。“NoC 位于最高驾驶舱层,您可以在其中拥有完整层次结构的集成方面,”Arteris 解决方案和业务开发副总裁 Frank Schirrmeister 说。“当需要对层次结构进行更改时,可能是因为电源域之间存在两种不同的非功能性属性,重构 RTL 可能很简单。对层次结构进行更高级别的集成有助于您相应地重构和重构 RTL,而您真的不想通过手动更改所有模块来做到这一点。

跟踪这一点可能是一场噩梦。“想想对属于层次结构的文档或文件的修订控制,”Rance 说。“然后,你可能会有该层次结构的多个版本或修订版,这取决于你在做什么。您可能有一个进行 PPA 分析的验证团队,并发现如果他们稍微调整一下并创建此层次结构的另一个版本,它的性能会更好。你需要跟踪这一点。

尽管等级制度有助于我们分而治之,但有些事情却无视任何简化这些尝试。“像热分析这样的事情需要在整个芯片范围内完成,”Arteris 的 Schirrmeister 说。“但你需要能够将其与芯片中发生的事情在功能上联系起来,与通过它运行的数据相关联。您希望能够拍摄芯片照片,从生命周期的角度来看,您可以查看热点以及每个功能的位置,并且受到的影响最大。将其与数据相关联绝非易事。

其他层次结构

其他层次结构确实存在,例如功能层次结构。我们今天最接近这一点的是一个需求跟踪系统,它从系统应该做什么的高级定义开始。这些任务被分解为越来越简单的任务,直到最终确定实际提供它的逻辑或其他电路,以及验证是否满足适当要求的测试平台。

一些层次结构在设计过程中来来去去。“你可能有一个时钟树的层次结构,”Schirrmeister说。“配电系统有层次结构。然后,系统分析工具可以看到一个层次结构,用于它们如何将所有东西连接在一起,以获得完整的芯片视角。我们对ESL(电子系统级)的思考,是描述整个事情的可执行功能规范的概念。这是尚未出现的东西。不知何故,我们似乎侥幸逃脱了,这令人惊讶。

物理布局提供了另一个层次结构。最高层次是楼层规划,它利用结构层次结构作为起点。放置这些块,并在它们之间布线互连。每个模块都使用物理综合进行布局,这再次处理本地互连。3D-IC将为此增加一个新的维度,现在可能在Z方向上存在布线。

Cadence 的 LaBorde 表示:“随着我们开始看到基于小芯片的 2.5D 和 3D 系统取代片上系统 (SoC) 设计,层次结构将不再像物理现实的表示那样具有战略意义。“原理图中的宏可能代表系统中的芯片,每个芯片都有自己独特的工艺。它们之间的连接将是焊点,而不是布局上的象征性引脚。

结论

虽然并不完美,但今天使用的非正式结构分解已被证明是一种熟练的层次结构。流程的某些方面因此而受到影响,但大多数方面都能够有效地使用它,并且工具可以弥补其不足。虽然有一定程度的优化潜力因此而丧失,但这可能是以生产力的名义做出的小牺牲之一。

审核编辑:黄飞

-

应对芯片设计复杂性 EDA工具需要新典范2017-02-09 3277

-

抑制嵌入式系统设计的复杂性解析2020-12-30 1459

-

嵌入式调试的复杂性分析2021-02-19 1150

-

如何用可重构射频前端简化LTE设计复杂性?2021-05-24 1876

-

免疫系统的主组织相容复杂性及其应用2009-05-28 798

-

有效解决实时IoT环境监测的复杂性2016-07-14 804

-

基于构件回归测试的复杂性度量框架2018-01-19 945

-

PCB复杂性怎样来解决2019-08-16 2828

-

大数据分析学习的挑战:复杂性、不确定性及涌现性2022-11-17 3940

-

插入排序算法的复杂性、性能、分析2022-04-08 4703

-

驾驭软件定义车辆的复杂性2022-07-14 1660

-

了解 AV 复杂性2022-07-15 2410

-

是什么定义了处理器漏洞的复杂性以及如何检测它?2022-11-01 1184

-

使用Emulex SAN管理器降低操作复杂性2023-07-28 497

-

医疗PCB供应链复杂性与风险管控2025-10-14 642

全部0条评论

快来发表一下你的评论吧 !