I2C地址跳变问题的调试案例

描述

引言:I2C作为使用最为广泛的通讯接口,调试各类I2C器件,大家应该都很轻车熟路。一般对于外挂电阻配置器件的I2C地址,例如电阻上拉之后,器件的地址就会固定下来不再变动,但是今天给大家分享一个自己的调试案例,即I2C地址跳变问题。

1.问题背景

该器件对外一起只有四个引脚:SDA、SCL、INT、RESET,其中对外输出中断引脚INT兼具器件地址设定功能,将INT上拉至VDDIO,地址为0X8A,INT无上拉,地址为0X88。

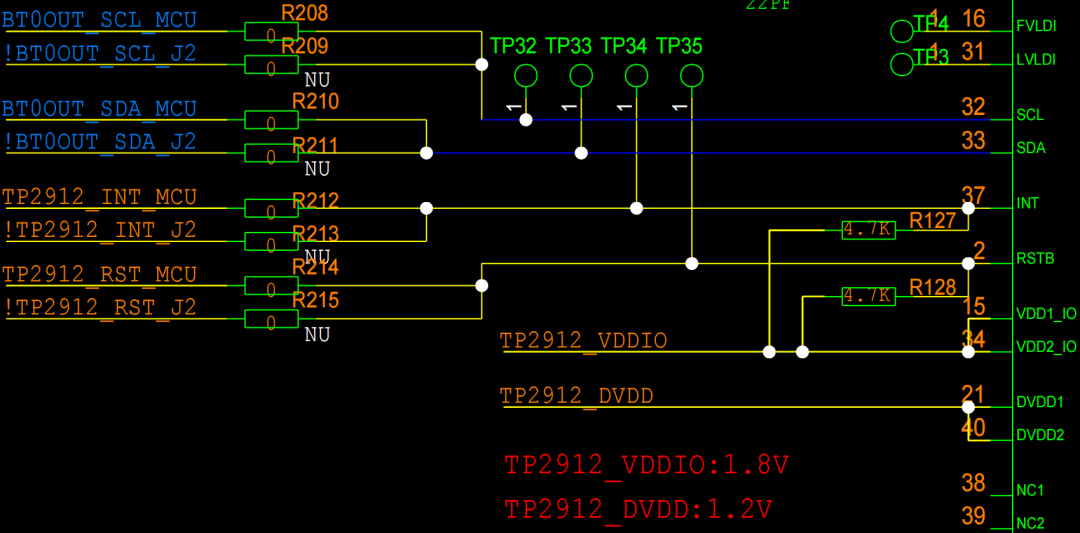

图3-1:控制线部分原理图

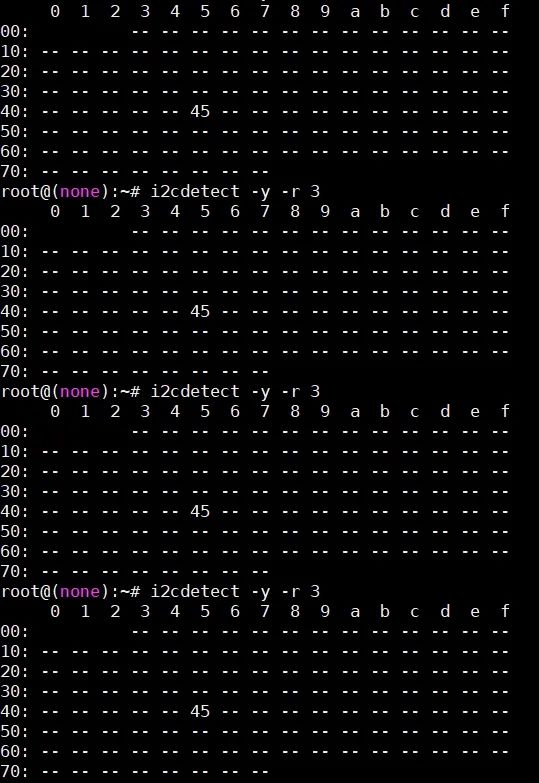

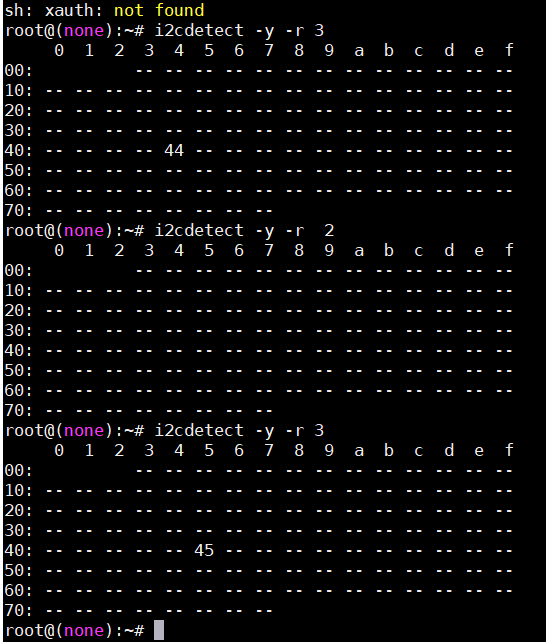

在上电启动之后,连续运行Linux地址查询命令,如图3-2所示,查询地址为0X45(7位地址,按8位即0X8A)。

图3-2:读取地址为0X45

断电再重启,然后运行查询命令,如图3-3所示,会偶发检测到地址跳变为0X44(0X88)。

图3-3:重新下电上电后读取地址

此时正确地址应该是0X45,所以偶发检测地址跳变为0X44说明器件上电初始对INT处的配置发生了误判。

2.怀疑点和排除过程

前端设备的高低电平影响

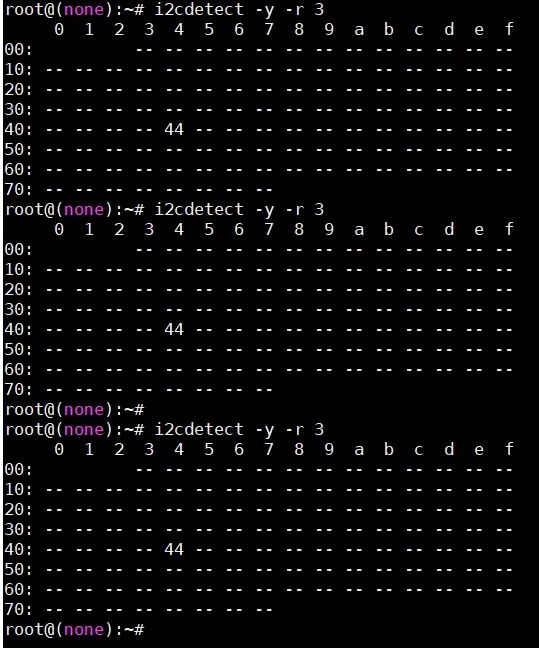

因为INT引脚是兼具I2C地址配置,如果INT存在初始拉低等情况,就会影响器件判断地址,在Application里面讲到:TP2912A通过在复位期间捆扎INT引脚来提供两个设备地址,0x88或0x8A。引脚上的上拉电阻器使设备地址为0x8A,如果电阻器不存在,则内部下拉电阻器的设备地址将为0x88。在选择设备地址时要注意,在判断复位期间,一些前端芯片可以强制驱动INT信号的逻辑低或高。在这种情况下,设备地址的检测可能是错误的,因为前端芯片驱动的逻辑电平与上拉或下拉电阻器无关,如果无法避免这些情况,则如果设备地址选择正确,则可以通过读取寄存器0xfe中的设备ID来实现软件工作。

图3-4:推荐INT Mode下读取地址程序

最开始测量INT点的电平,大约1.4V,所以其实INT引脚一直是高电平没有问题,然后断开INT与SOC的连接,继续上下电读地址,依然有I2C地址跳变问题存在,并且断开后单独测量SOC端的INT,为低电平0V,说明SOC没有配置这个引脚,没有使用到INT功能(软件端也确认过),所以排除前端设备影响INT的配置。

引脚耦合

引脚耦合这个理论上存在,但是实际中很难遇到,并且高达1.8V和0V的压差,耦合能量达到这么多几乎不可能,所以理论上排除引脚耦合问题。

上拉阈值临界

手册上的VDDIO是3.3V,并没有标注1.8V可以使用,使用1.8V是FAE的建议,也为了和前端SOC电平适配,所以是否1.8V处于一个临界上拉阈值导致器件判断失真。为了验证这一疑点,将INT上拉电阻取消,此时INT处于悬空(同时断开前级),地址应该固定为0X44,但依然存在地址跳变,说明也不是上拉阈值临界,注意这里的INT悬空并不等同于下拉到GND。

时序排查

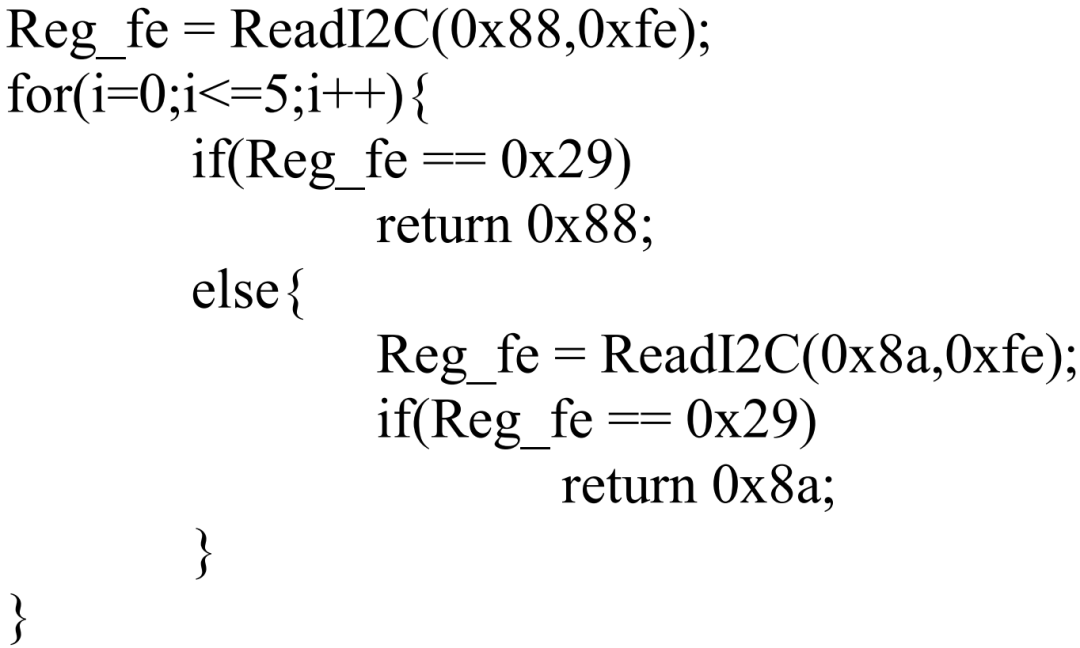

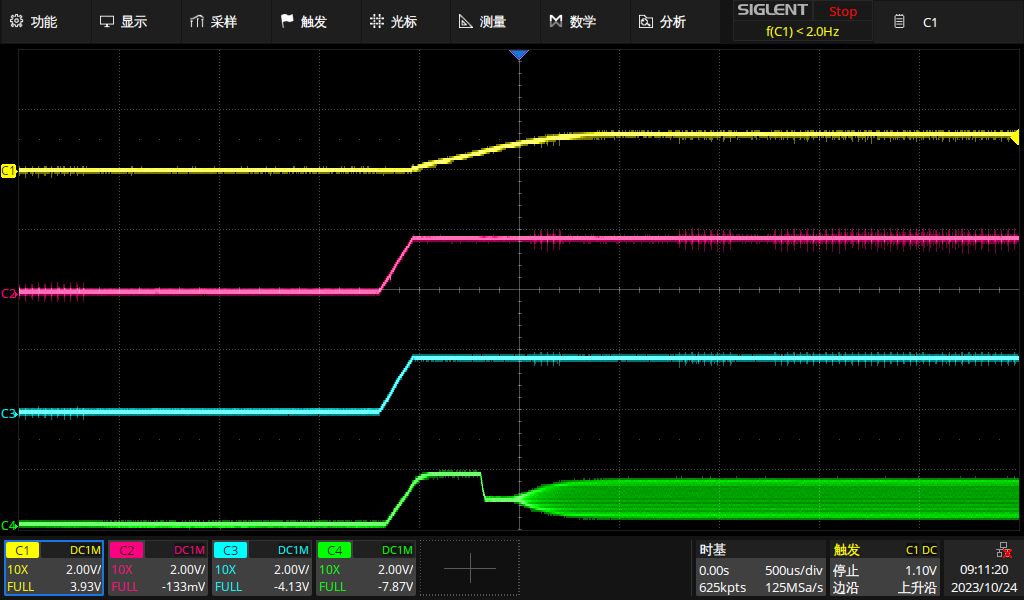

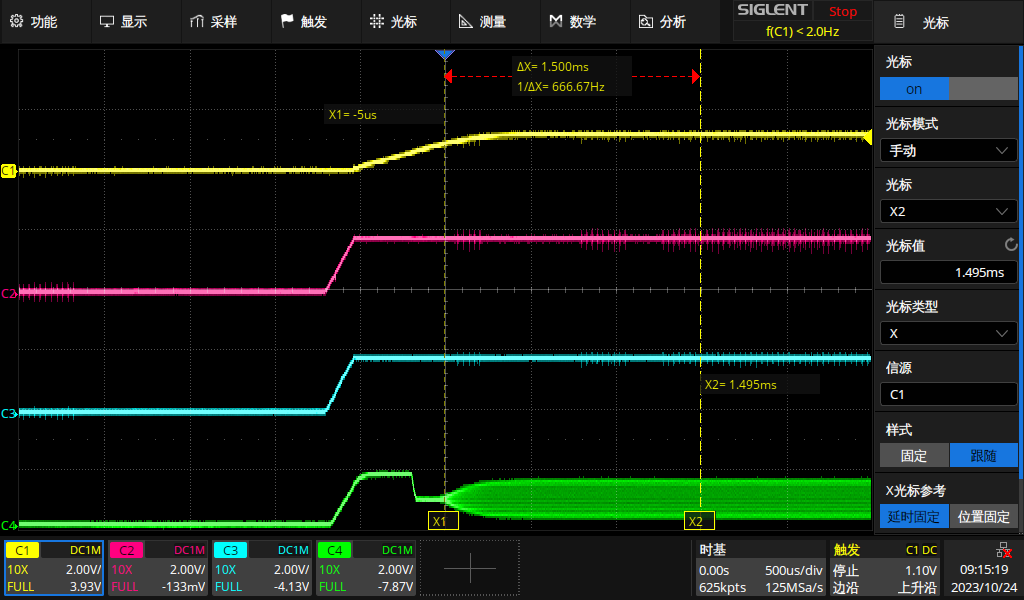

考虑到是上下电过程中触发地址误判,不断电情况下地址不会变动,所以会不会存在这样一种时序情况:在VDDIO还在上电的过程中,器件就开始读INT的配置,此时电压临界。测量器件上电时序如下图3-5 ,其中C1是DVDD(1.2V),C2是RESET,C3是1.8V,C4是XTI(27MHz晶振输入)。

图3-5:关键信号上电时序

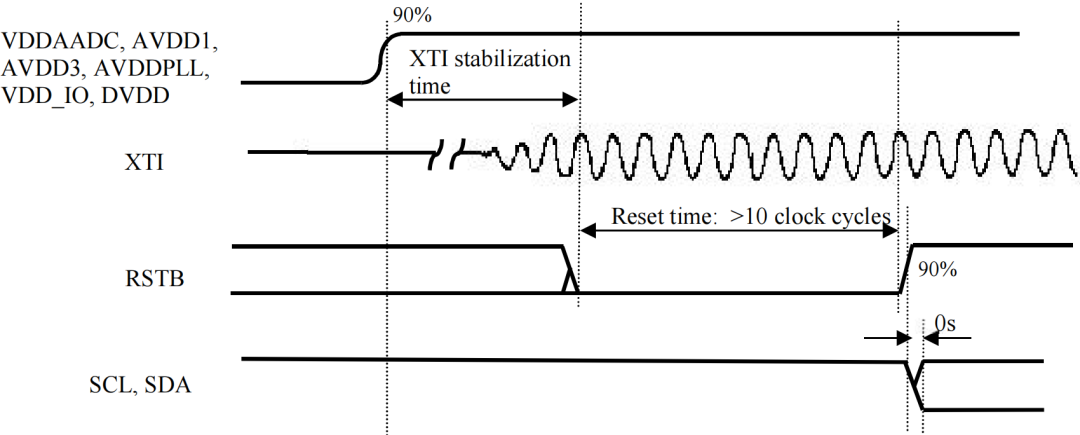

从图中可以看到,在XTI还在起振时,DVDD还处于上升阶段,此时芯片逻辑核心可能还没有开始工作,逻辑核心影响了器件读I2C地址。Application里面也提到了这一时序要求:由于POC(上电序列)功能在上电/断电事件期间在芯片内部操作,因此对每个电源树的上电和断电序列没有要求,复位应在晶体振荡器稳定后至少10个周期保持低电平,如图3-6所示:

图3-6:Application推荐Reset操作

为了验证这一猜想,首先触发一次0X44地址,然后不断电,给RESET一个复位拉低,然后再读地址,看地址是否会恢复到0X45,当然这里也可以使用手动复位,将RESET引脚手动接一下GND。

图3-7:不断电验证地址恢复

如图3-7所示,触发之后0X44变为0X45,验证有效,说明和猜想一致,最终确定是时序的问题。

3.如何修正

修正也很简单,如图3-8所示,前端SOC在上电之后10ms将Reset拉低,拉低时间≥10us。

图3-8:复位时间预估

4.总结

I2C地址跳变的问题比较难遇到,因为大多数器件是独立配置地址,如果是GND配置,自然不会考虑时序问题,但如果是上拉配置,就需要注意电压时序问题,在系统起来之前,配置电压就应该完全到位,如果有类似的情况或者电压无法调整,此时Reset不失为一种可靠的方法,不断电的情况下复位系统逻辑,器件就会重新去读地址然后写入寄存器,另外这一步需要放置主程序运行之前,否侧运行中地址变化会发生通讯中断。

-

MM32F013x上实现I2C多地址的功能应用2021-01-05 2683

-

无法读取I2C地址的调试案例2023-11-02 4458

-

I2C地址切换电路2009-02-22 1729

-

arduino读取I2C总线上连接设备的地址2017-11-23 113761

-

mpu6050对应i2c地址是什么_如何读取数据2017-12-11 26536

-

如何将I2C从地址左移1位2019-08-05 2341

-

I2C/SMBus地址转换器2021-04-20 1009

-

嵌入式linux应用读写i2c示例2021-11-01 1230

-

硬件I2C与模拟I2C2021-12-28 3413

-

I2C扫描仪之如何在Arduino上查找I2C地址2023-01-31 1842

-

如何提高I2C调试效率?2023-06-08 2469

-

Android Things I2C地址扫描器2023-06-13 645

-

I2C和I3C的区别有哪些2023-07-22 10631

-

I2C总线设备地址设置方法2025-01-17 8677

-

Adafruit TCA9548A 1-to-8 I2C 多路复用器:解决 I2C 设备地址冲突的利器2026-05-11 280

全部0条评论

快来发表一下你的评论吧 !