专利分析揭示AI热潮背后,HPC的发展

描述

先进 CMOS 逻辑和先进封装的共同开发将是实现下一代高性能计算设备的关键。

ChatGPT 和自动驾驶系统等 AI 技术的实施是每个人都在关心的问题。需要注意的是,AI 的崛起是建立在半导体设备制造 (SDM) 的进步基础上的,以产生高性能计算设备。

半导体器件的制造是一个快速发展的行业,拥有一系列互联技术。该领域的核心要素是 CMOS 逻辑,它驱动 CPU 和 GPU。在如此快速发展的领域,仔细研究该技术的制造商以及他们如何提供高性能芯片以实现人工智能创新至关重要。

前20名先进SDM专利拥有者

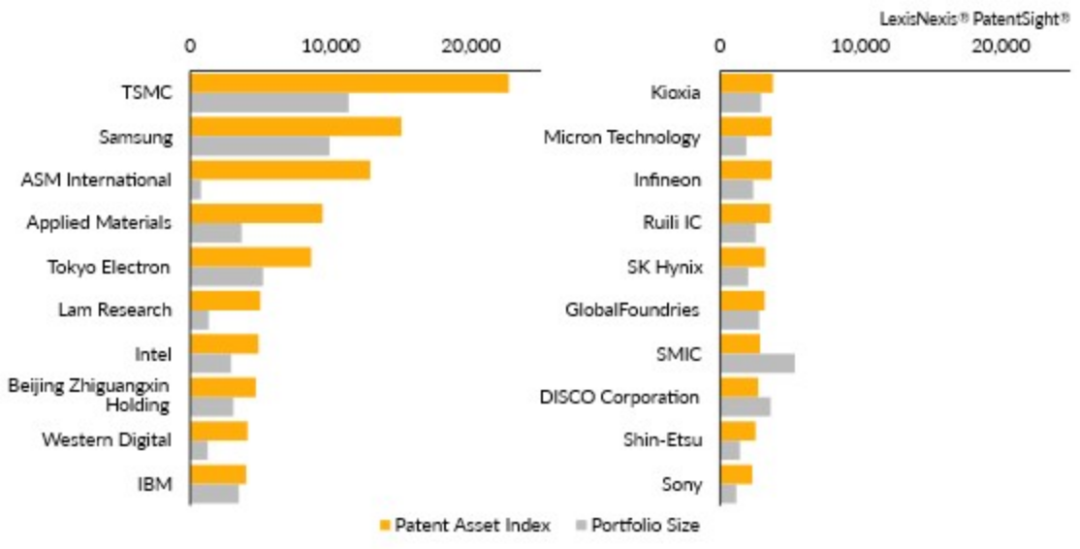

图 1. 按专利资产指数衡量的组合强度排名前 20 位的 SDM 专利所有者

台积电是先进制造领域明显的领导者,拥有最大的专利组合规模、活跃专利族数量和最高的专利资产指数(衡量专利组合累积实力的指标)。三星排名第二,ASM International 排名第三。

在整个前 20 名中,一系列公司正在以不同的方式为行业做出贡献,包括: 台积电是一家纯粹的代工厂——一家专门为客户生产的合同制造商; 三星和英特尔是IDM,既生产自己的设计,也生产第三方的设计; 设备供应商 ASM International 和 Applied Materials; 西部数据和英飞凌是集成器件制造商,只生产自己的设计; IBM,这是一家研发公司,进行研发,但不大规模生产产品。 值得注意的是,IBM 和 GlobalFoundries 均出现在本次分析中;GlobalFoundries 于 2014 年收购了 IBM Electronics 及其专利,但 IBM 仍在继续其半导体研发。

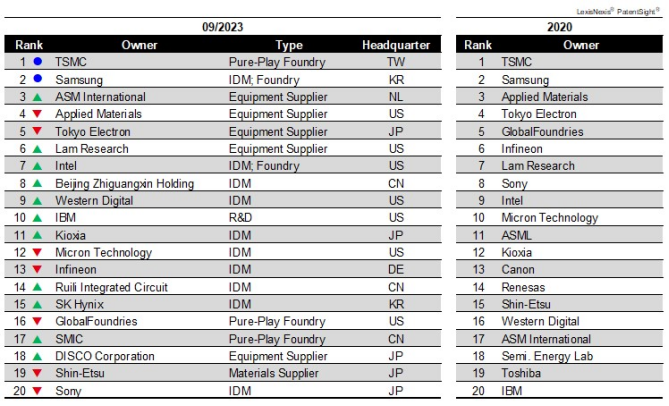

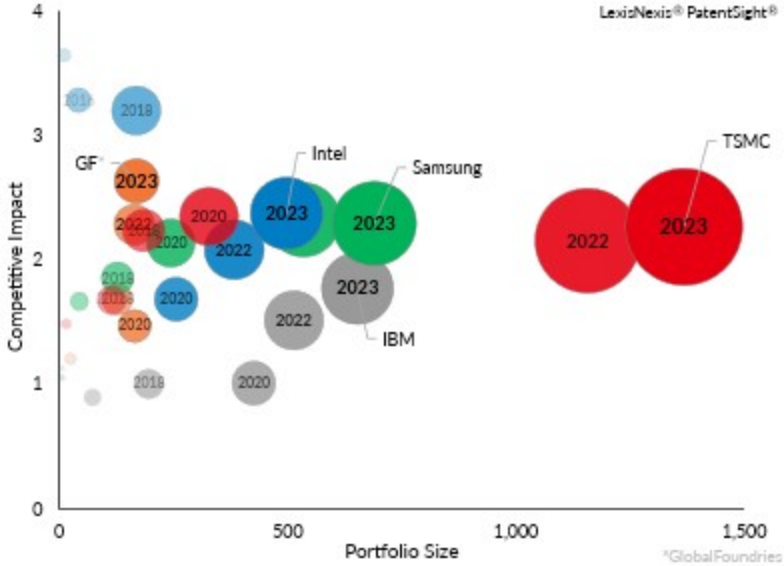

图2:2023年9月和2020年排名前20位的SDM专利拥有者。

图 2 概述了公司类型、总部所在地以及自 2020 年以来该领域的变动。虽然分别排名第一和第二的台积电和三星没有发生变化,但其他参与者在每个领域都发生了重大变动。其他组织的排名也发生了变化(例如,英特尔从第九名上升到第七名)。

面向未来高性能计算的 CMOS 逻辑

实现更低功耗和更高性能的计算需要的不仅仅是改进;核心半导体制造领域需要实现革命性创新。CMOS 逻辑核心的晶体管需要发展到能够缩小至 2 纳米(DNA 链的宽度)。在这种规模下,仅仅缩小设备尺寸已经不够了。半导体器件制造商正在遇到原子尺寸和量子尺度效应的物理限制。为了克服这些挑战,过去十年来,在晶体管的设计和结构方面投入了大量的精力和资源进行创新。

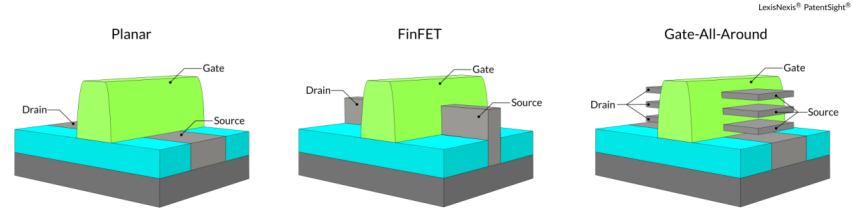

图 3. 说明不同晶体管类型的示意图

直到 2012 年,晶体管都是平面器件,即栅极下方简单、平坦的晶体管沟道结构,如图 3 最左侧所示。然后,在 2012 年,英特尔推出了首款商用 22 纳米 3D 晶体管,称为“FinFET ”。对于FinFET器件,栅极覆盖鳍沟道表面的三个侧面,以具有更高的电流并克服沟道宽度较小的平面结构的问题。此后,台积电为 Nvidia、Apple 和 AMD 等主要 CMOS 逻辑产品公司生产最先进的 FinFET 器件,成为市场领导者。

十多年后,FinFET 的微缩已经达到了 3nm 工艺节点的性能极限,需要一种更先进的晶体管类型:环栅 (GAA) 晶体管,如图3右侧所示,GAA 晶体管的沟道完全被栅极包围。GAA 晶体管提供比 FinFET 更好的性能,并且还可以进一步减小器件尺寸。

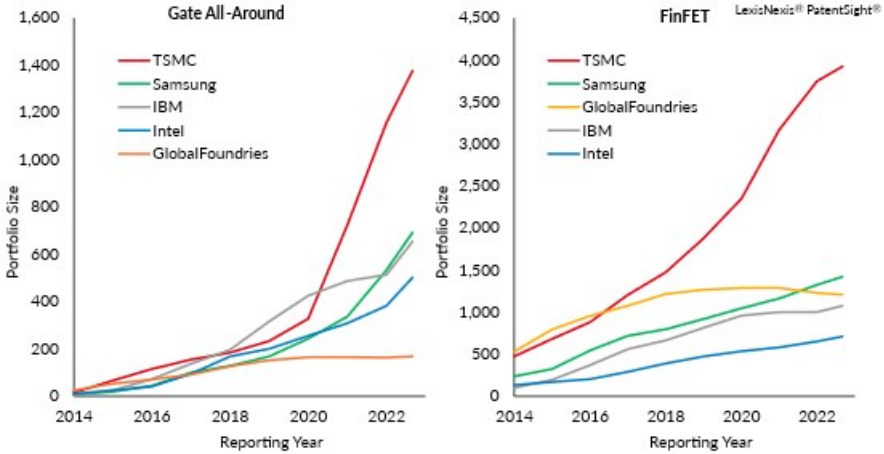

图 4. 选定专利所有者的 GAA(左)和 FinFET(右)晶体管的投资组合规模趋势

图 4 突出显示了四大半导体逻辑器件制造商(加上 IBM)针对这两种晶体管类型的产品组合规模,显然,GAA 是这两项创新中较新的一项,在过去五年中增长最为显著,而 FinFET 则在十多年来有了明显的发展。

如今,台积电在这两项技术上都占据第一的位置。三星、IBM 和英特尔似乎也在该领域继续发展,但速度要低得多。GlobalFoundries 最初的高投资组合规模是其收购 IBM 的结果,但增长放缓似乎与其在 2018 年宣布放弃 7nm 工艺技术的开发有关。

对于GAA来说,2018年之前并没有明确的领导者。2018年至2020年间,IBM似乎增加了其产品组合,但这种发展趋势在接下来的几年里并没有以同样的速度持续下去。三星和英特尔的增长明显,但这与台积电的快速增长相形见绌,台积电从 2020 年到 2022 年增长了四倍。

图 5. 拥有最强 GAA 组合的五个专利所有者的平均质量(竞争影响)与数量(组合规模)关系图 – 气泡大小代表专利资产指数衡量的组合强度

图 5 显示了这些所有者在 GAA 中的当前地位,其质量是通过对纵向的竞争影响来衡量的,而数量是通过水平上的投资组合规模来衡量的。最暗的泡沫是 2023 年的状态,每个较亮的泡沫都会从 2023 年回溯到 2022 年、2020 年、2018 年、2016 年和 2014 年。

如今,台积电在投资组合规模和实力方面均处于领先地位。自2020年以来,台积电的投资组合实力显示泡沫尺寸显著增加。此外,三星、IBM 和英特尔都扩大了其产品组合的规模和质量。这四家公司的平均专利质量随着其专利组合规模的增加而提高,这意味着新申请的专利必须与之前的专利具有相同或更高的质量。对于不断增长的投资组合来说,情况通常并非如此,这反映了 GAA 技术的进步。

唯一的例外是 GlobalFoundries,尽管平均质量有所提高,但自 2018 年以来,其投资组合规模几乎没有变化。这反映了该公司选择不追求 GAA 技术。

行业消息显示,三星最近已开始在 3nm 工艺节点进行 GAA 生产,台积电和英特尔均宣布将在未来几年内开始 2nm 工艺节点的 GAA 生产。

增强晶体管创新——先进封装

摩尔定律指出,集成电路上的晶体管数量每两年就会增加一倍,而成本的增长却极小。从历史上看,CMOS逻辑芯片将其所有功能集成到单个片上系统上,例如计算核心、存储器和输入/输出控制器。随着现代半导体器件更多功能的需求,额外的器件(例如,高带宽存储器)通过先进的封装技术与逻辑芯片集成。

例如,在高性能计算中,处理器需要大量具有短互连和高数据传输速率的近距离内存。这种近内存计算要求可以通过先进的封装来满足,例如英特尔的嵌入式互连桥和 Foveros。Nvidia 的 H100是先进封装的商业化示例,它建立在台积电的 CoWoS 技术之上。另一个例子是AMD的MI300 ,它采用台积电的CoWoS和集成芯片系统(SoIC)。AMD首席执行官苏姿丰甚至表示,如果没有台积电,AMD就不可能做出MI300。

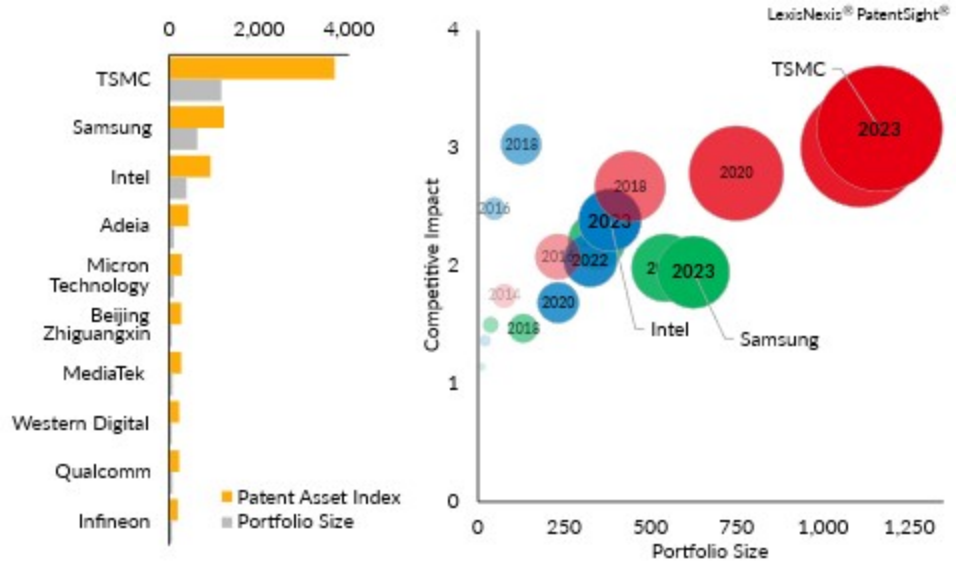

图 6. 前 10 位专利拥有者的专利组合规模和专利资产指数(左)以及拥有最强组合的三位专利拥有者的先进封装组合趋势(右)——质量与数量图表

图 6 显示了先进封装领域排名前 10 位的厂商。台积电显然在这一领域占据主导地位,其次是三星和英特尔。其他参与者的规模要小得多,但技术重点也略有不同。Adeia、美光、北京智广芯控股、西部数据和英飞凌并不专注于 CMOS 逻辑技术。联发科和高通是无晶圆厂专利所有者。

图6右侧突出显示了前三名公司的发展情况。由于 CMOS 逻辑的先进封装取决于先进的半导体器件制造能力,这三家公司有能力进行大批量的先进封装来满足人工智能的蓬勃发展。英特尔和台积电近年来都有着积极的发展。令人印象深刻的是,台积电凭借更大的尺寸和更高的质量,使其稳居第一。随着产品组合规模的扩大,三星的质量略有下降。

扩展摩尔定律

随着这些单独功能的需求,IP 模块不断增加,这些功能所需的电路规模也随之增加。用于这些设备的半导体芯片变得如此之大以至于不易于制造。创新的解决方案是在单个较小的芯片或“小芯片”上制造此类IP块,并使用先进的封装将它们重新组合。这种方法还允许添加计算单元的芯片和/或小芯片与其他外部存储器和神经网络计算单元并将其连接起来,以提供更多的功能和性能。

对于高性能计算,芯片和小芯片之间更短的互连和更高的数据传输速率是必要的。将小芯片与间距仅 20 微米或更小的互连连接起来是尖端的先进封装,称为细间距封装。台积电的 SoIC 或英特尔的 Foveros Direct 可以实现这一点,从而实现高性能计算。厂商(例如AMD)已经将其采用台积电制造的3D V-Cache 技术推向市场。

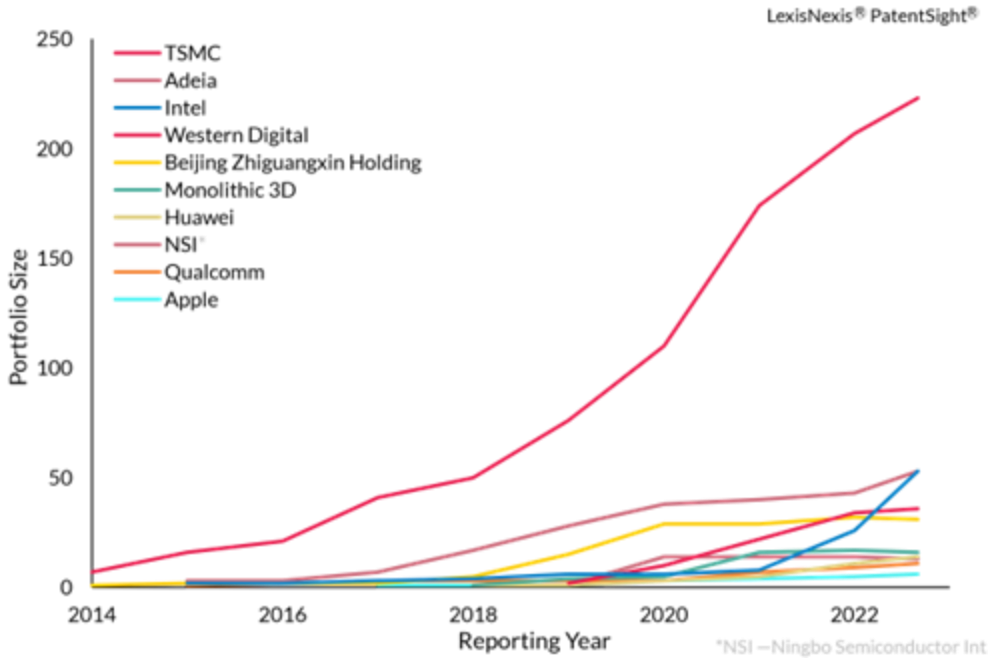

图 7. 前 10 位专利所有者的细间距封装组合规模趋势

图 7 反映了该领域的所有者及其投资组合的长期发展。台积电在这项尖端技术方面很早就处于领先地位,并在过去十年中不断发展。然而,其他参与者并没有看到同样水平的持续发展。近几年Intel开始发展,增长明显;英特尔目前的趋势非常积极,但仍远远落后于台积电。

展望未来

创新的步伐是不懈的——在先进半导体 CMOS 逻辑器件制造和先进封装领域尤其如此。这两种技术过去并行发展,但现在它们之间的界限正在消失。先进 CMOS 逻辑和先进封装的共同开发将是实现下一代高性能计算设备的关键。

-

新能源汽车驱动电机专利信息分析2025-03-21 438

-

轮边驱动电机专利技术发展2025-06-10 304

-

无刷双馈电机专利技术发展2025-06-25 186

-

了解AI人工智能背后的科学?2017-09-25 3686

-

AI芯片热潮和架构创新有什么作用2020-04-23 2285

-

AI芯片热潮和架构创新是什么2020-04-24 1993

-

GPU爆炸式发展背后的深层原因?2021-03-11 3405

-

2018年智能制造装备行业市场分析 各地掀起集群化发展热潮2018-01-22 1248

-

AI的发展大热潮_AI进步正让人类焦虑2018-03-24 698

-

深度盘点世界各国AI专利2018-12-03 6772

-

HPC与AI:完美融合2023-10-22 2624

-

助力科学发展,NVIDIA AI加速HPC研究2024-05-14 1146

-

AI与HPC技术推动先进封装行业发展2024-10-22 1378

-

维谛技术(Vertiv):未来HPC,你想象不到的酷炫变革!2024-10-30 948

-

新华三全面接入DeepSeek,引领AI发展新热潮2025-02-10 1053

全部0条评论

快来发表一下你的评论吧 !