数字电路中的亚稳态产生原因

描述

亚稳态是指触发器的输入信号无法在规定时间内达到一个确定的状态,导致输出振荡,最终会在某个不确定的时间产生不确定的输出,可能是0,也可能是1,导致输出结果不可靠。

1、亚稳态产生原因

亚稳态的产生是 输入信号违背了触发器的建立时间和保持时间导致的 。建立时间是指在时钟边沿到来之前输入信号必须保持稳定的时间。保持时间是指在时钟边沿到来之后数据必须保持稳定的时间。输入信号如果在这两个时间段内没有保持稳定,就将产生亚稳态现象。

2、同步机制

亚稳态无法避免,只能通过一定方法阻止其向后级传播,避免其对后级电路产生影响。主要方法有: 引入同步机制 、 采用响应更快的触发器 、降低时钟频率等。接下来介绍一下如何通过同步机制阻断亚稳态的传播。

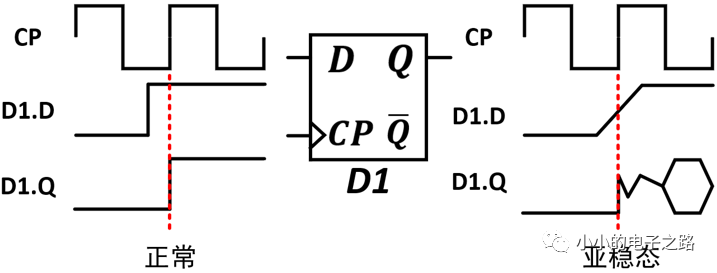

如下图所示,如果触发器出现亚稳态现象,该电路将无法准确检测输入信号是否出现上升沿。

(1)若D1.Q稳定在低电平,能够检测出上升沿;

(2)若D1.Q稳定在高电平,不能检测出上升沿;

但是,如果采用两个触发器级联的方式引入同步机制,情况就不一样了,电路将准确检测输入信号是否出现上升沿。

(3)若D1.Q稳定在低电平,在输入信号上升沿出现两个时钟周期后,检测出上升沿;

(4)若D1.Q稳定在高电平,在输入信号上升沿出现一个时钟周期后,检测出上升沿。

总而言之,该电路始终能够检测出上升沿,只是时间问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

数字电路中的亚稳态是什么2024-05-21 3364

-

FPGA设计中的亚稳态解析2023-09-19 3693

-

什么是亚稳态?如何克服亚稳态?2023-05-18 6255

-

今日说“法”:让FPGA设计中的亚稳态“无处可逃”2023-04-27 886

-

在FPGA中,同步信号、异步信号和亚稳态的理解2023-02-28 1057

-

亚稳态产生原因、危害及消除方法2022-09-07 11685

-

数字电路设计中跨时钟域处理的亚稳态2021-08-25 3086

-

FPGA中复位电路产生亚稳态概述与理论分析2020-10-25 3336

-

FPGA--中复位电路产生亚稳态的原因2020-10-22 2073

-

在FPGA复位电路中产生亚稳态的原因2020-10-19 1730

-

亚稳态问题解析2013-11-01 5326

-

FPGA中亚稳态——让你无处可逃2012-01-11 4658

-

一种消除异步电路亚稳态的逻辑控制方法2011-10-01 1197

全部0条评论

快来发表一下你的评论吧 !