如何在 3DICC 中基于虚拟原型实现多芯片架构探索

电子说

描述

前言

Chiplet多芯片系统将多个裸芯片集成在单个封装中,这对于系统架构的设计来说增加了新的维度和复杂性,多芯片系统的设计贯穿着系统级协同设计分析方法。

在系统定义和规划时,虚拟原型可以用来分析架构设计决策可能产生的影响,将系统的功能性和非功能性要求转化为系统的物理硬件属性,包括裸片的目标工艺、面积大小以及不同组成芯片的组装要求等。根据不同的解决方案,选择不同的chiplets和堆叠架构,进行早期的分析驱动的架构探索和优化迭代,包括电气可靠性、散热、良率分析、应力分析等等。从而可以基于目标系统的指标定义,确定系统的瓶颈所在——性能、功耗、存储容量/带宽、面积/体积、成本以及上市时间等,逐步建立和完善各类分析模型,使得整个系统最终定型。

芯和半导体的3DIC Compiler(以下简称“3DICC”)设计平台,全面支持chiplet多芯片系统2.5D/3D集成设计和仿真。本文介绍如何在3DICC设计平台实现基于虚拟原型实现多芯片架构探索。整个流程包含chiplets虚拟原型和顶层创建、布局堆叠规划、Bump/TSV设计规划、PG网络规划和系统早期EMIR Thermal分析等。

案例介绍

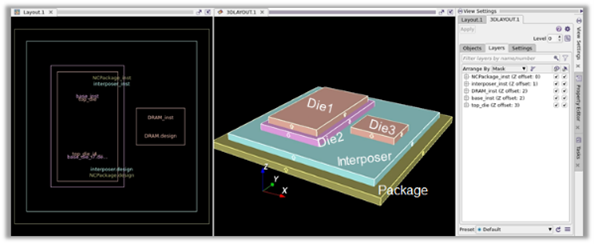

图1:多芯片系统3D架构探索、布局、分析和迭代

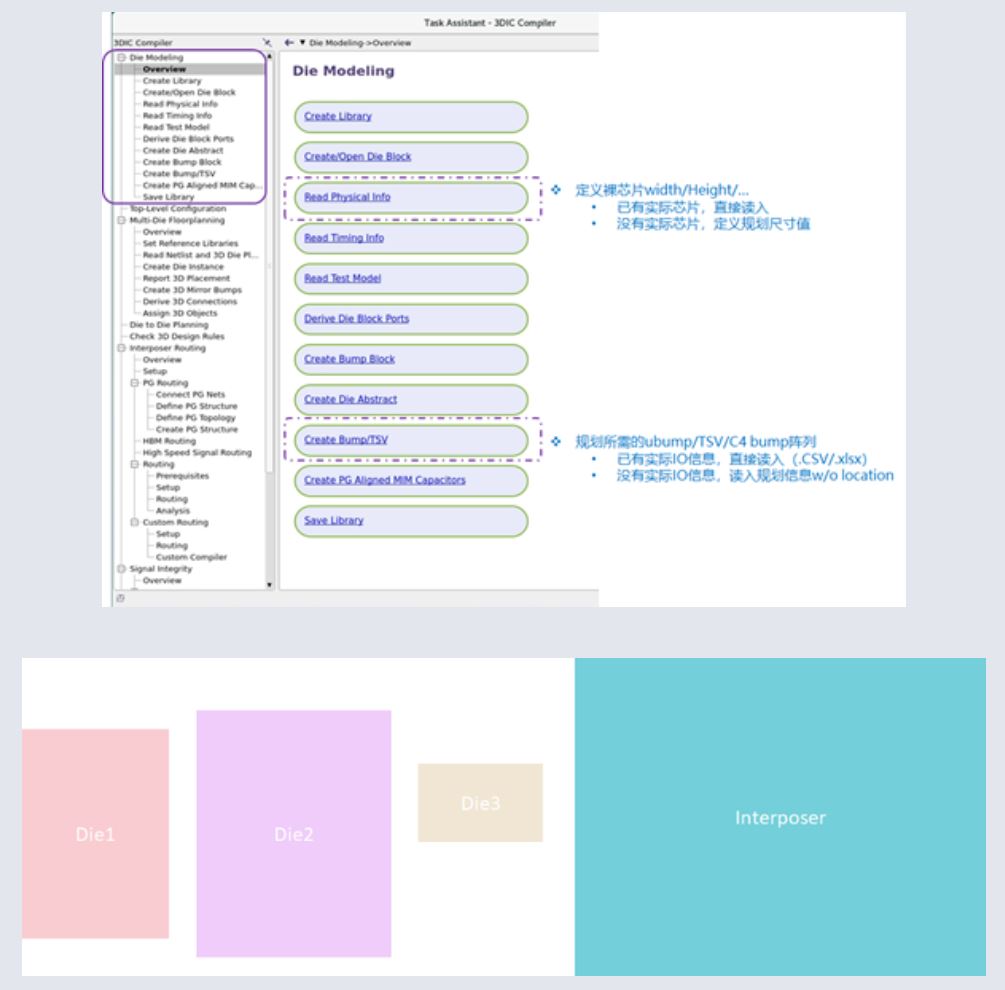

1. Chiplets虚拟原型和顶层创建

创建chiplets虚拟原型,包含长宽尺寸和信号接口规划。

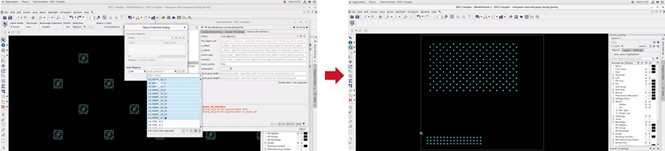

图 2 :虚拟芯片原型创建

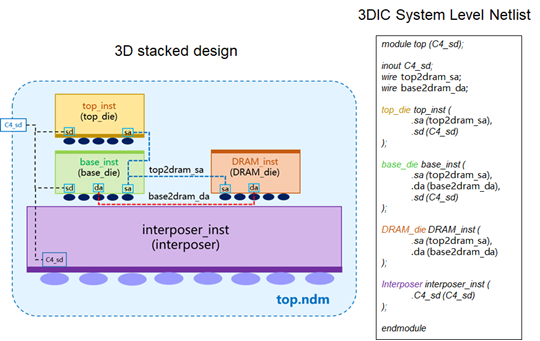

创建虚拟顶层网表,建立芯片间互连关系,包含多芯片系统的所有实例和互连,但不会产生用于生产制造的实际GDS。

图3:虚拟顶层网表创建

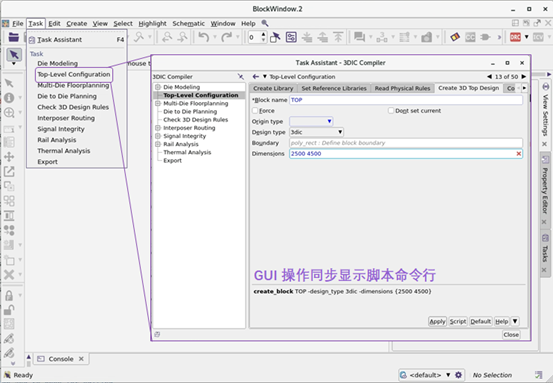

2. 布局堆叠规划

Chiplet多芯片系统架构和布局规划有诸多因素需要考量,如chiplets和IP选择、接口协议和类型、裸片是并排放置还是垂直堆叠等等,选择的确定取决于目标应用在功耗、性能、功能、成本和散热等方面的要求。

3DICC对于系统的架构布局支持多种芯片堆叠方式,如face-to-face、face-to-back等,在布局探索过程中,这些都可以从2D和3D的视图进行交互式设计,快捷直观。

图4:堆叠布局探索

3.Bump/TSV设计规划

在chiplets的架构探索和设计阶段,需要完成系统级Floorplan和各个层次的bump planning。

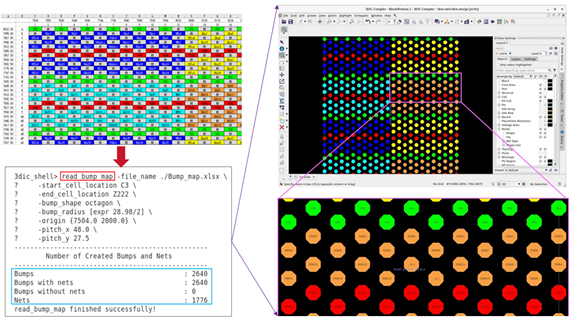

对于ubump、TSV、C4 bump的设计,3DICC支持多种规划方式,包括CSV、Excel表格以及图形界面阵列设计等,可以根据实际的设计条件和需求,选择适合的方式进行。例如:

Die1:已有Excel表格类型IO信息,导入文件自动创建。

图 5:导入excel格式的bump map

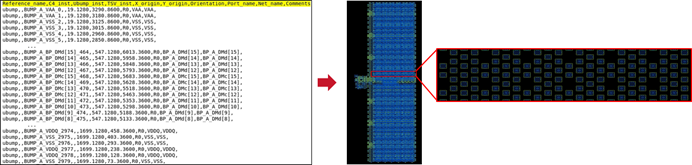

Die2:已有CSV格式IO信息,导入文件自动创建。

图6:FanOut设计顶层创建

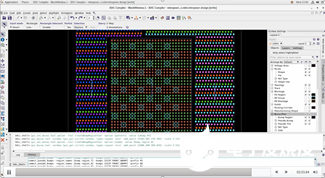

Die3:只有IO信号列表,可以设定区域和pattern创建,也可以由工具基于信号接口关系自动分布创建。

图7:设定区域和pattern创建bump阵列

图8:工具自动分布创建bump阵列

4.PG网络规划和系统早期EMIR Thermal分析

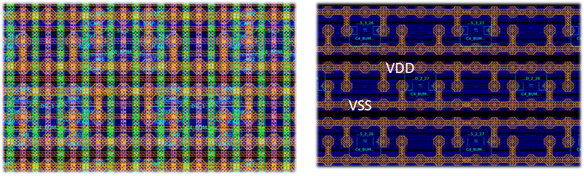

3DICC可以快速建立不同类型和pattern的PG网络,用于支持原型阶段的EMIR和Thermal建模分析。这些结果为PG网络、bump/TSV阵列、芯片热功耗、芯片堆叠方式等设计选择确定提供了必要的数据支持,推进架构探索设计迭代优化。

图9:PG网络实现

图10:EMIR Thermal分析示例

总结

与单片系统相比,chiplet多芯片系统在架构定义阶段,必须通过功能架构、物理架构的协同假设和优化,从整个系统的角度进行设计和验证,问题越早发现,就越有可能做出有影响力的改变来优化整个系统。通常来说,有价值的设计数据通常要到设计流程的后期才能获得,而借助虚拟原型技术,开发者可以更好地掌控功耗和性能,同时仍可以在设计过程中做出修正和优化,从而规划出系统的理想蓝图。

3DIC Compiler提供的基于虚拟原型实现多芯片架构探索,对于多芯片系统的可行性、可优化性和可实现性等方面提供了有效且高效的功能支持。

文章来源:芯和半导体

-

如何基于3DICC实现InFO布局布线设计2023-03-30 4855

-

鸿蒙跨端实践-JS虚拟机架构实现2024-09-30 3995

-

【「DeepSeek 核心技术揭秘」阅读体验】第三章:探索 DeepSeek - V3 技术架构的奥秘2025-07-20 1997

-

多通道RF到位开发平台可实现相控阵的快速原型设计2020-08-21 3020

-

请问虚拟系统原型有什么作用?2021-04-27 1634

-

如何在嵌入式系统或快速原型构建板上实现即交即用式部署?2021-11-22 1485

-

如何在visual studio上实现USB虚拟串口功能?2021-12-07 1449

-

STM32实现虚拟串口功能2022-02-22 1512

-

将 Virtualizer 虚拟原型和 HAPS 系列基于 FPGA 的原型无缝集成2017-02-08 619

-

介绍虚拟机器原型及应用2018-06-25 2257

-

如何在ADIsimRF中建模多級元件2019-08-23 3074

-

带有Android的四核ARM虚拟原型2022-06-19 1845

-

大算力时代,虚拟原型解决方案如何保证SoC架构和性能不掉队?2022-11-10 914

-

如何在3DICC中基于虚拟原型实现多芯片架构探索2023-11-20 1688

-

虚拟桌面基础架构(VDI)远程连接如何实现2024-10-18 1554

全部0条评论

快来发表一下你的评论吧 !