如何在高速设计中通过规则管理来控制阻抗

电子说

描述

本文要点

阻抗不匹配会导致并行网络出现信号反射和不同步现象,从而导致接收器上出现比特错误。

要快速识别阻抗超标,需要在 PCB 设计工具中使用规则管理器,然后在设计规则中设置阻抗限制和容差。

布线后仿真工具可用于检查不符合阻抗规则的网络,并确定哪些区域的设计应该更改。

走线阻抗控制主要在于确保走线的尺寸大小合适。如果独立考虑一条走线,其阻抗值是很明确的。但是,当它靠近另一条走线或导体时,由于意外耦合作用,该走线的阻抗将与最初的设计值不同。这个问题非常棘手,会导致沿着互连的阻抗变化不定,而传输线和接收器之间的极端阻抗失配将导致信号反射。

尽管我们已根据最佳实践对 PCB layout 进行了布线,并且布线的走线宽度全部符合设计值,但是互连中也有可能出现阻抗变化。这时就需要使用规则驱动设计,即,在对 layout 进行布线时,根据设计规则来检查电路板。如果要处理一块工艺比较陈旧的电路板,那么就需要分批检查阻抗;为此,可以运行一个批处理设计规则检查 (DRC),一目了然地浏览阻抗超标情况。

通过规则管理来控制阻抗,准确发现信号反射

要纠正整个电路板上的阻抗错误,Sigrity 的布线后仿真功能可以助我们一臂之力,用以分析整个单端和差分互连的阻抗。同时,还可以发现互连线上特定位置的信号反射,如过孔或连接器过渡处。在下文中,我们将介绍如何使用 Allegro PCB layout 工具和 Sigrity 分析功能。

定义阻抗控制的规则

阻抗控制的目的是确保 PCB 上的走线在每个互连中的几何形状都是一致的。该方法适用于单端和差分对布线。为此,需要遵循我们的高速信号标准来定义这些约束规则,而这些信号标准又取决于所选的器件或设计的接口类型。

PCB 设计软件的适应性很强,确保用户能够定义任何物理和电气规则,以符合可制造性设计 (DFM) 要求和信号标准。Allegro 提供的设计工具允许用户使用 Allegro Constraint Manager(规则管理器)来定义所需的阻抗值和容差。此工具可在 Allegro PCB Designer 或 Allegro Sigrity SI 内访问。

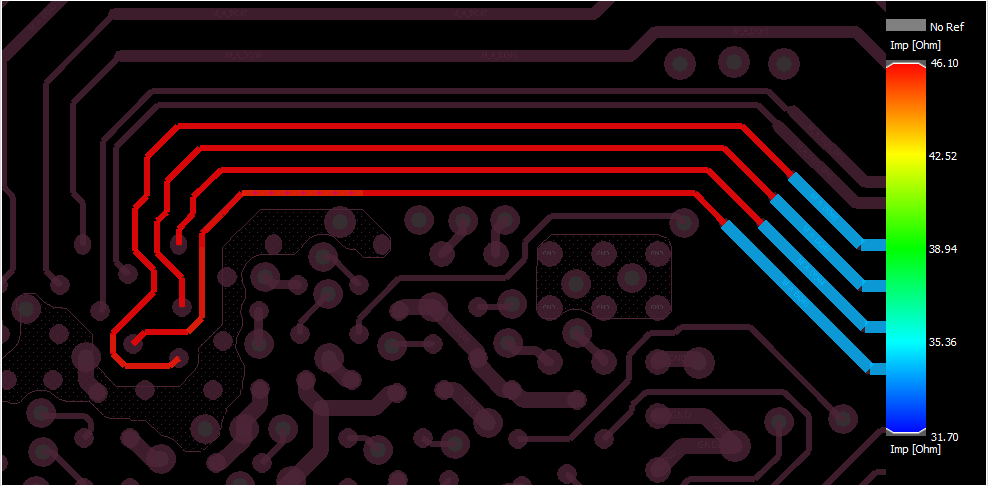

对四个阻抗控制网络进行分析。

在接下来的例子中,我们将讨论如何定义和检查现有 layout 中一组网络的阻抗规则。如上图所示,这四个要检查的网络是 DDR3 数据总线的一部分,定义的阻抗是 34 欧姆。此时,我们要检查这些走线的阻抗是否在 JEDEC 标准的限制范围内,以及在这些走线上是否会发生过度的信号反射。

定义规则

在开始定义规则之前,我们需要确定规则定义是针对单个网络,还是针对一组网络。Allegro PCB Designer 允许用户将几个网络划分到一个网络组,因此可以将同一组设计规则分配至整个网络组。请注意,不是必须要将网络分配到网络组;一个网络也可以有自己的设计规则和约束。所有设计规则都可以在 Allegro Constraint Manager 中访问、查看和编辑。

要访问 Allegro Constraint Manager 并定义电路板中的约束规则,请在 Allegro Sigrity SI 中打开 .BRD 文件。单击 Setup 菜单并找到 Constraints → Constraint Manager。打开 Constraint Manager 后,可以从屏幕左侧的面板上访问基于网络组和基于网络的电气规则。

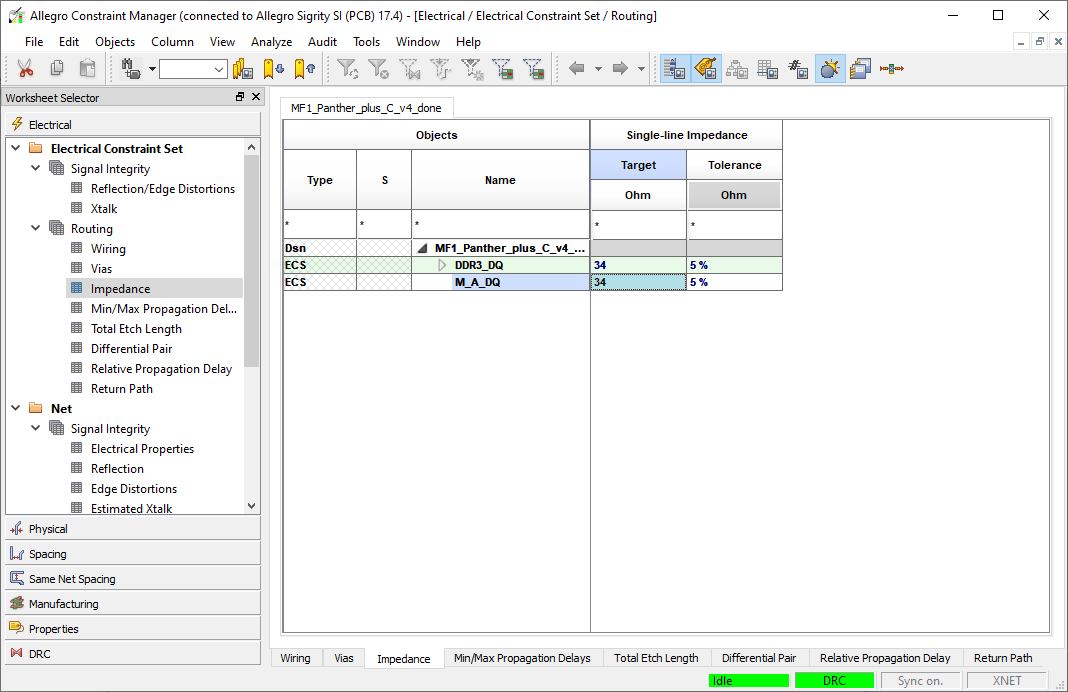

要为一个网络组设置阻抗规则,请打开 Electrical Constraint Set 选项,然后找到 Routing → Impedance。下图是在该电路板上定义的两个网络组。这两个网络组都是 DDR3 接口的一部分,因此该接口上的走线阻抗应该设置为 34 欧姆。阻抗容差设置为 5%。

网络组的阻抗规则。

我们要检查的四条走线不属于这些网络组,但如有需要,我们可以将这些走线分配到这些网络组。另一种方法是在 Electrical Constraint Set 中为这些走线单独定义阻抗规则。为此,只需在 Constraint Manager 中向下滚动到电气工作表中的 Net 部分。打开 Routing → Impedance 部分后,就可以查看所有的网络以及它们属于哪个网络组。

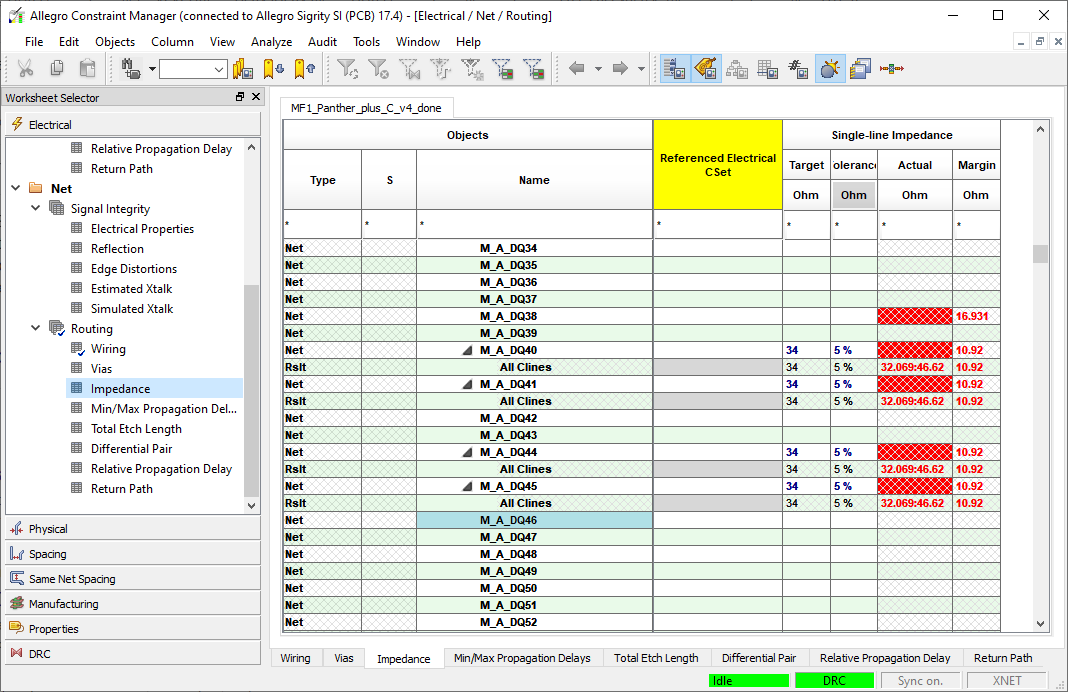

如果我们想把一个网络分配到电气规则集,只需在 Referenced Electrical C Set 一栏下打开下拉菜单,选择所需的电气规则集。现在,我们要把目标阻抗值分配到要检查的各个网络。从下图中可以看到,目标阻抗设置为 34 欧姆,阻抗容差为 5%。定义目标阻抗值之后,我们就会看到相应的网络被标记为红色。如果该网络没有立即显示标记,只需从工具栏运行设计规则检查(在 Tools 菜单下选择 Update DRC)。

各个网络的阻抗规则。

在上图中,这四个网络被标记为了红色,因为它们的最小阻抗和/或平均阻抗超出了 34±5% 的范围(32.3-35.7 欧姆)。Constraint Manager 显示,阻抗范围为 32.069-46.62 欧姆;这些值可能出现在这些网络的任何位置。造成这种现象的原因包括与其他导体产生意外的寄生耦合、走线宽度不一致,或在参考平面的间隙上进行布线。

请注意,Allegro Constraint Manager 还支持为 PCB 定义其他几种物理和电气规则。物理规则包括焊盘和走线间距,而电气规则包括传播延迟限制和返回路径跟踪。

确定违反设计规则的网络之后,就可以进一步了解到底是设计的哪些部分导致设计规则超标。另一种查看规则超标的方法是使用工具菜单中的 DRC Browser。该工具可以显示电路板中超出设计规则的坐标,并在不同的类别中标记出具体的规则超标项目。超标列表可能让人有点眼花缭乱,但不必担心,Allegro 提供了可视化工具来显示规则超标。这涉及到使用 layout 数据进行布线后仿真。

运行阻抗和反射仿真

现在,我们已经准备好纠正电路板中的阻抗失配,要完成此操作,可以使用 Allegro 中的信号完整性分析功能来发现阻抗变化并识别存在反射的位置。

在 Allegro 中打开电路板,点击 Analyze 菜单,并选择 Workflow Manager 选项。随后屏幕上会显示几个可供执行的分析,包括 Impedance Workflow 和 Reflection Workflow。

首先,选择 Reflection Workflow 和要检查的目标网络。选择目标网络后,点击 Start Analysis,开始仿真。仿真完成后,可以点击 Reflection Vision查看热图,热图中标出了网络上出现反射的位置。我们也可以点击 Reflection Table 来查看具体的上冲/下冲值以及它们在电路板上的坐标。在本例中的电路板上处理的是 DDR 线路,因此可以在 Reflection Table 中将这些值与 JEDEC 规范进行比较。

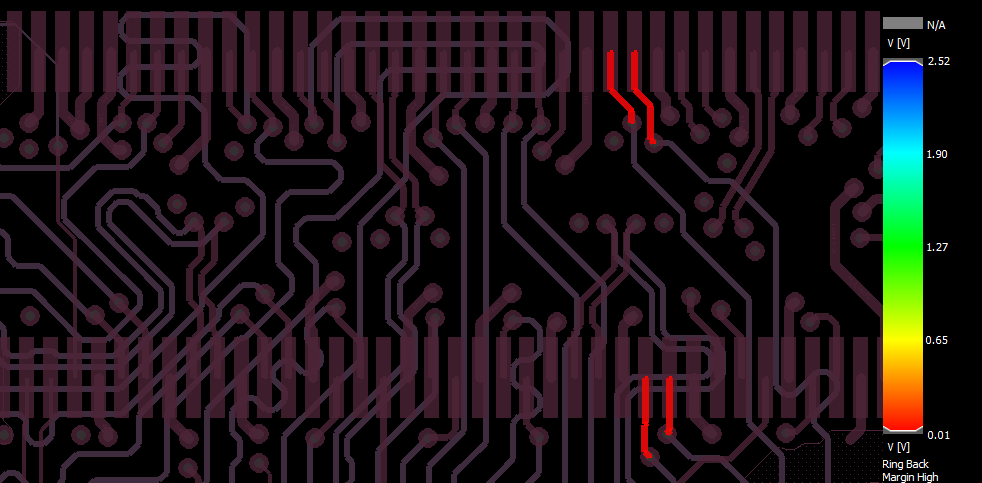

下图是本例中四个网络的反射结果。从图中可以看到,反射主要发生在器件焊盘上。相应的值以红色标记,并且只产生了约 10 mV 的振铃现象。在互连上很早就可以看到 30 mV 的振铃,但用 Reflection Vision 工具不容易进行可视化;需要双击阻抗表中的相应条目才能看到这些结果。

Reflection Workflow 结果。

沿着这些网络出现了 30 mV 的振铃,它们发生在靠近走线的多个点附近,相应的走线片段如之前的图片所示。Impedance Workflow 分析有助于理解这些反射现象,它们是由沿互连线的阻抗变化而引起的,以可视化的方式查看会更为直观。

要检查阻抗变化,请选择分析工具栏中的 Impedance Workflow 选项。选择相同的网络进行分析并运行仿真。选择 Impedance Vision 选项,可以查看整个互连的阻抗,同时也会显示热图,其中阻抗值以不同的颜色表示。

四个网络的阻抗变化。

从图中我们可以直接看到,阻抗从约 46 欧姆突然过渡到约 34 欧姆,和 Allegro Constraint Manager 中显示的数据相同。从红色部分和蓝色部分之间的长度变化可以明显看出这一点。这对应于网络中具有较高上冲的区域。下一步是将信号上冲和阻抗变化与信号标准进行比较。这些网络的红色部分对应 FPGA 上的 BGA 扇出部分,所以要限制扇出部分的宽度,防止出现过度的信号反射和损失。

我们可以采用与上文相同的仿真步骤来检查电路板中的不同网络对。只需选择网络对的两端,确保整个电路板的差分阻抗保持一致。对于差分对,还需要检查是否符合长度匹配容差,该容差可以在 Allegro Constraint Manager 中定义。然后可以使用 DRC Browser 来确定哪里发生了长度失配的情况,布线工具可以对标准的长度匹配片段进行布线,保持差分对同步。

本文转载自: Cadence楷登PCB及封装资源中心微信公众号

审核编辑 黄宇

-

什么是阻抗匹配?高速PCB设计为什么要控制阻抗匹配?2023-10-30 4304

-

高频高速PCB设计中的阻抗匹配,你了解多少?2023-05-26 1394

-

高速信号的走线闭环规则2023-05-22 2625

-

EMI问题可以通过高速PCB来控制解决吗2021-12-31 1504

-

高速PCB布线技巧、EMI问题、设计规则2021-03-31 8053

-

使用阻抗控制来管理PCB信号完整性2020-10-09 2331

-

如何通过高速PCB来控制EMI问题2019-06-05 1168

-

如何用S12ZVM来控制高速电机(二)2018-06-28 4122

-

解决高速PCB设计EMI(电磁干扰)的九大规则2017-11-02 2975

-

高速PCB设计解决EMI问题的九大规则2016-01-19 4226

-

高速pcb设计中,阻抗失配2014-10-24 3261

-

关于高速设计中的阻抗匹配的问题2010-03-15 1711

全部0条评论

快来发表一下你的评论吧 !