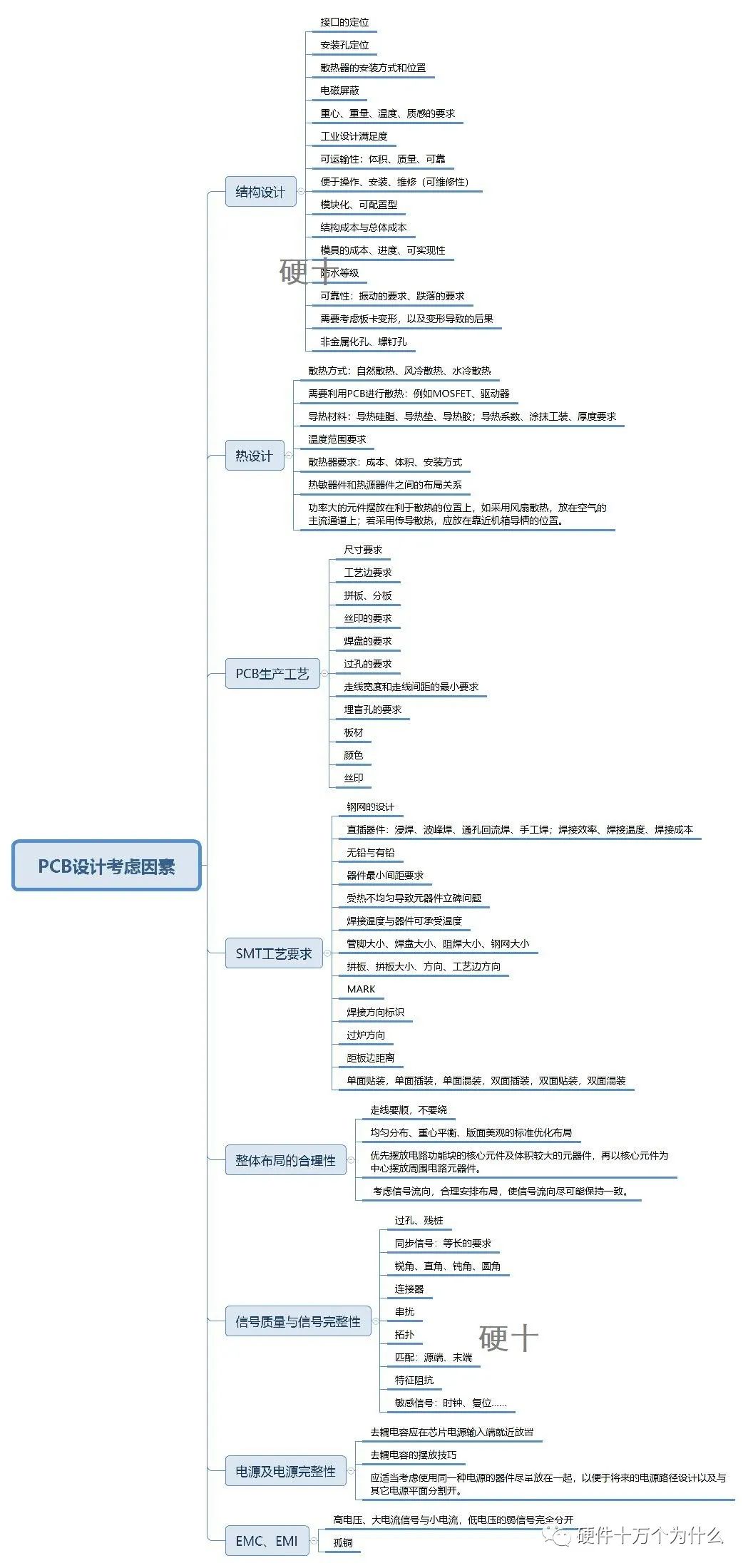

一张图看懂“PCB设计考虑的因素”

电子说

1.4w人已加入

描述

| 项目 | 检查内容 | Y/N | 备注 |

| 常规类检查项 | 禁止布局布线区域设置是否正确。(注意限高区)增加:晶振,电感,变压器下方画好禁布区。 | ||

| 结构是否更新正确,螺孔大小,接口定位与方向是否正确。对于有疑问的接口方向有没有与结构工程师确认? | |||

| 结构是否是最终文件。 | |||

| 封装是否经过检查。 | |||

| 改版设计时,封装是否检查并更新(原点变化导致固定器件偏位等) | |||

| 有出差工程师自建或临时替换的封装有没有进行复查和更正 | |||

| 光绘设置是否正确。 | |||

| 每种电源是否都有来源,宽度是否都满足载流量。过孔数量是否足够。 | |||

| 原理图和PCB文件网表否是最新的,导入是否一致 | |||

| 是否有未摆器件、是否有未连接网络、是否有多余线段 | |||

| IPC网表是否对比、并确认没有断路和短路存在 | |||

| 规则设置 | 叠层设置是否正确。(包括正负片)是否有按增加的工艺制作说明进行规则设置 | ||

| 差分线、单端线等线宽、线距规则设置是否正确。 | |||

| 高电压安规设置是否正确。 | |||

| 等长误差与最大长度设置是否正确。 | |||

| 保护地是否设置2mm以上间距。 | |||

| 是否有把相同分类的网络全部分配到对应的分组。 | |||

| 相应规则是否打开。 | |||

| 如果有隔离盘花焊盘,是否设置正确。 | |||

| 布局 | 确保结构限高区没有摆放超过限制高度的器件。 | ||

| 有顺序要求的(如LED,按键)是否符合结构要求摆放。 | |||

| TVS、ESD保护器件是否靠近接口放置。 | |||

| 数字、模拟、高速、低速部分是否分开布局。模拟布局是否保证主通路走线最短。 | |||

| 相同模块是否相同布局。 | |||

| 源端与末端匹配器件布局是否正确。 | |||

| 晶体、晶振及时钟驱动器摆放是否合理。 | |||

| 开关电源是否按要求布局布线。(回路是否最小,是否做单点接地) | |||

| 每种电源电压电容是否均匀分布。(0.1uf以下小电容每个电源管脚有一个)。 | |||

| 热敏感器件是否远离电源和其他大功耗的元件(测温器件是否放在合适的位置)。 | |||

| 绕线电感是否有平行摆放一起。(建议相互垂直摆放) | |||

| 射频电路是否考虑一字型或者L型布局。 | |||

| 隔离器件(如变压器)前后部分器件要分开布局。 | |||

| 发热量大的器件也要相互分开,方便散热。 | |||

| 确保禁布区没有放置器件。 | |||

| 布线 | 锁相环电路,REF,电感两端走线是否加粗。 | ||

| 信号或者电源孔密集处是否增加回流地孔。 | |||

| 电源引脚出线是否都有20mil以上或同引脚一样宽。(包括热焊盘,上下拉电阻除外) | |||

| 所有关键信号线走线,是否有跨相邻平面层分割。 | |||

| 射频线与天线是否处理正确(加粗控50ohm阻抗,并加上相应的参考面,陶瓷天线按要求挖空,射频线周边加屏蔽地过孔。) | |||

| 模拟走线和不要求阻抗的线(如晶体时钟线,Reset等)是否加粗8mil以上。 | |||

| 是否存在多余过孔和线,多余残桩(Stub)走线。 | |||

| 是否存在直角和锐角走线。 | |||

| 是否存在孤铜和无网络铜。 | |||

| 有极性器件是否正确。(特别注意二极管、极性电容、ESD、LED等) | |||

| 布线拓朴结构是否合理。 | |||

| 隔离器件(光耦、共模电感、变压器等)是否做隔离或挖空处理。 | |||

| 静电保护地,保护地与工作地是否已做隔离设计(至少相隔2.5mm) | |||

| 电源模块、时钟模块是否有信号线走过,特别是开关电源电感下不能穿线。 | |||

| 相邻信号层是否有平行走线。平行走线必须错开或者垂直走线,不可以重叠。 | |||

| 差分线和重要信号线换层处是否加有回流地过孔。最好对称加上两个回流地孔。 | |||

| 对敏感信号是否进行了地屏蔽处理,每500mil是否有一个过孔。 | |||

| 多层板板边是否每150mil加有屏蔽地过孔。 | |||

| 平面层是否有通孔隔离盘过大造成平面割断导致电源平面电流不足。 | |||

| 电源平面与地平面比较是否有内缩。 | |||

| 平面层各块电源网络是否都有花盘连接。 | |||

| IC与连接器是否都有电源和地管脚且加粗走线。 | |||

| 发热量大器件铺铜面积是否足够大。是否在表层有加上散热开窗的铜皮。 | |||

| 金手指上是否有铺铜,内层铺到金手指焊盘的一半的位置,金手指上是否有整块阻焊。 | |||

| 器件(电阻电容电感等)引脚中间是否有过线。 | |||

| 表层空白处是否有铺铜处理。 | |||

| 两层板正反面地是否连接良好。特别注意电源和地在换层的地方过孔是否满足载流能力。 | |||

| 串口芯片(例如232、485、429、422)部分电容走线是否加粗。 | |||

| 时钟电路(包括晶体、晶振、时钟驱动器等)的电源是否进行了很好的滤波,对于时钟走线不能残桩(Stub)。 | |||

| 做等长时,是否确保每个信号分组中的每一根网络都做到的等长。 | |||

| 重要信号线是否优先布线,走在最优布线层。 | |||

| 电源平面压差较大时,隔离带是否相应加宽。 | |||

| 同组高速信号线的过孔数是否最少且个数一致,尽量小于2个过孔。 | |||

| 输出产生文件检查 | 确定SMT器件是否有开钢网和所有器件开阻焊层。 | ||

| 阻焊开窗是否与表层铺铜一致。 | |||

| 确定器件字符及丝印标示方向是否正确,是否有干涉和文字错误上焊盘现象,器件1脚标示是否正确明显。 | |||

| 走线线宽是否与生产说明一致。 | |||

| 非金属化孔焊盘是否设置正确。 | |||

| 板上标注是否正确。(包括Drill层说明及误差标注) |

文章来源: 硬件十万个为什么

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- PCB设计

-

PCB图复制到另一张图纸 怎么解除警告2016-06-09 6597

-

原创|高速PCB设计中层叠设计的考虑因素2017-03-01 4121

-

一张图看懂阿里云网络产品[二] 专有网络VPC2018-01-08 4332

-

对存在的一张RGB图像将其变换成一张灰度图的方法2019-04-03 4042

-

在PCB设计中应该考虑哪些因素2019-06-12 1564

-

PCB设计应考虑哪些因素2021-03-04 1715

-

如何读懂一张电路图?电源电路怎么看懂?2021-03-05 4277

-

一张图看懂USB充电协议2021-09-15 3832

-

PCB布板时考虑的因素2021-12-28 1699

-

一张图看懂ERP和MES的区别分析资料下载2018-01-04 1269

-

一张图看懂阿里云网络产品【十四】IPv6转换服务2018-08-15 565

-

PCB设计的成本考虑因素是什么?2020-09-12 4469

-

一张图看懂STM32芯片型号的命名规则2021-12-02 4450

-

一张图看懂中软国际2023中期财报2023-08-17 1814

-

一张图看懂睿创微纳2023年年报2024-04-23 1237

全部0条评论

快来发表一下你的评论吧 !