磁环在EMC中的妙用

电子说

描述

作者: 金耀光,来源: 韬略科技EMC微信公众号

前言

在电子产品的设计中,电磁兼容EMC性能对系统的影响非常大,关系到其能正常稳定运转。很多国家现在已经开始对电子产品的电磁兼容性做强制性限制,电磁兼容性能已经成为产品性能的一个重要指标。

电磁兼容主要有两方面的内容,一个是产品本身对外界产生不良的电磁干扰影响,称为电磁干扰发射EMI;另一个是对外界电磁信号的敏感程度称为电磁敏感度EMS。干扰源、耦合途径及敏感设备是电磁兼容的三要素,缺一不可。在整改过程中我们有时候经常采用到磁环来排查问题,但是使用过程中我们不知道哪些细节会影响使用的效果。

磁环的作用

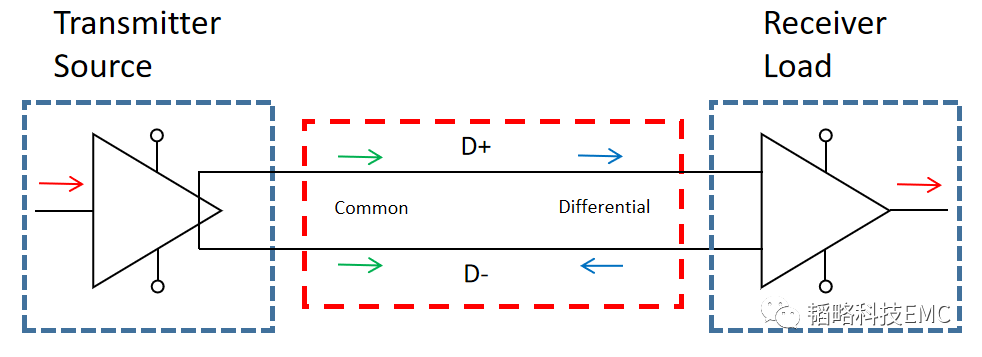

图1 USB接口信号传输

上面图1是USB接口信号传输的等效电路,假设信号传输过程中存在两种噪声,绿色信号的走向是共模噪声,蓝色信号走向是差模噪声。因此在整改过程中我们将磁环绕在USB信号线上来抑制噪声,并对比前后的效果。

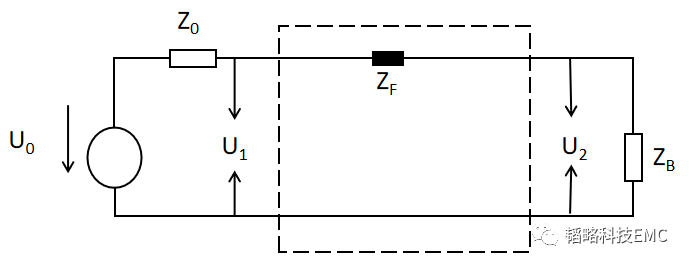

图2 绕磁环等效电路

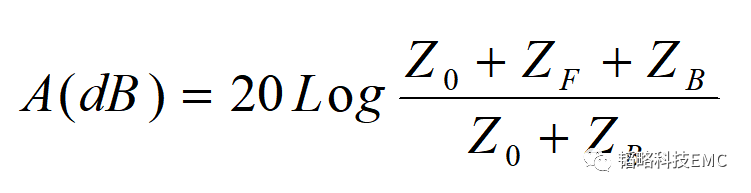

上面图2是绕磁环等效电路,电路上的ZF是绕磁环后在电路上的等效阻抗,Z0是信号源的内阻,ZB是负载,那么我们可以根据下面的公式计算出磁环的插入损耗,这样就可以选出合适的磁环来降低噪声满足实验限值的要求。

图3 插入损耗计算公式

影响磁环抑制噪声效果的因素

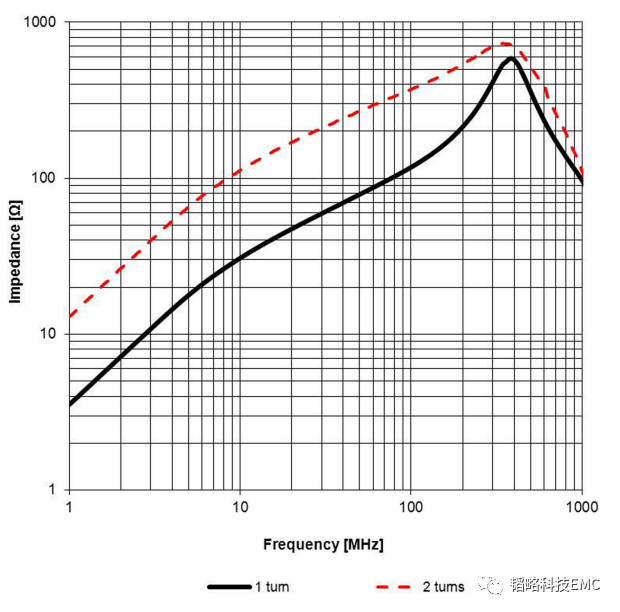

1. 绕线的匝数

一般磁环的规格书上面都会给出这样的匝数的频率阻抗曲线,从图4可以看出当线绕一匝时100MHz对应下的阻抗大约110Ω,而当线绕到两匝时可以看出100MHz对应的阻抗大约390Ω,而且两匝的整个曲线都偏上,因此在整改过程中绕的匝数也是比较关键的,不然加上磁环达不到我们想要的效果。

图 4 不同匝数的频率特性阻抗曲线

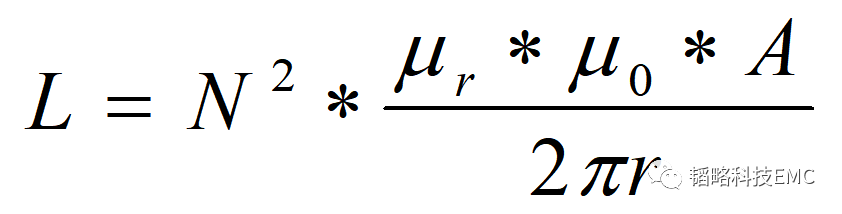

那么当规格书上面没有这样的曲线时,我们可以根据以下的公式进行计算,当磁环上绕了线之后我们可以将其等效成一个电感,其中N为绕线的匝数,μr是磁环的磁导率,μ0是初磁导率,A是磁环的截面积,r是外圈到中心的半径,因此根据公式可以计算出我们想要的磁环参数。

图 5 磁环感量的计算公式

2. 磁导率

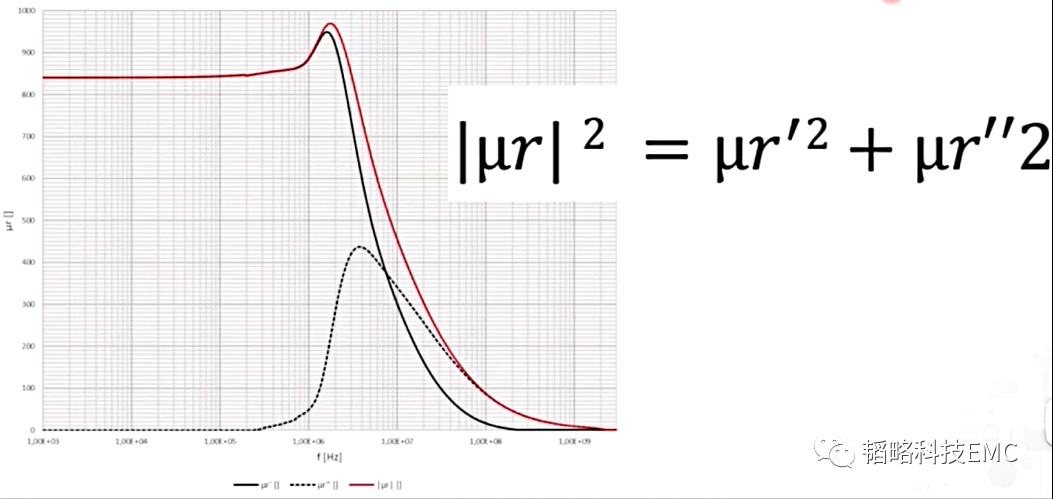

图 6 磁导率

由上图6可以看出磁导率是分为虚部和实部两部分,红色的曲线是实际的磁导率,黑色的实线是磁导率的实部,黑色虚线是磁导率的虚部。当频率达到上GHz时,磁导率的值几乎降低到零了,所以当选择磁环时要考虑到超标频率对应磁导率的变化。

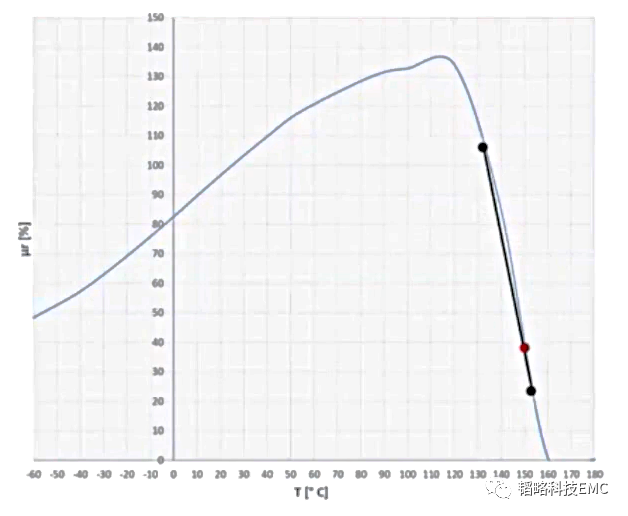

3.居里温度

图 7居里温度曲线

简单来说,这居里温度是让磁环内部的磁畴解体的温度,可以从图7看出磁导率随着温度的升高逐渐达到一个高点,该高点对应的温度是120℃,当温度再升高时磁导率开始急剧下降,下降到磁导率变为1时,该磁环没有了磁性。不同的磁环有不一样的居里点,因此当使用磁环在高温环境下时,我们要考虑磁环的居里温度的影响,这样保证磁环的有效性。

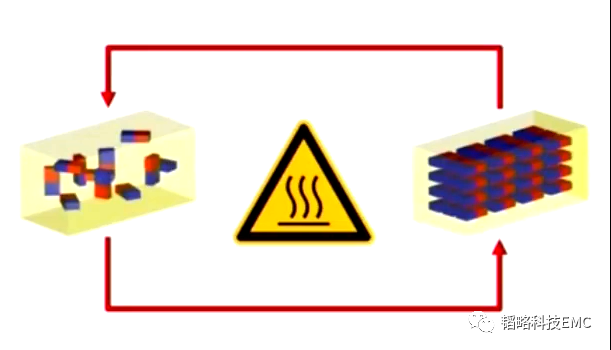

4. 通流大小

图 8 磁环内部磁畴的分布图

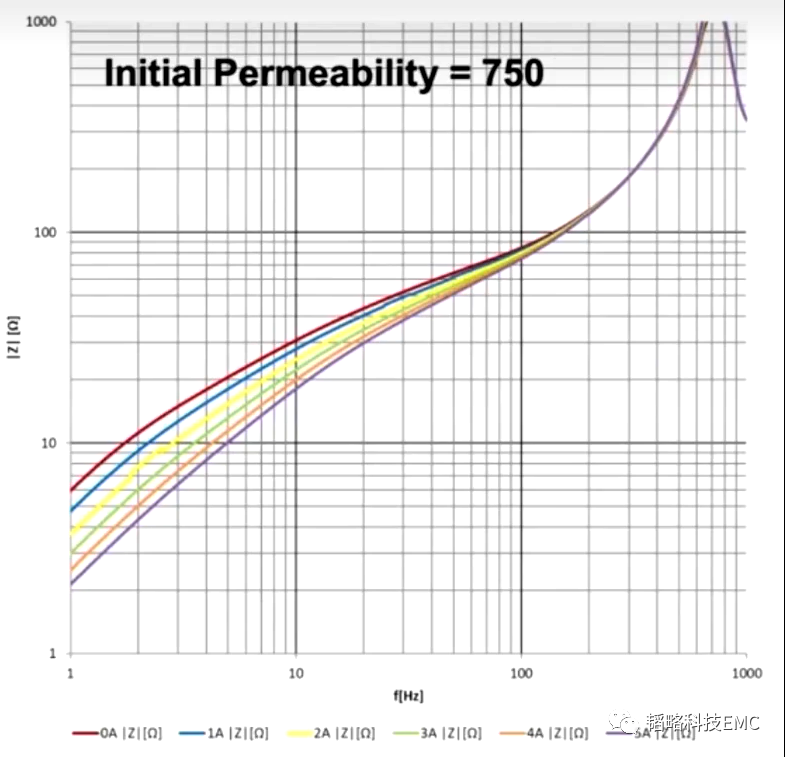

图 9 电流频率阻抗曲线

图8是磁环内部磁畴的分布情况,当磁环没有磁场时磁畴的分布是一个无序的状态,而施加磁场时磁畴变成一个有序的状态,那么电流增大时磁场强度也随之增强,这样磁畴的排列就更加的紧凑,有序的磁畴更加的多,通过的磁感线就变得越密集,所以磁环的阻抗就随之增大。由图9的电流阻抗曲线可以看出,磁环的初始磁导率为750H/m时,在低频情况下电流由0安逐渐增加到5安,阻抗的差异会比较明显,到高频时电流变化时阻抗变化不大。

5. 气隙

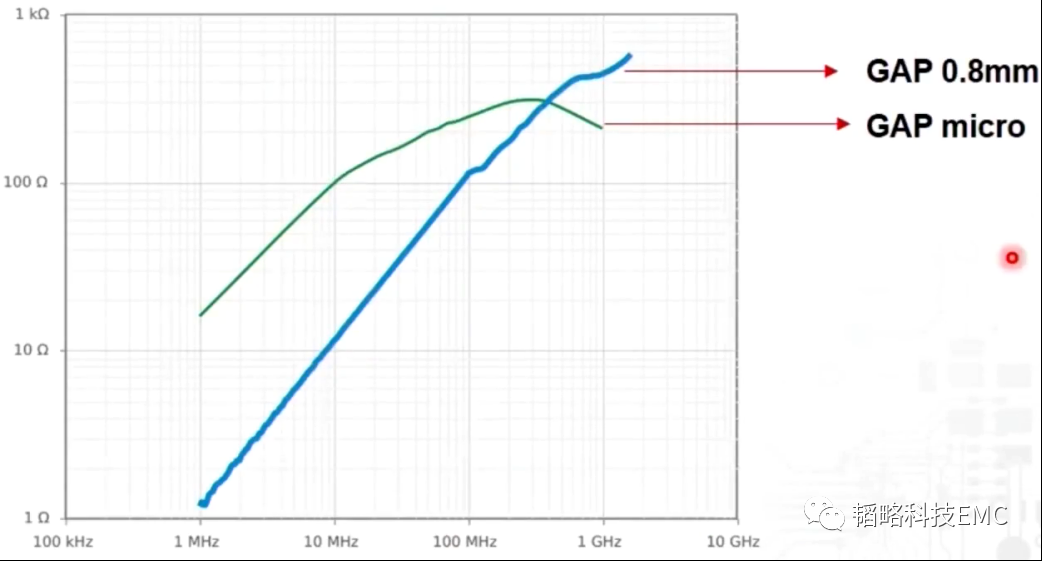

图 10 频率特性阻抗曲线

如图10可以看出一款气隙0.8mm的夹扣式磁环随着频率的不断增加阻抗接近直线上升的趋势,到达上1GHz了阻抗还是增大状态。而micro扁平磁环随着频率的增加会达到一个最高点,频率再增加时阻抗会下降,尤其是频率达到1GHz的时候。因此在我们想要抑制高频的噪声时可以选择夹扣式的磁环进行抑制噪声。

POC电感参数对比和测试

总的来说,对于磁环的使用一般会在消费类产品上看见,由于外接这种磁环外观不是很好看,所以很多产品都会取消采用其他的滤波方式去抑制噪声,如共模电感、差模滤波器等,但是对于磁环的使用,我们可以在整改过程中用来排查问题,这样比较有效、快速的锁定噪声传播路径,因此使用磁环时可以参考以上的几点影响因素,可以规避一些额外的影响。

审核编辑 黄宇

-

铁氧体磁环妙用解决某产品辐射超标整改案例2022-10-11 8015

-

磁环在EMC中的妙用 #磁珠 #电磁兼容EMC #EMI #硬件工程师 #电子技术 #电子元器件深圳市韬略科技有限公司 2025-08-14

-

磁环在EMC中妙用2020-09-17 2647

-

产品和EMC整改的最常见的器件—磁环2023-03-29 1510

-

磁环电感在EMC电路中的作用是怎样的2021-06-29 2948

-

EMC磁环在EMC产品中的作用是怎样的2022-04-27 6224

-

磁环在EMC中的妙用有哪些呢?2023-04-18 2674

-

磁环选型的攻略和EMC整改的技巧2023-10-25 2789

-

磁环材质对EMC性能的影响2023-11-13 2330

-

EMC磁环的整改技巧2023-12-21 2609

-

EMC磁环厂家:电磁干扰的隐形守护者2024-07-01 1288

-

电源EMC测试不过,加磁环or不加磁环,如何选择?2025-03-27 5730

全部0条评论

快来发表一下你的评论吧 !