功率MOSFET零电压软开关ZVS的基础认识

电子说

描述

作者:刘松 来源:松哥电源

高频高效是开关电源及电力电子系统发展的趋势,高频工作导致功率元件开关损耗增加,因此要使用软开关技术,保证在高频工作状态下,减小功率元件开关损耗,提高系统效率。

功率MOSFET开关损耗有2个产生因素:

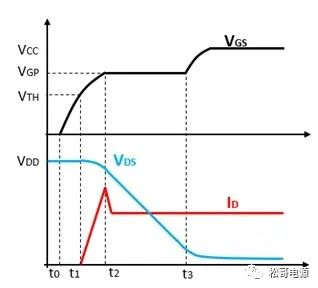

1)开关过程中,穿越线性区(放大区)时,电流和电压产生交叠,形成开关损耗。其中,米勒电容导致的米勒平台时间,在开关损耗中占主导作用。

图1 功率MOSFET开通过程

2)功率MOSFET输出电容COSS储存能量在开通过程中放电,产生开关损耗,高压应用中,这部分损耗在开关损耗中占主导作用。

功率MOSFET零电压开关ZVS是其最常用的软开关方式,ZVS包括零电压的开通、零电压的关断,下面介绍这二个过程的实现方式。

1、功率MOSFET零电压的开通

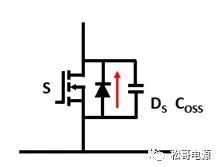

功率MOSFET要想实现零电压的开通,也就是其在开通前,D、S的电压VDS必须为0,然后,栅极加上VGS驱动信号,这样就可以实现其零电压的开通。在实际的应用中,通常方法就是利用其内部寄生的反并联寄生二极管先导通续流,将VDS电压箝位到0,然后,栅极加VGS驱动信号,从而实现其零电压的开通。

图2 功率MOSFET体二极管导通

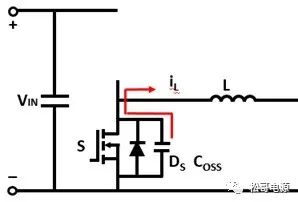

功率MOSFET开通前,COSS电压VDS为一定值,因此COSS电容储存了能量。为了将VDS放电到0,而且不损耗能量,就必须用一些外部元件,将COSS电容储存的这部分能量,抽取并转移到外部元件中。能够储存能量的元件有电容和电感,因此,最直接的方法就是:通过外加电感L和COSS串联或并联,形成谐振电路(环节),LC谐振,COSS放电、VDS谐振下降到0,其储存能量转换到电感中。此时,电感电流不能突变,要继续维持其电流的方向和大小不变,这样,功率MOSFET反并联寄生二极管导通续流。

图3 LC谐振

功率MOSFET反并联寄生二极管导通后,VDS电压约为0,在其后任何时刻开通功率MOSFET,都是零电压开通。因此,功率MOSFET零电压开通逻辑顺序是:

LC电路谐振-->COSS放电、VDS电压下降-->VDS电压下降到0、功率MOSFET体二极管导通箝位-->施加VGS驱动信号,MOSFET导通,电流从功率MOSFET体二极管转移到其沟道-->电流从负向(S到D)过0后转为正向(D到S)。

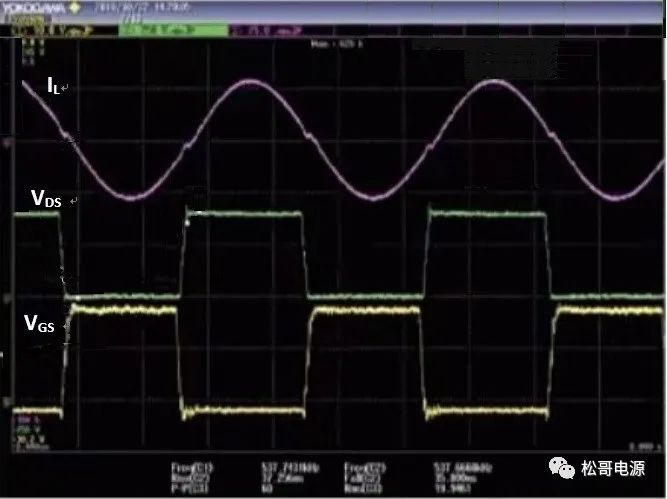

图4 零电压开通波形

2、功率MOSFET的零电压关断

从字面上来理解,功率MOSFET零电压关断,应该就是VDS电压为0时,去除栅极驱动信号,从而将其关断。事实上,功率MOSFET处于导通状态,VDS电压就几乎为0,因此,可以认定:功率MOSFET在关断瞬间,本身就是一个自然的零电压关断的过程。

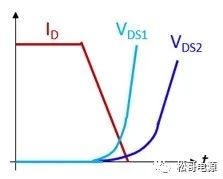

然而,功率MOSFET关断过程中,VDS电压从0开始上升,ID电流从最大值开始下降,在这个过程中,形成VDS和ID电流的交叠区,产生关断损耗。为了减小VDS和ID交叠区的损耗,最直接办法就是增加VDS上升的时间,也就是在D、S并联外加电容,降低VDS上升的斜率,VDS和ID交叠区的面积减小,从而降低关断损耗,如图5所示。VDS2为外部D、S并联电容的波形,VDS2上升斜率小,和ID电流的交叠区的面积也变小。

图5 不同COSS电容的VDS波形

早期的全桥移相电路、LLC电路以及非对称半桥电路中,通常在上、下桥臂的功率MOSFET的D、S都会外部并联电容,就是这个原因。

功率MOSFET的D、S外部并联电容,可以降低其关断过程中VDS和ID交叠产生的关断损耗,但是,额外的外部电容,需要的更大变压器或电感电流,来抽取这些电容储存能量。这样,在变压器或电感绕组和谐振回路中,产生更大直流环流,回路导通电阻就会产生更大的直流导通损耗;此外,外部并联电容还会影响死区时间的大小,所以,要在二者之间做折衷和优化处理。

从上面分析可以得知:功率MOSFET的ZVS零电压软开关工作,重点在于要如何实现其零电压的开通,而不是零电压的关断。

审核编辑 黄宇

-

看了那么多书,第一次有人把ZVS(零电压开通)说的那么简单通透2025-04-08 1196

-

零电压开关与零电流开关的区别2024-07-25 8810

-

什么是软开关?LLC电路是如何实现软开关的?2023-10-26 7287

-

LLC电路的ZVS零电压开通2023-03-20 6582

-

零电压电流开关相关资料分享2021-10-29 873

-

ZVS软开关推挽直流变换器2021-08-31 1584

-

请求各位大佬解释下ZCS和ZVS软开关的工作原理。2021-06-04 4340

-

输出反灌电流零电压软开关反激变换器2021-05-21 3927

-

ZVS软开关技术的原理及如何设计升压电路图2018-10-30 10360

-

MOSFET寄生电容对LLC串联谐振电路ZVS的影响2018-07-13 5785

-

零电压转换脉宽调制软开关功率变换器2018-01-24 1517

-

如何自制最简单zvs升压电路图?其操作步骤解析2017-11-14 185427

-

零电压开关谐振功率变换2017-06-09 1114

-

新型ZVS 软开关直流变换器的研究2009-06-19 821

全部0条评论

快来发表一下你的评论吧 !