高速DAC相位噪声从何而来?首要的原因原来是它……

电子说

1.4w人已加入

描述

问:时钟噪声对于高速DAC相位噪声的影响

在电路设计中,DAC时钟通常是DAC中产生相位噪声的首要原因。为什么这么说?本文将来做一些探讨。

时钟相位噪声的产生

时钟决定何时发送下一样本,故相位(或时序)中的任何噪声都会直接影响输出的相位噪声。

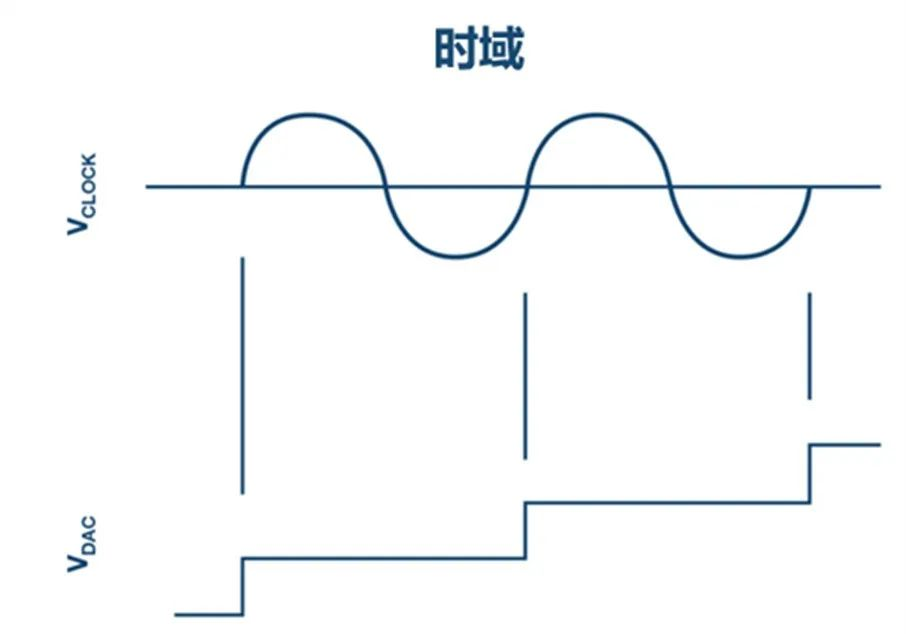

图 1:时钟与相位噪声的相关性

如上图所示,时钟对相位噪声的影响,可以视作各相继离散值与一个矩形函数相乘,其时序由时钟定义。

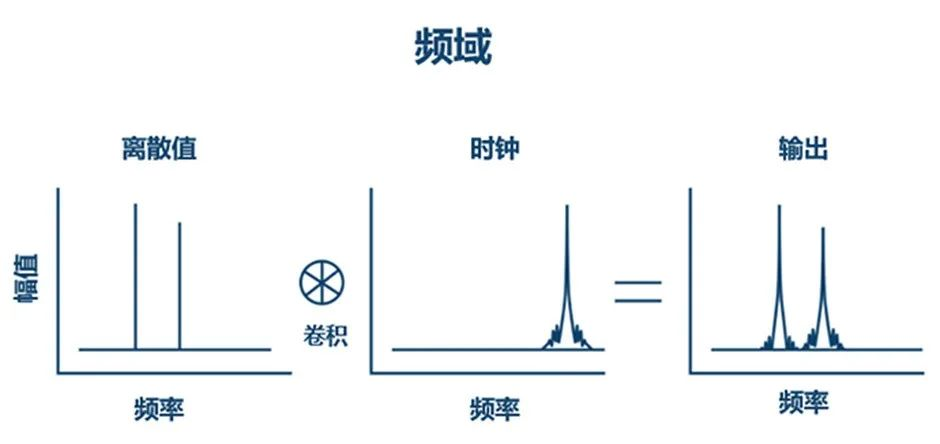

图 2:相位噪声卷积

如上图所示,在频域中,乘法转换为卷积运算。结果,期望的频谱被时钟相位噪声所破坏。这就是整个时钟相位噪声的产生的过程。

信号频率与相位噪声

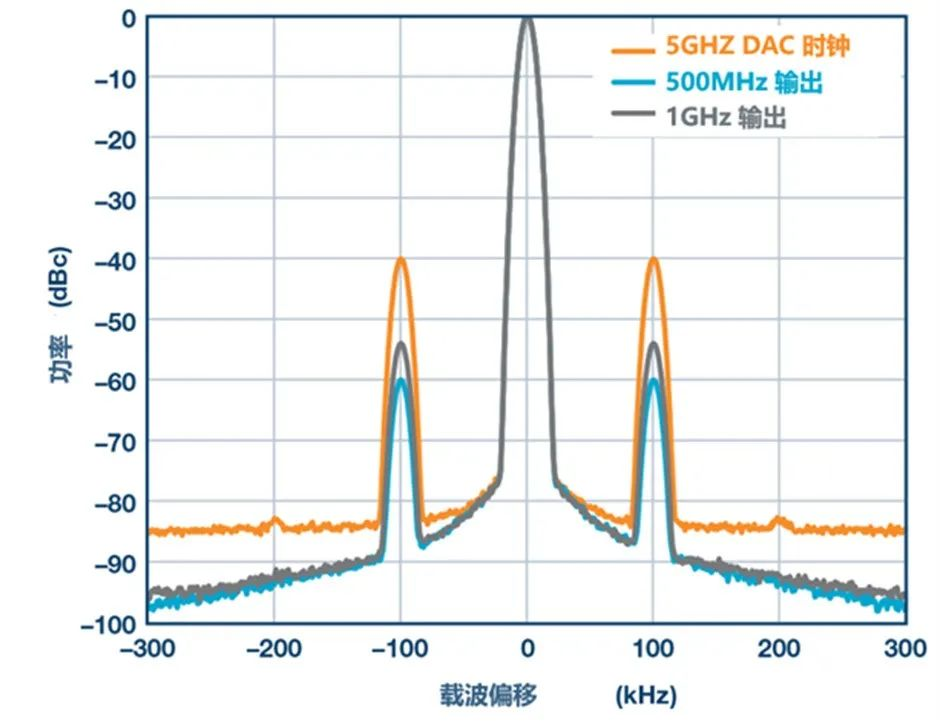

根据信号频率与时钟频率之比,相对于载波的噪声放大或缩小。信号频率每降低一半,噪声改进6dB。为了证明这一点,下图是不同频率(5GHz,1GHz,500MHz)下,混入一个带有轻度100kHz相位偏移的调制时钟信号(精密受控),来模拟相位噪声,来看看信号频率与相位噪声的关系。

图 3 :带100kHz相位调制的时钟输出相位噪声 (图片来源:ADI)

我们可以看到,从5GHz时钟到500 MHz DAC输出观测到20dB降幅,从500MHz输出到1GHz输出观测到6dB增幅。

时钟噪声对于DAC相位噪声的影响很大。选择一个高精度的晶振可能是最简单的方案。

文章来源:得捷电子DigiKey

审核编辑 黄宇

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理2017-05-10 6856

-

电源噪声和时钟抖动对高速DAC相位噪声的影响分析及管理2018-10-17 4429

-

当堆栈被配置为空Mac地址时,无法理解Mac地址从何而来2019-09-20 1460

-

电子产品的音频噪声从何而来呢?2021-07-15 1457

-

STM32CubeIDE生成的固件文件字节从何而来2022-12-08 755

-

SAI模块输出不包括WS信号,RT1024上的WS从何而来?2023-03-21 616

-

时钟噪声对于高速DAC相位噪声的影响2022-07-28 1835

-

电源噪声对于高速DAC相位噪声的影响2022-08-18 1920

-

步进电机的噪音从何而来 如何使步进电机完全静音2022-09-07 5790

-

高速DAC相位噪声从何而来?2022-11-10 1276

-

嵌入式系统上的软件从何而来2022-11-11 1269

-

ADC的噪声从何而来?2023-04-30 3058

-

ADC噪声:从何而来?2023-06-30 1755

-

什么是相位噪声 产生相位噪声的原因 相位噪声的表示方法及影响2024-01-31 5407

-

人工智能从何而来2024-09-06 2099

全部0条评论

快来发表一下你的评论吧 !