SiC – 速度挑战

电子说

描述

本文转载自: UnitedSiC微信公众号

功率转换器可以使用不同技术的宽带隙半导体,人们常常会比较这些半导体的开关速度和边缘速率。速度越快,支持的运行频率就越高、损耗就越低,功率转换器磁性元件就越小,听上去很美好。而在真实世界中,更快的dV/dt和di/dt也会成为一个问题,使您难以满足EMI规格要求——极小的轨道值或寄生电感以及电路电容会产生振铃,而且如果必须添加多个昂贵的大滤波器来突破发射限制,宽带隙技术就变得没那么有吸引力了。振铃还会导致电压过冲,从而可能造成损坏,至少会降低电压安全裕度,因而必须使用额定电压更高或更昂贵的器件,而这通常伴随更高的导电损耗。

边缘放缓会增加耗散

在实践中,必须控制边缘速率以避免过冲应力,一个常见解决办法是添加栅极电阻,而且通常会使用二极管栅极控制方法让电阻在打开瞬态和关闭瞬态具有不同的电阻值。当然,这会降低电压和电流边缘速率以及内部电压过冲,但是会增加关闭时的电压/电流重叠,从而提高耗散的功率,而且毫不影响振铃持续时间,该时间发生在关闭瞬态和栅极驱动稳定后。尝试降低电感以尽量减小振铃的努力也会因实际布局而失败,因为实际布局需要实现安全分离并符合所选器件封装类型。

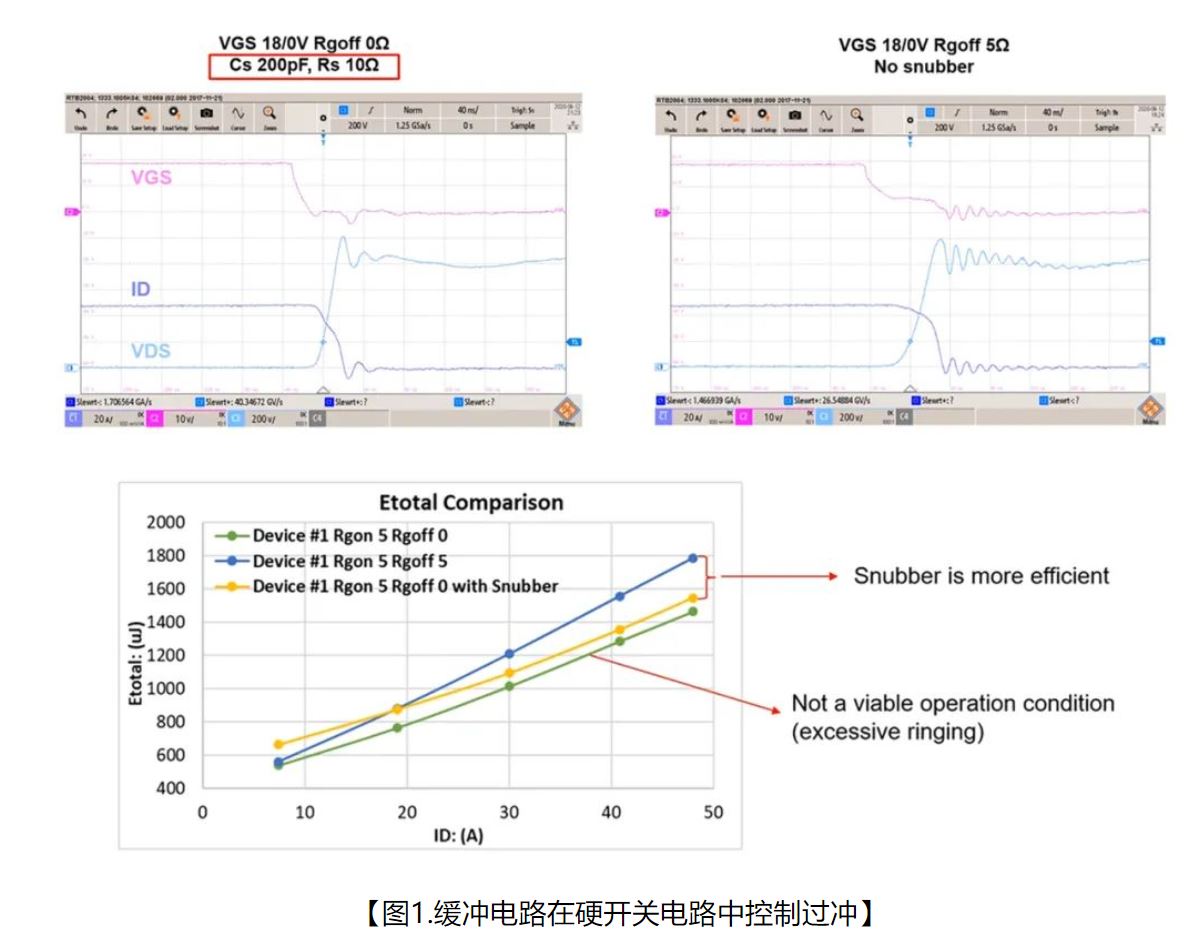

缓冲电路是领跑技术

使用SiC FET时有更好的解决办法,对于硬开关应用,这个办法是跨器件使用小RC缓冲电路,而对于软开关,则是在开关处使用电容器,并跨直流链路轨使用RC缓冲电路。即使缓冲电路RC值小,也可以有效抑制振铃,同时限制过冲并保持低损耗。图1显示的是在硬开关电路中缓冲电路将过冲值控制到与使用5欧姆栅极电阻时相同,但是却阻尼却好得多。与仅使用栅极电阻相比,关闭能量Eoff会减半,但是打开能量Eon会增加10%,因此,为了进行公平比较,我们比较Etotal,结果表明整个缓冲电路方法更高效,同时能提高我们需要的阻尼。在真实电路中,如果ID是40A,开关频率为100kHz,则使用缓冲电路并且没有Rgoff的40毫欧SiC FET会耗散10.9W功率,低于仅使用5欧姆Rgoff时。在这两种情况下,Rgon都设为5欧姆。对于软开关应用,采用简单电容器缓冲电路时损耗甚至会更低。

从波形中可以看出,栅极电阻解决办法还会增加从栅极驱动到漏极电压上升之间的延迟,大约会从33ns延迟到104ns,而这会限制可以达到的最小占空比和高频转换器电路的运行范围。

SiC FET用户指南可加快缓冲电路值选择

通过观察振铃波形可以轻松计算缓冲电路值,只需添加一个小的已知缓冲电路电容器C1,它的电容大约是SiC FET数据表输出电容Coss的3倍,然后观察频率变化,再推断出寄生电容C0,其中包含Coss、杂散电容和所有散热贡献。寄生电感L现在可以通过L-C谐振方程计算得出。可能的缓冲电路起始值为C1= 2 x C0,R=√(L/(C0+C1))。还可以在UnitedSiC网站上找到推荐值,请参见:《SiC FET用户指南》。这里提供了各种产品在硬开关和软开关的LLC和PSFB应用以及一系列频率下的值,可以调节这些值,以实现可接受的效率、电压应力和EMI的组合。

因此,您可以做好准备,让您的功率转换器电路加速至高频,并获得较小的滤波和功率级磁性元件带来的体积、重量和成本优势。所有这些都需要使用最佳SIC FET额定电压来完成任务,并让所含EMI达到可控级别。

审核编辑 黄宇

-

使用SiC技术应对能源基础设施的挑战2024-07-25 1726

-

14.1 SiC基本性质(下)jf_75936199 2023-06-24

-

SiC MOSFET的设计挑战——如何平衡性能与可靠性2023-05-04 1218

-

SiC器件的核心挑战#硬声创作季电子学习 2022-11-20

-

SiC功率器件的新发展和挑战!2022-11-04 1271

-

GaN和SiC区别2022-08-12 10150

-

安森美丰富的SiC方案解决新一代UPS的设计挑战2022-06-24 2097

-

深爱代理SIC953XD..SIC9531D.SIC9532D.SIC9533D.SIC9534D.SIC9535D2021-09-07 1084

-

SiC技术怎么应对汽车电子的挑战2019-07-30 3232

-

车用SiC元件讨论2019-06-27 2518

-

SiC功率器件SiC-MOSFET的特点2019-05-07 5715

-

SiC功率模块的栅极驱动其12018-11-30 3277

-

使用SiC-SBD的优势2018-11-29 4590

-

为何使用 SiC MOSFET2017-12-18 6056

全部0条评论

快来发表一下你的评论吧 !