理解FPGA中的单粒子翻转

描述

1. 介绍

现场可编程门阵列(FPGA,Field-Programmable Gate Array)是当今电子领域不可或缺的一部分,具有出色的灵活性和可配置性。不过,FPGA依赖SRAM单元进行配置,因此容易受到单粒子翻转(Single-Event Upsets,SEU)的影响。本文探讨了FPGA中的SEU,强调了必须防范SEU的原因,以及快速错误纠正的重要性。

2. 理解单粒子翻转

SRAM单元FPGA的核心

SRAM单元是FPGA的控制中心,存储着控制其运行的比特流。SRAM单元状态发生任何变化都可能导致灾难性的功能故障,因此,SEU是一个十分严重的问题。

晶体管缩小和SEU

虽然SRAM单元通常采用较老的技术,但随着为节省芯片面积而缩小晶体管尺寸,SRAM单元对SEU的敏感性也会增加。晶体管尺寸缩小降低了SRAM保存数据的能力,使其对各种外部因素更加敏感,特别是在航空航天应用中。

宇宙射线和地球表面

通常,宇宙射线会在地球大气层中消散,对地表居民几乎不构成威胁。然而,由于SRAM单元的晶体管尺寸不断缩小,人们担心即使宇宙射线减弱也会造成SEU,从而可能导致FPGA故障。

相关粒子

造成SEU的两种粒子主要是中子(模拟宇宙射线)和α粒子,这两种粒子通常由封装中的焊球发射。虽然可以更换材料,但通常更经济的做法是有效处理SEU。

3. 高云FPGA解决方案优势

增强SRAM单元

要防止SEU,首先要增强SRAM单元。高云的创新之举有:设计定制的SRAM单元;增强SRAM单元抗干扰性。这一举措显著提高了抗SEU能力,甚至在较小的芯片尺寸,如22nm的Arora V器件中也是如此。

22nm的BSRAM仍使用TSMC的晶圆厂技术,软错误率(Soft Error Rate,SER)报告中存在显著的差异。高云为用户提供了硬件校验和纠错(Error Checking and Correction,ECC)电路,用于在读取BSRAM内容时纠正BSRAM的SEU错误。

性能比较

高云的抗SEU能力更强,全面的测试数据彰显了这一性能优势。

受控测试

为了量化抗SEU能力,进行中子和α粒子轰击的受控测试至关重要。高云的故障率数据显示,高云FPGA的抗SEU能力非常强,超过了竞争产品和先前几代的FPGA。以下是与高云GW2A 55nm配置SRAM单元的比较,该单元来自TSMC 55nm GP工艺。

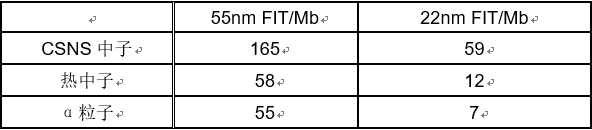

表 1 55nm TSMC 配置SRAM单元 VS 22nm高云配置SRAM单元

4. 快速错误纠正

错误纠正的重要性

对于关键任务的应用,错误纠正至关重要。高云采用基于汉明码的错误纠正系统,能够检测和纠正数据错误。

比较错误纠正

与X公司相比,X公司只能纠正一位错误,而高云的GW5A器件可以纠正两位错误并报告三位错误,提高了系统的可靠性。(138K器件是GW5A器件中唯一纠正一位错误的器件)X公司只能每个frame中纠正一位错误或者相邻两位错误(高级模式下),而高云的GW5A器件可以每个frame中纠正更多类型的两位错误或者分布在frame中不同位置的更多位的错误,并报告不可修复的多位错误,提高了系统的可靠性。

高效的帧大小

高云FPGA的帧设计注重效率,与X公司的帧相比,每帧的位数要少得多。帧大小较小可降低出现多位错误的风险。

关于帧大小的更多信息:

138K: 帧长1513比特

25k: 帧长469比特

60k: 帧长918比特

作为对比,X公司7系列器件的帧长为3232比特。

专用Parabit

高云在SRAM帧内集成了专用Parabit,简化了错误纠正过程,无需使用fabric功能来进行检测和纠正操作。高云提供了一个简单的封装IP——“SEU Handler”,使用户能轻松访问SEU报告和纠正功能。这样既提高了效率,也提高了可靠性。

可定制的扫描频率

高云的FPGA解决方案提供了可定制的扫描频率,能实现更快的错误检测和纠正,这对于在关键的服务器环境中保持不间断运行至关重要。在高级模式下,扫描频率可高达200MHz。

5. 效率与整合

高云的FPGA解决方案将缓解SEU功能集成到硬件中,简化了客户的部署过程。这确保了运行的高效可靠。

6. 高云22nm FPGA软错误率测试报告

测试背景

高云的FPGA设备是基于SRAM的,这意味着用户逻辑是通过内部的配置SRAM单元进行编程和控制的。

业界对由α粒子或中子粒子引起的SRAM单元的SEU有充分的了解,并且在对于在计算关键任务、功能安全和高可靠性应用的系统故障率时需要考虑到这一点。

已测试的SRAM

SRAM单元的数量可从比特流文件中得出。

比特流文件包含需要编程到FPGA SRAM单元阵列的所有数据。

因此,根据阵列大小,可以得到SRAM单元的数量。

这种阵列包括两类SRAM单元:一类是配置SRAM;另一类是块SRAM,用户在设计中将其用于存储器存储,不涉及逻辑控制。

表1和表2显示了SEU所导致的软错误率,该SEU会影响用作配置SRAM和块SRAM的存储单元。

测试方法

中子截面根据JESD89/6加速高能中子测试程序的CSNS射束测试确定,热中子截面根据JESD89/7加速热中子测试程序确定。

纽约市的中子软错误率以FIT/Mb为单位进行了校正。

α粒子截面是根据JESD89/5加速α粒子测试程序,以镅-241源作为α辐射源测定的,α SER(FIT/MB)是根据α发射率每小时每平方厘米0.001计数校正的。

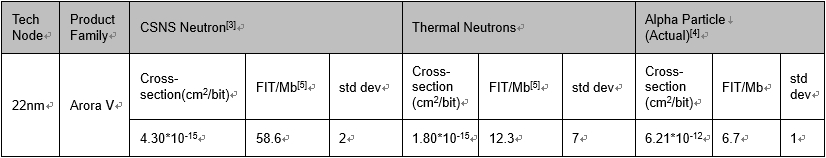

配置SRAM的SER

表2显示了SEU所导致的SER,该SEU会影响用作配置SRAM的存储单元。

表2配置SRAM的SER

Note! [1]实验在带有650Kbytes SRAM的GW5A-25产片上进行。 [2]实验在常温下进行,使用典型的电源电压。 [3]数据来源于中国散裂中子源。 [4]典型的阿尔法数据基于0.001个每平方厘米每小时的阿尔法发射率 [5]中子软错误率(以FIT/Mb为单位)根据JESD89A在纽约市进行了修正。.

[6]在启用ECC功能的测试中,所有在测试期间检测到的SEU都进行了纠正,SER为0。

块SRAM的SER

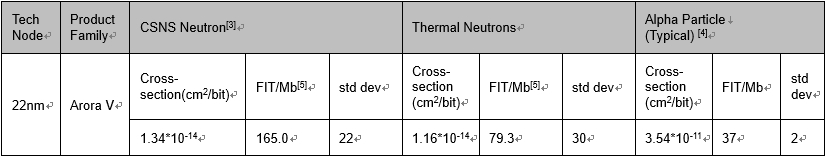

表3显示了SEU所导致的SER,该SEU会影响用作块SRAM的存储单元。

表3块SRAM的SER

Note! [1]实验在带有126Kbytes SRAM的GW5A-25产片上进行。 [2]实验在常温下进行,使用典型的电源电压。 [3]数据来源于中国散裂中子源。 [4]典型的阿尔法数据基于0.001个每平方厘米每小时的阿尔法发射率

[5]中子软错误率(以FIT/Mb为单位)根据JESD89A在纽约市进行了修正。

配置SRAM的ECC

为验证高云22nm FPGA的ECC功能,高云成立了一个实验小组。

在相同的FLUX实验条件下,SRAM的回读频率为15MHz,回读和比较周期为 44610us,在回读过程中可以观察SEU,其中观察到了SBU,但没有观察到MBU。所有观察到的SBU都被ECC电路纠正,整个比特流保持完好,从而器件可以正常工作。

7. 结论

高云的GW5A和GW5AT系列FPGA在防止和纠正SEU方面表现出色凭借增强SRAM单元、高效纠错和专用Parabits,高云为关键任务应用提供了更可靠、更高效的解决方案。

高云的FPGA解决方案使客户即使在最具挑战的环境中,也能满怀信心地部署稳健的系统。

-

一文详解单粒子效应的电荷收集2025-09-08 1511

-

单粒子翻转效应的FPGA模拟技术 (上)2023-02-09 3048

-

航空电子设计之“单粒子翻转”问题2022-07-13 5601

-

有效容忍单粒子多点翻转的加固锁存器2021-06-03 998

-

在芯片设计阶段如何防护“单粒子翻转”2020-11-29 8812

-

单粒子翻转引起SRAM型FPGA的故障机理阐述2020-01-26 8260

-

如何对ADC、DAC、PLL进行单粒子翻转容错设计2019-12-17 2402

-

高速ADC的单粒子闩锁和瞬态2018-10-31 4263

-

ARINC659总线的单粒子翻转识别2018-01-29 1233

-

单粒子翻转加固锁存器分析与辐照试验验证2017-01-07 747

-

一种FPGA单粒子软错误检测电路设计2015-12-31 578

-

用SOI技术提高CMOSSRAM的抗单粒子翻转能力2010-04-22 2137

-

随机静态存储器低能中子单粒子翻转效应2009-10-31 881

全部0条评论

快来发表一下你的评论吧 !