异质集成时代半导体封装技术的价值

描述

随着对高性能半导体需求的增加,半导体市场越来越重视“封装工艺”的重要性。根据这一趋势,SK海力士正在大规模生产基于HBM3(高带宽存储器3)的高级封装产品,同时专注于投资生产线并为未来封装技术的发展获取资源。一些以前专注于半导体存储器制造技术的企业,现在对封装技术的投资超过了OSAT1专门研究这种技术的公司。这种趋势是由这样一种信念推动的,即封装技术将增强半导体行业及其公司的竞争力。

1OSAT(外包半导体组装和测试):专门从事半导体封装测试的公司。

他的文章将 提供对…的简单概述包装技术已经经过深思熟虑的a 困难的主题为这一般 公众的接近 由于其复杂性。 T包装的含义、作用和演变技术将接受检查, 然后 a调查 这 发展萨斯喀彻温海力士的封装工艺这导致了到目前对异构集成的关注。最后,的方向公司的未来技术发展s 将被介绍。

这M含义和R的oleP确认字符(acknowledgementcharacter)(对他人的话作出反应或表示生气、恼怒)唔,啊,哎呀强中子发生器(Intense Neutron Generator的缩写)T技术

首先,让我们看看包装过程的四个主要功能。第一个也是最基本的目的是保护半导体芯片免受外部冲击或da魔术师。第二种是将外部电源传输到芯片用于其操作,和第三是为芯片提供布线,以在操作期间执行电信号的输入和输出。 T他最后作用是为了适当地散发产生的热量经过保证芯片稳定运行。最近,散热或热分布的功能变得越来越重要。

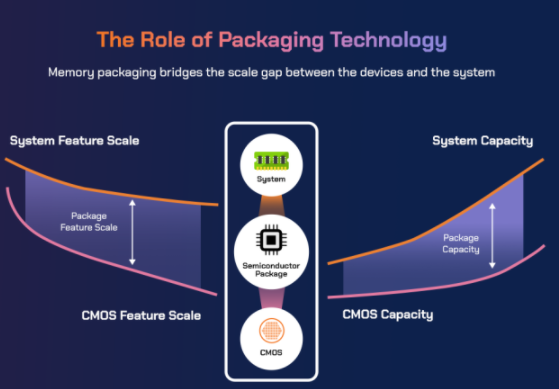

包装的作用可以是看见在图1。例如,两者之间有很大的差距规模系统要求和CMOS提供的比例2,但是他们可以通过封装技术连接。同样,还有一个系统要求的密度与密度CMOS可以提供的。这个问题 可以通过包装过程解决因为它有帮助s增加密度CMOS的。 在其他方面换句话说,封装技术是半导体器件和系统之间的桥梁。 T这个的重要性是连接方法,因此,增加渐渐地。

2CMOS(互补金属氧化物半导体):使用半导体技术的印刷电路板(PCB)上的集成电路设计。

图一。内存封装弥合了设备和系统之间的规模差距

包装发展的三个阶段:堆栈竞争、性能竞争和融合

当考察包装技术的历史时,它可以分为三大部分年代。在过去,a 单一的包裹将仅实现一个芯片。因此,包装很简单,没有区别因素包装技术的附加值低。然而,在21世纪初,随着转换 去FBGA3封装,开始在一个封装上堆叠多个芯片。这能够被称为“堆叠竞争力的时代。”当芯片开始堆叠时,封装的形式多样化的各种衍生产品的产生取决于这内存芯片。主控制程序4, 哪个实现DRAM而同一封装中的NAND,也在此时出现。

3FBGA(细间距球栅阵列):一种表面贴装封装(芯片载体),用于基于球栅阵列技术的集成电路。它的触点更薄,主要用于片上系统设计。

4MCP(多芯片封装):通过垂直堆叠两种或多种不同类型的存储半导体而制成单个封装的产品。

第二时代开始了2010年后,使用芯片上的凸点进行互连的方法出现了。因此,的变化运行速度和设备财产利润发生了。这时期能够呼叫这“性能竞争力时代”如同2010年之前的封装技术通常复杂的连接强中子发生器(Intense Neutron Generator的缩写)金属线,但是介绍突起缩短艾德(男子名)实现更快速度的信号路径s。同时,堆叠方法使用 TSV5大大增加了I/的数量Os(输入/输出),which导联到连接强中子发生器(Intense Neutron Generator的缩写) 1,0246宽I/操作系统(Operating System) 实现高运行速度即使在低电压下。 在这性能竞争时代性能筹码的变化根据包装技术,以及这成为一个重要的因素 在满足的要求顾客s. 如同企业的成败能取决于包装技术的存在与否,包装技术具有的价值继续生长。

第三个也是最后一个纪元开始于 2020 和是 b基于之前所有的 包装技术。 它能够经过深思熟虑的 这“融合时代“因为它需要能够连接v各种类型的筹码到一个包裹和,同样,连接许多零件 在到一个模块当。。.的时候 法人团体强中子发生器(Intense Neutron Generator的缩写)一个系统。在th是纪元,包装技术本身可以成为系统解决方案,可以为客户提供定制的包装解决方案到制造小批量生产成为可能。此时此刻,仅仅拥有包装技术将决定一个企业的成功。

5TSV (Through-Silicon Via):一种互连技术,在DRAM芯片上钻成千上万个细孔,并用垂直穿透的电极连接上下两层的孔。

61,024:标准DRAM高达64 I/操作系统(Operating System),而HBM3的最大宽度I/为1,024操作系统(Operating System)。

图二。包装技术发展带来的变化

SK的历史海力士的 P包装T技术

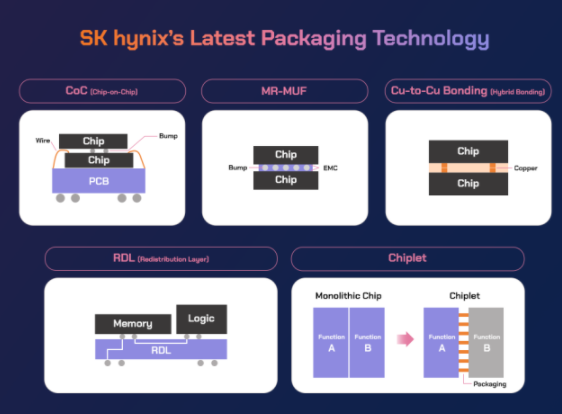

海力士的封装工艺 经历了重大的发展 在整个上述的 年代。 虽然公司美国的封装技术没有明显的差异直到堆叠竞争力era,随着性能竞争力时代的开始,萨斯喀彻温海力士 成为 因其封装工艺。 特别是, 完工证明书7 技术,它结合了b裁判员i互连和w愤怒b翁丁,当引座员在 创新这包括 f全速前进和reduc艾德(男子名)费用。它 is目前一项专门技术应用于SK的生产和制造海力士的 h室内运动场densitym奥德莱斯。此外,SK海力士已经发展了MUF先生8技术并且一直在申请它到HBM产品。这项技术改进了HBM超过100,000个微凸块互连的质量。 另外,这种包装技术充分增加了热虚设凸块的数量虽然散热性能优于其竞争对手,如It应用美国照明工程学会 a m旧的u底部填充(MUF)材料w有吗高导热率。 T他的进步帮助了SK海力士增加其在HBM市场的份额,并最终取得领先地位HBM3扇区中的位置。

7CoC (Chip-on-Chip):一种封装技术,旨在将两个(或多个)芯片电连接在一起,无需TSV(硅通孔)。

MUF先生(大规模回流模制底部填充):MUF先生指的是将半导体芯片附着到电路上,并在堆叠芯片时用一种叫做“液态EMC”(环氧模塑料)的材料填充芯片之间的空间和凸起间隙的过程。迄今为止,NCF技术已被用于这一进程。NCF是一种通过在芯片之间使用一种薄膜来堆叠芯片的方法。与NCF相比,MR-MUF方法具有大约两倍的热导率,并且影响工艺速度以及产量。

海力士正在促进发展使用铜的混合焊接技术–到–铜键合9代替焊接。 此外, 公司I正在复习多种应用各种包装技术的选择,包括移植法这扇出RDL10 技术。混合粘接技术 考虑到更精细的间距11 并且因此在封装高度方面具有优势,因为这是一种无间隙接合技术,不使用s年长的b堆叠芯片时发出的声音。此外,扇出RDL技术适用于各种平台,因此萨斯喀彻温海力士计划使用它当。。.的时候把…合并包装随着小芯片12。线条p瘙痒和m多-layer是关键的组件F安全技术、和SK海力士旨在保护1微米以下的RDL技术,或者在亚微米级别,到2025年。

Cu-to-Cu(铜-铜)键合:封装工艺的混合键合方法之一,通过完全避免使用凸点,为10 m及以下的间距提供解决方案。当封装中的管芯需要彼此连接时,在该工艺中应用直接铜-铜连接。

10RDL(再分布层):集成电路上的一层额外的金属层,它将芯片上其它需要的输入输出焊盘重新布线,以便更好地访问需要的焊盘。例如,位于芯片中心的凸块阵列可以重新分布到芯片边缘附近的位置。重新分布点的能力可以实现更高的接触密度,并实现后续的封装步骤。

11间距:互连线之间的最小中心到中心距离

12小芯片:按用途(如控制器或高速存储器)划分芯片的技术,在封装过程中重新连接芯片之前,将它们制造为单独的晶片

图3。SK海力士的最新包装技术

P包装技术将成为提供 整体的系统解决方案那去 超越一维函数诸如芯片保护离子和 供应电力。用不了多久c公司需要可能的字母s封装工艺成为一名领导者在半导体工业。 几年前,一个主要的年的铸造公司东亚不仅创建了新的系统级封装(啜饮)通过一种叫做 i集成的f出去吧 (信息)包装,但是它是 也能提高的现有业务领域 foundry销售—这意味着萨斯喀彻温海力士。 就像这样 公司 因其生产的作用控制器,萨斯喀彻温海力士 是 有名的 为 生产强中子发生器(Intense Neutron Generator的缩写) 高的表演 半导体记忆诸如它的HBM。萨斯喀彻温海力士还开发了先进的包装技术,如异质整合和扇出RDL技术—即将到来的融合时代的关键封装技术。 因此,公司是不仅玩强中子发生器(Intense Neutron Generator的缩写)一个记忆整合的角色 d埃维切m制造商(IDM)但是也正在成为 a 总数 “s解决方案provider “那能引领未来半导体记忆行业。

审核编辑:黄飞

-

芯粒设计与异质集成封装方法介绍2026-03-09 892

-

喜讯 | MDD辰达半导体荣获蓝点奖“最具投资价值奖”2024-05-30 1283

-

半导体发展的四个时代2024-03-13 4646

-

异构集成时代半导体封装技术的价值2023-11-28 1226

-

华林科纳的化合物半导体异质集成2023-08-14 1511

-

半导体集成电路封装技术及芯片封装意义、技术领域分享!2022-12-13 6448

-

二维半导体薄膜在任意表面的异质外延技术2022-10-19 2739

-

集成电路与半导体2021-09-15 3014

-

芯片,集成电路,半导体含义2020-02-18 6488

-

射频集成电路半导体和CAD技术讨论2019-07-05 2570

-

我国半导体封装业发展状态和方略2018-08-29 4439

-

集成电路封装技术专题 通知2016-03-21 3969

-

国防威胁减除局寻求抗辐射高频模拟和射频半导体2012-12-04 3017

-

半导体异质结构的应用知识2010-03-06 2308

全部0条评论

快来发表一下你的评论吧 !