开关电源芯片输出电压调整率技术指南

电子说

描述

01如何改善高压非隔离架构的输出电压调整率?

大家首先要了解在DCM工作模式下,高压浮地Buck工作模态包括:励磁模态、消磁模态和振荡模态。

励磁模态[t0,t1]

消磁模态[t1,t2]

振荡模态[t2,t3]

关键点工作波形

在消磁期间[t1,t2],由于D1导通,VDD和Vo共地,Vo可以通过VDD真实反馈:

备注:VF1和VF2分别为D1和D2的正向压降

在振荡期间[t2,t3],由于D1截止,Vo不能通过VDD直接反馈,Vo向负载供电,VDD向控制芯片供电,如果Cvdd和Co的放电速率相等则VDD可以间接反馈Vo。

此类浮地Buck架构,控制芯片通过VDD电压间接采样输出电压,闭环调节Buck变换器能量使得输出电压稳定在设定值。而浮地Buck-boost架构,输出电压间接采样及稳压原理相同,不再赘述。

实战技巧

对于芯朋微PN8034、PN8016、AP8506等非隔离高压芯片,为提高输出电压调整率,建议如下:

1.由公式(1)式可知,可通过调整D1和D2正向压降来微调输出电压稳态值;

2.不同负载下,输出电容的放电速率变化较大,为改善输出电压负载调整率,供电电容放电速率建议为0.5~2倍的输出电容满载放电速率。

02、如何改善原边反馈反激架构的输出电压调整率?

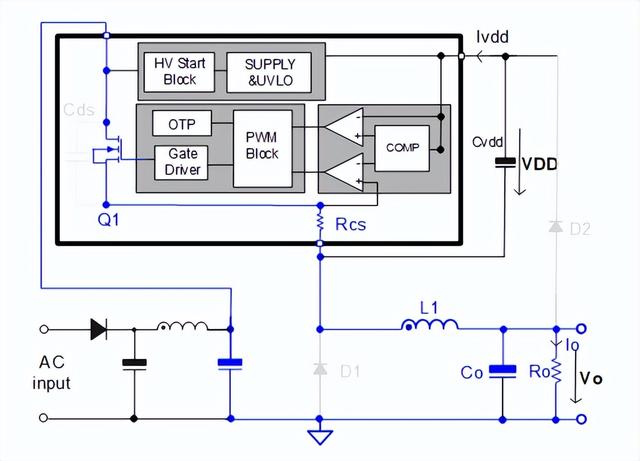

在DCM工作模式下,原边反馈反激电源的典型电路及工作波形如下:

典型电路图

关键点工作波形

在消磁期间[t1,t3],D1导通后变压器被输出电压Vo钳位,折射到VFB的电压为:

备注:VF1为D1的正向压降

控制芯片在消磁期间对VFB电压进行脉冲采样及保持,则可以获取到输出电压信息,为了避免变压器漏感振荡对输出电压采样的影响,芯片的采样保持点需避开[t1,t2]区间。

实战技巧

对于芯朋微PN8370、PN8680、PN8390、PN8575等PSR芯片,为提高输出电压调整率,建议如下:

1.为了避免漏感振荡对输出电压间接采样的影响,RCD吸收电路的串联电阻Rrcd建议大于100Ω,FB脚并联电容CFB建议大于33pF;

2.为了减小VDD回路对输出电压间接采样的影响,D2建议用快管,Rvdd建议大于4.7Ω;

3.变压器设计合理,最小消磁时间Tdmg_min务必大于2us(推荐大于2.5us),利于芯片内部的采样和保持(S/H)运算。

备注:其中Vcs_min为芯片CS脚的最小基准电压

03、典型应用案例

浮地Buck智能wifi排插应用案例

5V250mA Buck 非隔离方案

浮地Buck-boost智能家电应用案例

12V300mA Buck-Boost 非隔离方案

原边反馈Flyback网通适配器应用案例

12V1.5A 适配器应用方案

-

pwm开关电源输出电压跳动原因分析2024-10-18 7896

-

怎样改变开关电源的输出电压2024-07-08 8030

-

开关电源线性调整率快速测试方法2024-03-14 3104

-

开关电源中什么是负载调整率?如何去测?2024-01-19 5359

-

如何改善原边反馈反激架构的输出电压调整率?2023-11-24 3049

-

电子负载怎么调试开关电源?开关电源负载调整率怎么改善?2023-11-07 5423

-

电源模块测试用例之开关电源电压调整率的测试方法2023-10-17 2545

-

开关电源如何改变输出电压2023-08-17 14220

-

开关电源:TL431与光耦组成的电压反馈电路2022-11-21 17506

-

开关电源芯片提高输出电压调整率实战解析2021-08-03 6225

-

开关电源的技术指标有哪些2020-08-25 3251

-

什么决定了输出电压的电压调整率和负载调整率?2019-07-17 9767

-

开关电源中什么是电压调整率和负载调整率?2019-07-04 53932

-

改善多路输出开关电源交叉调整率的无源设计2011-09-27 1541

全部0条评论

快来发表一下你的评论吧 !