Chiplet技术革新赋能,开阔芯片设计新思维!

描述

在数字化时代,半导体技术的进步是推动产业发展的重要驱动力。

终端用户对芯片的需求越来越多样化,其为满足这些独特的需求,定制芯片逐渐成为趋势。

纵观全局的同时,我们也需“追根究底”,终端用户对芯片需求多样化体现在哪?

应用场景的多样化:以往,芯片主要应用于电脑、手机等消费电子产品,但现在,芯片的应用范围已经扩大到商业显示、工业、汽车、医疗、教育等各个领域;不同的应用领域对芯片有着不同的需求,这就需要芯片具有更高的适应性和灵活性。

性能需求的多样化:消费者对设备性能的要求越来越高,市面上对芯片的性能需求也变得更为多样化;比如,一些用户需要芯片具有强大的计算能力,以支持复杂的数据分析和图像处理,另一些用户则更看重芯片的低功耗设计,以保证设备的续航能力。

安全性的需求:网络安全问题的日益严重,用户对芯片安全性的需求也越来越高;且希望芯片能够具备强大的安全防护能力,保护设备免受黑客攻击和病毒感染。

小型化和集成化的需求:在许多应用中,尤其是可穿戴设备和物联网设备等新兴领域,用户对芯片的小型化和集成化需求强烈;其希望芯片在保持高性能的同时,能够占用更小的空间,消耗更少的能源。

值得注意的是,Chiplet用户应用端则为这一趋势提供了强有力的支持:

同时,终端用户根据需求定制芯片,从而大大提高应用性能,且确保供应链安全与可靠性,推动技术创新,并顺应垂直整合的趋势。

那么,目前传统芯片设计方法往往无法满足终端用户的多样化需求。

在此背景下,Chiplet因需更多异构芯片和各类总线的加入,将会使得整个芯片的设计过程变得更加复杂。

相关半导体行业从业者就指出:在一个封装只有几百个I/O的时代,封装设计者还有可能用试算表(Spreadsheet)来规划I/O,但在动辄数千甚至上万个I/O互连的先进封装设计中,这种方法不仅太耗时,且出错的机率很高。

基于资料库的互连设计,还有设计规则检查(DRC),都将成为先进封装设计的标准工具。

此外,以往封装业界习惯使用的Gerber档格式,在先进封装时代或许将改成GDSII档格式;整体来说,封装业界所使用的工具,都会变得越来越像Fab跟IC设计者所使用的工具。

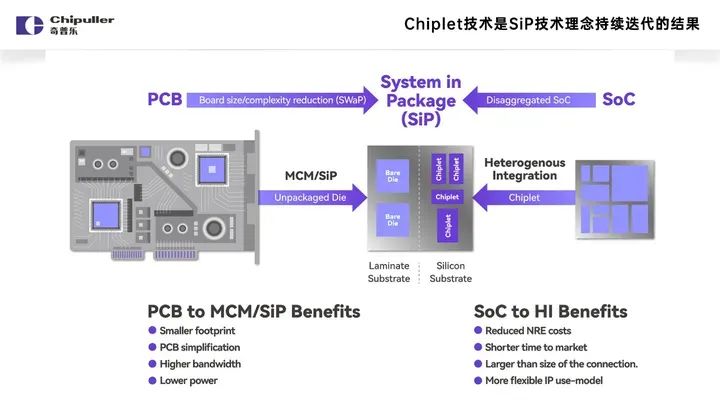

因此,在芯片的设计流程之前,应将SoC分解为Chiplet,设计人员需更密切地协作,并使用相关的EDA工具。

图片来源:奇普乐

首先,需要更新RDL Netlist和线路布局(Place & Route)的工具,为了应对多晶片所带来的挑战,设计人员还需要应用更多的设计模拟工具,以解决电源一致性(PI)、讯号一致性(SI)、电磁相容(EMC)以及散热(Thermal)等问题。

其次,使用EDA工具可以确保Chiplet之间的互连和通信更加准确和高效,这些工具能够对设计进行仿真和验证,确保设计的正确性和性能。

然而,随着芯片集成度的提高,散热成为一个重要问题;EDA工具可以对Chiplet的热性能进行模拟和分析,帮助设计团队优化散热设计,确保芯片在工作中的稳定性。

特别是,由于整个行业都在积极探索Chiplet设计的最佳实践和解决方案,奇普乐以应对这些挑战并推动Chiplet设计的应用。

奇普乐Chiplet技术应运而生,其为终端用户自定义设计芯片开辟了新的道路,同时,也提供了更高的性能和更低的功耗。

目前Chiplet可以并行设计和生产,这使得芯片的开发周期大大缩短,进一步加速了产品的生产时间。

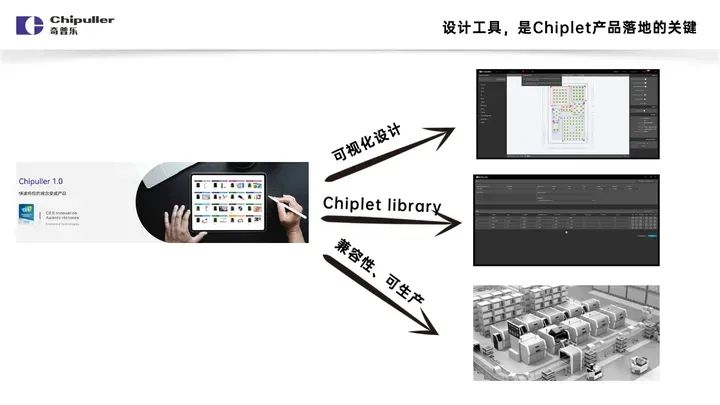

通过奇普乐自研的Chipuller 1.0平台应用端,终端用户可以体验一个简单而高效的定制流程。

图片来源:奇普乐

除此之外,奇普乐所掌握的Chiplet技术结合了芯片堆叠、SASiRogo(硅上互联系统)中电源管理和外设IP的集成,并提供了比传统PCB更小、比ASIC更灵活的单芯片解决方案。

与此同时,奇普乐也看到了Chiplet技术在推动产业协作和创新方面的巨大潜力。

尤其,通过构建开放的Chiplet技术生态,我们期望与众多合作伙伴共同推动这一技术的发展,创造出更多前所未有的应用场景和商业价值。

图片来源:奇普乐

当然,我们深知在迎接这一技术革新的过程中,也会面临诸多挑战;但正如一句古话所说:“风物长宜放眼量”。

-

微电网规划中储能技术革新的方向有哪些?2026-04-09 254

-

耐能KNEO Pi开发板的三大技术革新2025-06-06 1411

-

Arm关键洞察 芯片新思维 奠定人工智能时代新根基2025-03-14 989

-

蓄电池放电技术革新:引领能源存储新时代2025-02-08 6061

-

电池充放电测试仪厂家:技术革新与市场竞争的领航者|鑫达能2025-01-14 1273

-

NVH-FLASH语音芯片支持平台做语音—打造音频IC技术革新2024-10-16 1269

-

技术革新:AI与RFID的融合,亚马逊引领零售行业变革2024-09-09 1141

-

英特尔推出集成光学计算互联OCI Chiplet芯片2024-06-28 4173

-

天马微电子荣获阿尔卑斯阿尔派2023年度“技术革新奖”2024-05-29 1785

-

什么是Chiplet技术?2024-01-25 4540

-

C++设计新思维-泛型编程与设计之应用2022-11-16 653

-

TDK帮助机器人实现技术革新的传感器解决方案2020-07-09 1985

-

探析5G时代的技术革新挑战2018-12-04 5937

-

快速发展的无线标准以及如何应对技术革新者们面临的困境2017-11-17 1333

全部0条评论

快来发表一下你的评论吧 !