FPGA图像处理_ISP算法DPC流程

描述

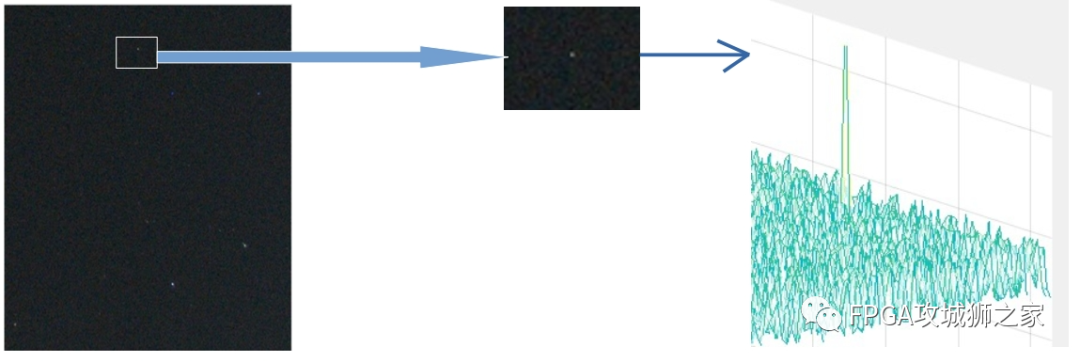

DPC通常作为ISP算法流程里面的第一个模块,原理也很简单。DPC 应对的主要问题是传感器像素的缺陷,这些缺陷可能源于制造缺陷、长期磨损或外部因素如灰尘侵入,这些缺陷像素在成像时无法准确记录光线信息,表现为静态的亮点、暗点或彩点,从而破坏图像的整体质量

坏点校正技术的实施通常涉及两个阶段:检测和校正。在检测阶段,算法分析传感器输出的原始图像数据,识别出异常。

然后,在校正阶段,利用周围正常像素的值采用插值等方法对这些异常像素进行修复。

这一过程的关键在于恰当平衡,以去除缺陷的同时尽可能保留图像的真实细节。

当 DPC 算法得当,其结果是让最终图像在视觉上免受这些缺陷像素的影响,保证了图像质量的准确性和一致性。

运算的一般方法为

1,在邻域的 3*3 区域内,对比中心像素与周围像素之间的差值,如此得到 8 个差值

2,如果第一步中得到的 8 个差值同为正数,或者同为负数,并且所有值的绝对值大于设定的阈值,那么进行第三步。否则直接输出原有的中心像素值。

3,在 3 * 3 的区域内,找到中值。

4,用中值替换掉原来的中心像素值

上述模块的精彩之处在于:

1,LineBuffer 进行了IP 化,可以任意多行并行输出。

2,中值滤波本来可以很简单,但是本文中采用方法独特,时序最优,占用资源最少。

3,代码从400M的主频跑到了600M,优化之后跑到了725M 的主频。

4,讲解如何进行时序优化

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA设计经验之图像处理2024-06-12 3324

-

FPGA图像处理之CLAHE算法2024-01-04 4235

-

相机图像信号处理流程(ISP)介绍2023-12-09 6708

-

FPGA图像处理算法有哪些2023-09-12 2081

-

图像信号处理ISP有哪些产品趋势?2023-09-07 2573

-

CMOS图像传感器的ISP算法2023-05-28 6605

-

FPGA学习-基于FPGA的图像处理2023-02-15 2257

-

如何使用FPGA实现图像的中值滤波算法2021-04-01 1371

-

ISP处理流程及应用场景2018-09-25 5912

-

ISP图像处理芯片2018-01-12 20123

-

基于FPGA的红外图像处理系统及算法设计2016-05-17 878

-

ECT图像重建算法的FPGA实现2015-11-19 924

-

基于DSP和FPGA的通用图像处理平台设计2010-12-25 653

-

FPGA图像与视频处理培训2009-07-16 6002

全部0条评论

快来发表一下你的评论吧 !