硬件电路设计之DDR电路设计(2)

描述

1 简介

本文主要讲述一下DDR从0到1设计的整个设计的全过程,内容涵盖以下部分:

- SDRAM电路设计

- DDR4电路设计

下一篇文章内容:

- DDR4级联

- DDR4 Layout注意事项

2 SDRAM电路设计

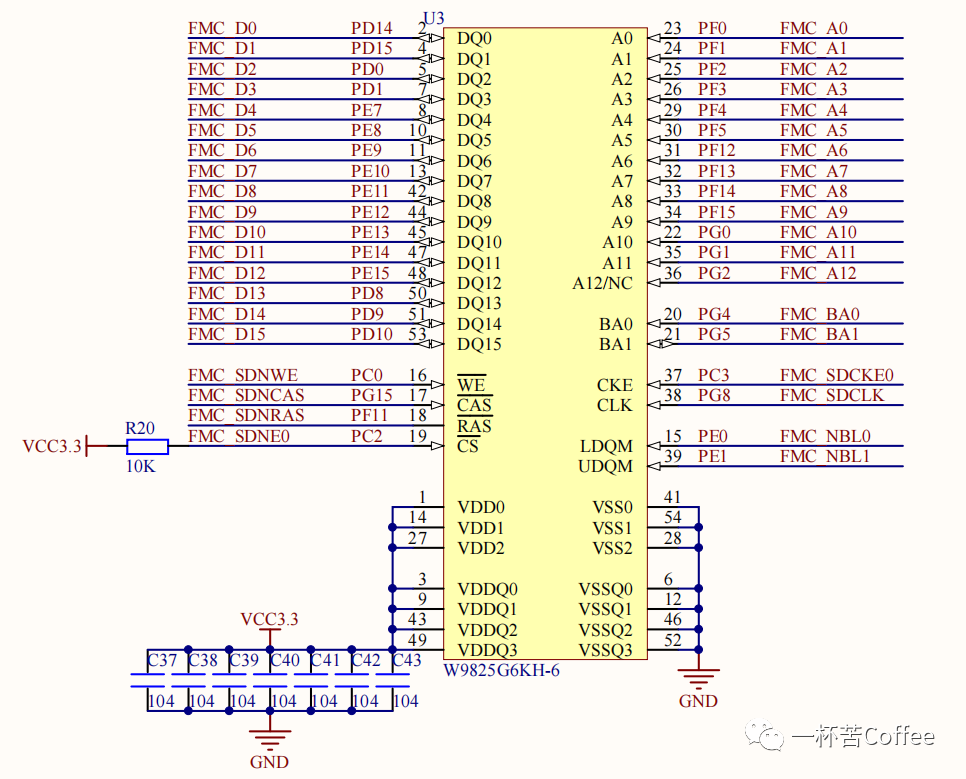

W9825G6KH-6是一种 动态随机存取存储器 ,存储的容量为 256 Mbit ,支持最大时钟频率为 166MHz ,供电范围 3V~3.6V 。

电路分析:

- 地址线A0-A12 :行地址线为A0-A12;列地址线为A0-A8,无需上拉电阻;

- 数据线DQ0-DQ15 :数据的输入输出线为DQ0-DQ15,无需上拉电阻;

- 片选信号CS :当CS为低电平时,表示选中该芯片。多个芯片复用或者与NAND FlashNor Flash复用时,需要注意该信号。

- 行选通信号RAS列选通信号CAS :行选通信号为RAS(Row Addredd Strobe),低电平有效,列选通信号为CAS(Column Addredd Strobe),低电平有效;

- 写使能信号WE :写使能信号为WE(Rrite Enable),低电平有效;

- 数据输入输出屏蔽信号LDQMUDQM :用于在读模式下控制输出缓冲,在写模式下屏蔽输入数据。LDQM,UDQM这些信号线是为了实现字节访问和半字访问,LDQM控制低八位,UDQM控制高八位,这样当要按字节写的时候,就把高八位屏蔽掉。

- 时钟信号CLK :输入时钟信号;

- 时钟使能CKE :输入时钟使能引脚CKE,高电平有效。

- 电源引脚VDD和VDDQ :均采用3.3V供电。

3 DDR4电路设计

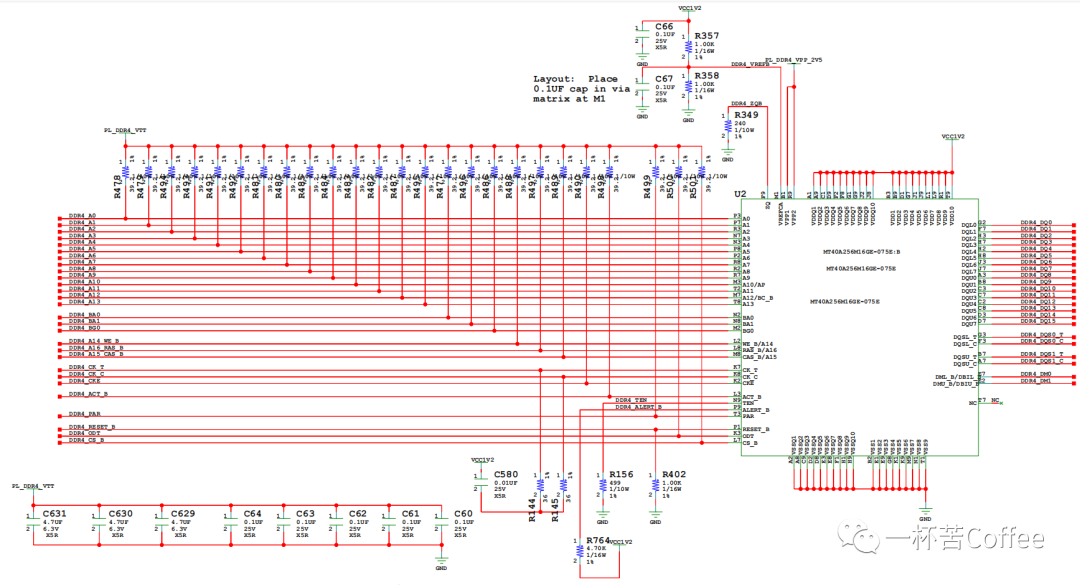

今天使用的DDR颗粒为镁光的MT40A256M16GE-075E(DDR 的厂家有三星、镁光、海力士、东芝,国产厂家有长鑫、紫光),数据位宽为16bit,存储的容量为4Gbit(容量计算请参考:硬件电路设计之DDR电路设计(1)),支持最高的时钟频率为1.333 GHz,供电范围1.14V-1.26V,封装形式为96-Ball FBGA。

电路分析:

- 电源设计

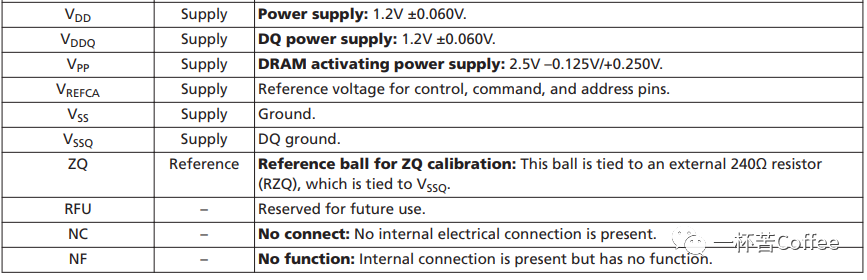

DDR4的电源主要有以下几个部分: VDD(核电压)、VDDQ 、 参考电压VREF、VTT、激活电压VPP 。

1、电源VDD

Power supply通常也会被称为主电源(核电压),其供电范围: 1.2V ±0.060V。随着不断发展,主电源(核电压)的电压在不断降低,具体见下:

| 序号 | 版本 | VDD电压 |

|---|---|---|

| 1 | SDRAM | 2.5V/3.3V |

| 2 | DDR2 | 1.8V |

| 3 | DDR3 | 1.5V |

| 4 | DDR4 | 1.2V |

| 5 | DDR5 | 1.1V |

2、电源VDDQ

DQ power supply是给IO buffer供电的电源,其供电范围:1.2V ±0.060V。一般情况下,VDD和VDDQ合成一个电源使用,即VDDQ=VDD。

3、参考电压VREFCA

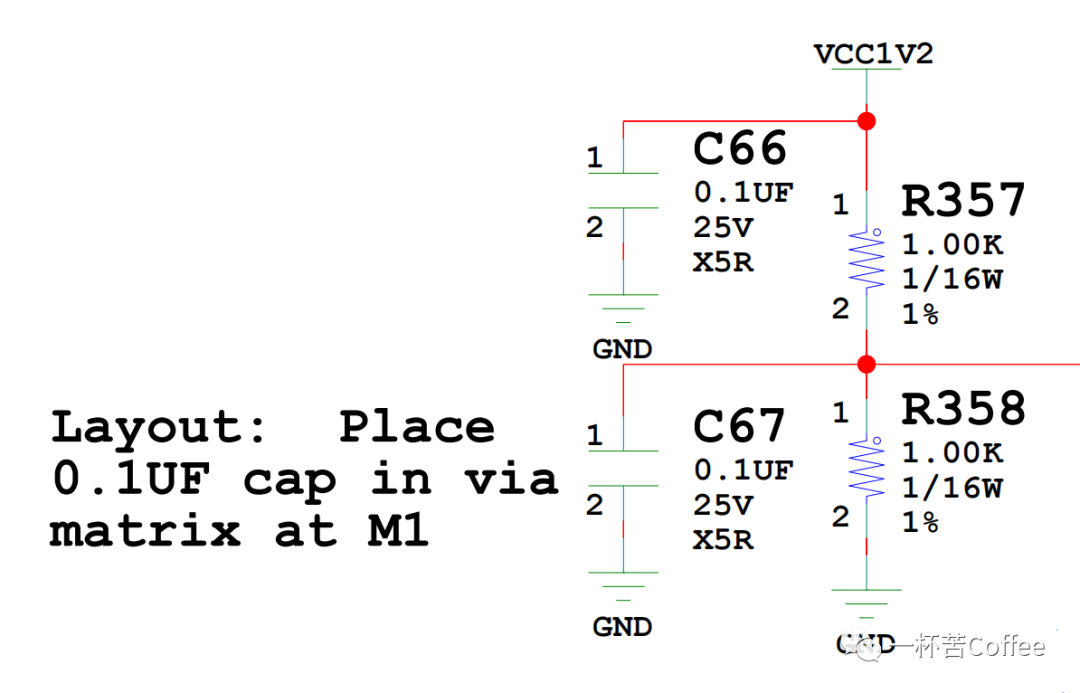

控制、命令和地址的参考电压。该电压要求跟随VDDQ,且VREF=VDDQ/2。参考电压VREF可以通过两种方式获取:

- 电阻分压

VREF需要的电流比较小,一般为mA和几十mA的数量级,这种方式在布局上比较灵活,且成本较低。分压电阻的取值范围:100Ω-10kΩ,电阻精度为1%。参考电压VREF每个分压电阻上需要添加一个0.1uF的滤波电容。

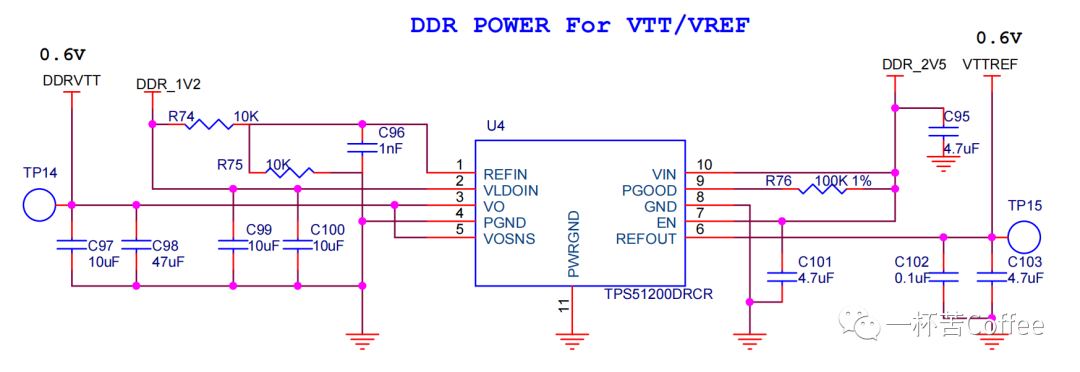

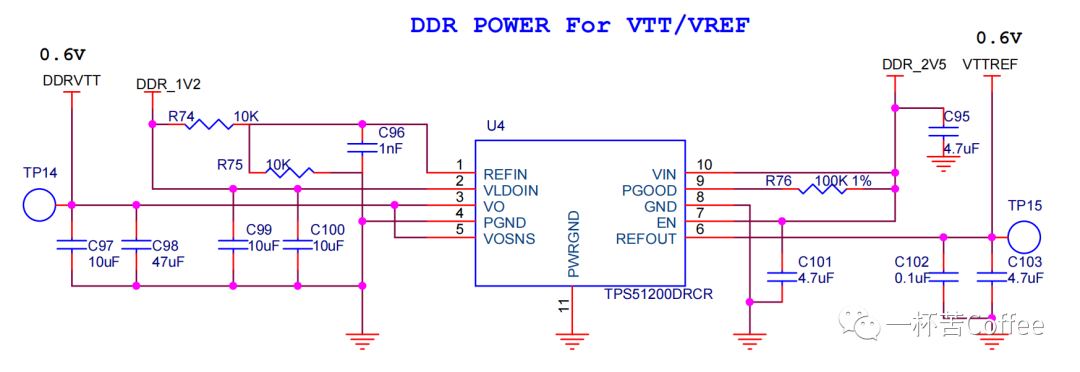

- 电源芯片提供

此处推荐的芯片是TID的电源管理芯片(TPS51200DRCR),TPS51200 器件是一款灌电流和拉电流双倍数据速率 (DDR) 终端稳压器,专门针对低输入电压、低成本、低噪声的空间受限型系统而设计。

TPS51200 可保持快速的瞬态响应,仅需 20µF 超低输出电容。TPS51200 支持遥感功能,并满足 DDR、DDR2、DDR3、DDR3L、低功耗 DDR3 和 DDR4 VTT 总线终端的所有电源要求。

此外,TPS51200 还提供一个开漏 PGOOD信号来监测输出稳压,并提供一个 EN 信号在 S3(挂起至 RAM)期间针对DDR应用对VTT进行放电。

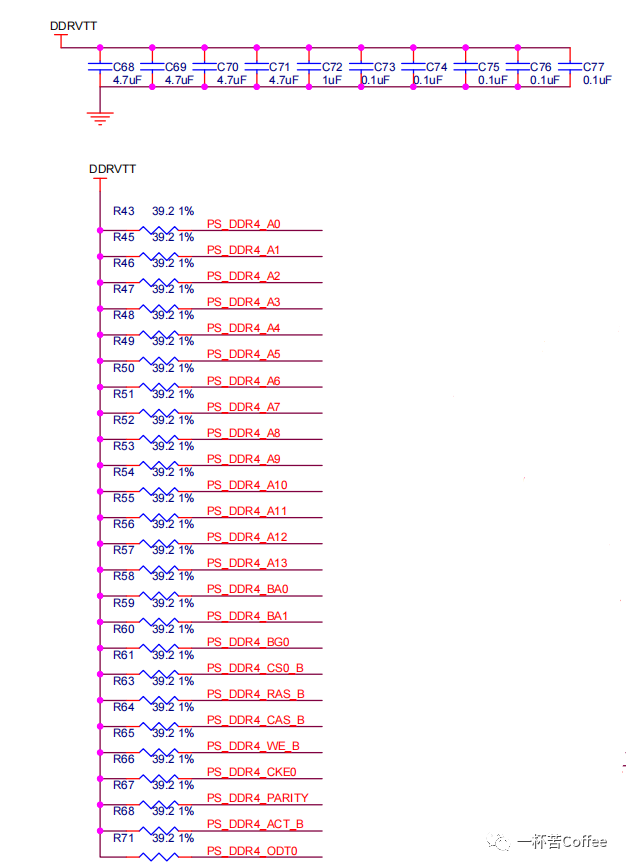

4、用于匹配的电压VTT

VTT为匹配电阻上拉到的电源,VTT=VDDQ/2 。DDR的设计中,根据拓扑结构的不同,有的设计使用不到VTT,如控制器带的DDR器件比较少的情况下。 如果使用VTT,则VTT的电流要求是比较大的,所以需要走线使用铜皮铺过去。 并且VTT要求电源,即可以提供电流,又可以灌电流(吸电流)。

一般情况下可以使用专门为DDR 设计的产生VTT的电源芯片来满足要求(曾经使用过程中用了简单的线性稳压器也没发现出现什么问题,这种方式还是不建议的)。每个拉到VTT的电阻旁一般放一个10nF~100nF的电容,整个VTT电路上需要有uF级大电容进行储能。

一般情况下,DDR的数据线都是一驱一的拓扑结构,且DDR2和DDR3内部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到较好的信号质量。而地址和控制信号线如果是多负载的情况下,会有一驱多,并且内部没有ODT,其拓扑结构为走T点结构或Flayby结构,所以常常需要使用VTT进行信号质量的匹配控制。

5、激活电压VPP

VPP为激活电压,一般为2.5V电压,上电的时间必须早于VDD,且在整个工作期间必须保持高于VDD的电压。

6、ZQ电阻

输出驱动校准的外部参考。这个脚应该连接240ohm 电阻到 VSSQ。

- 时钟设计

1、CK_T、CK_C

**CK_T、CK_C是差分时钟输入 。所有的地址、命令和控制信号都是在CK_T上升沿和CK_C下降沿的 交叉位置采样 。

2、CKE

CKE是时钟使能信号,高电平有效。

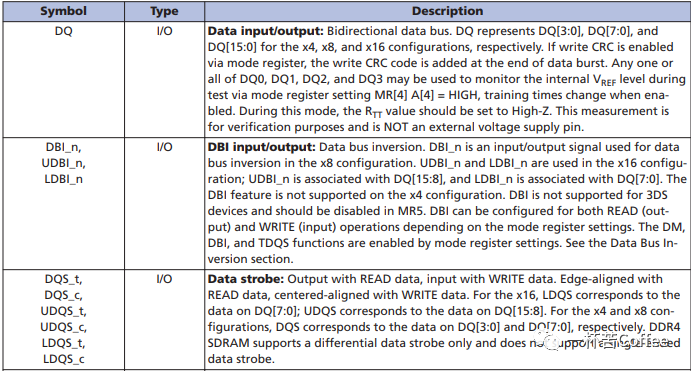

- 数据信号

1、DQ数据线

数据输入/输出,双向数据总线。

2、DBI_n、LDBI_N、UDBI_n

数据掩码以及数据总线倒置:DM 信号是作为写数据的掩码信号,当 DM 信号为低电平时,写命令的输入数据对应的位将被丢弃。DM 在 DQS 的两个条边沿都采样。同时,在 MR5 中的 A10,A11,A12 可选择此信号是 DM 还是 DBl。在 X8 设备中, MR1 的 A11 可控制此信号是 DM 或者 TDQS, DBI 为低电平时,DDR4 SDRAM 会将数据进行翻转存储以及输出,反之,DBI 为高电平时,则不会翻转数据,TDQS 仅支持 X8 设备。

3、LDQS_T、LDQS_C

数据选通信号:输入时与写数据同时有效,输出时与读数据同时有效,与读数据时边沿对齐的,但是跳变沿位于写数据的中心。在 x16 系统中,DQSL 对应到 DQL0_7;DQSU 对应到DQU0_7;DQS_t,DQSL_t 与 DQSU_t 分别与 DQS_c, DQSL_c与 DQSU_c,对应为差分信号对。DDR4 SDRAM 仅支持选通信号为差分信号,不支持单根信号的数据选通信号。

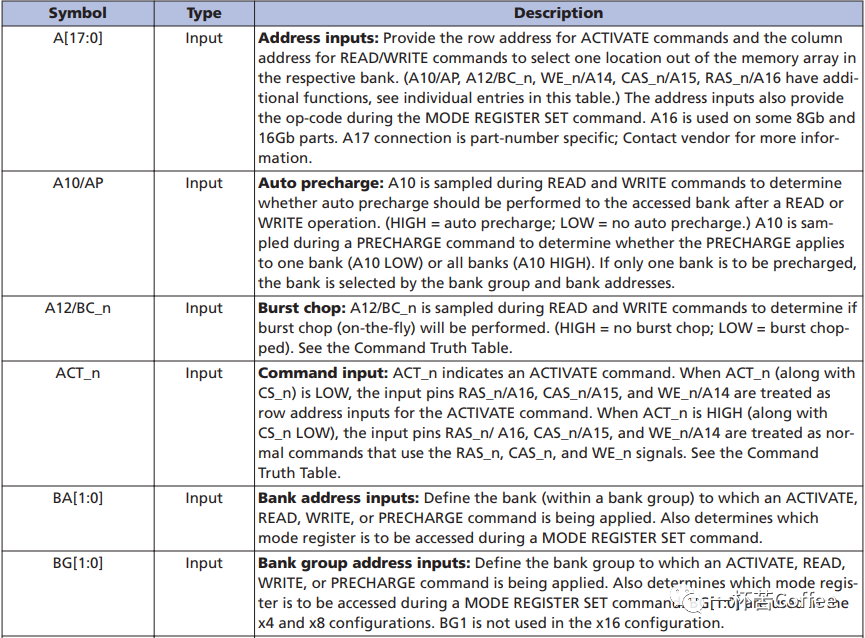

- 地址和控制信号

1、BA[1:0]

BANK地址输入,用于指定当前操作的BANK。

2、BG[1:0]

Bank Group 地址输入;BG0-BG1可以选择当前的 ACT、READ、WRITE或是PRE 命令是对哪一个 BANK 组进行操作。在MODE REGISTER SET 命令中,BG0 也参与模式寄存器的选择。在 X4、X8 系统中,有 BG0和BG1,而 X16 系统中,仅有 BG0。

3、A[17:0]

地址输入引脚,其中有些引脚具有一些其它的复用功能,详见下:

- A10有AP功能(自动预充电)

- A12有BC_N功能(突发中止)

- A14有WE_N功能(写使能)

- A15有CAS_N功能(行地址选通)

- A16有RAS_N功能(列地址选通)

4、ODT

片上终端电阻使能,高电平有效。

5、RESET

复位信号,低电平有效。

6、ALERT_N

警告信号,低电平有效。当出现数据错误(CRC校验错误等)时,该引脚会被拉低。

7、TEN

连接测试信号,高电平有效。正常使用使用过程中,该信号必须为低电平。

8、PAR

奇偶检验使能信号。这个功能必须通过寄存器来使能或失能。

9、ACT_N

激活信号,低电平有效。ACT_N为低电平时,A[16:14]为复用功能,ACT_N为低电平时为高电平时,A[16:14]为地址线。

-

硬件电路设计2013-11-08 34193

-

高速电路设计2015-07-06 3713

-

硬件电路设计流程系列2017-10-17 3771

-

核心板硬件电路设计2021-02-01 3440

-

硬件电路设计的思路分享2021-11-11 2448

-

硬件电路设计与实践2015-12-08 1165

-

硬件电路设计具体详解2016-04-05 940

-

硬件电路设计流程--原理图设计2016-10-10 1697

-

硬件电路设计之“磁珠”的应用资料下载2021-04-15 1253

-

主板电源DC-DC电路设计之电容的选择2021-11-18 1545

-

硬件电路设计的基本流程、作用和注意事项2023-06-30 3411

-

怎么成为硬件电路设计高手?2023-07-28 9720

-

硬件电路设计之晶体与晶振电路设计2023-11-22 4383

-

硬件电路设计之DDR电路设计(1)2023-11-24 9708

-

硬件电路设计之DDR电路设计(4)2023-11-29 19576

全部0条评论

快来发表一下你的评论吧 !