SAR型ADC应用要点

描述

当然,使用ADC前一定要仔细阅读它的datasheet,但如果对于该器件没有任何了解,可能通读完整篇手册也找不到重点,具体应用时还是毫无头绪;我就经常有这样的感觉。就像哲学家黑格尔讲过的:没有相应的概念,经验对象在我们眼中就是“有之非有”,“存在着的无”。

本文就着手整理一下使用ADC时的要点,希望以后再阅读手册就可以更有侧重、更有效率 。肯定会不全面、有错误,但算是一个总结。因为ADC是很复杂的,作为模拟和数字混合器件,参数非常之多!另外,我们其实是假设了,已经根据应用条件已经选好了ADC,选型ADC也是有挑战的。

这里讲的是SAR型ADC,因为这种ADC工作中用到的最多,它具有精度高(如16位)、采样速率快(甚至可以达到80Mhz),功耗低,有些SAR-ADC可以多通道输入等特点。

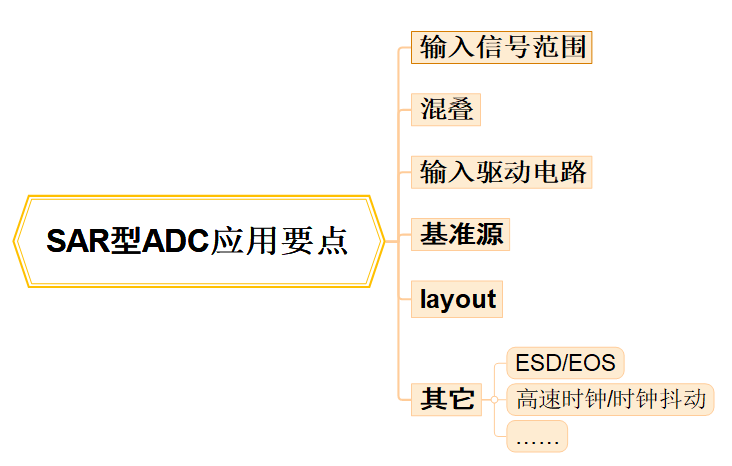

图1 SAR型ADC应用要点

输入信号范围

如果想要充分利用好ADC的话,我们输入给ADC的信号范围,最好是接近它的满量程输入范围。ADC的满量程输入范围跟它的输入类型有关系,单端还是差分(还有伪差分);一般性能好的SAR型ADC,都是差分输入。跟基准源也有关系。

比如基准源1.8V的ADC,如果是单端输入,那么它的满量程输入就是1.8V。如果是差分输入,那么它的满量程输入就是3.6V。一般会留一些裕量,避免输入信号超过满量程输入范围,输入到ADC的信号会稍微小于满量程输入如100mV。担心信号超出ADC满量程范围后,输入极进入饱和区会影响速度等;即ADC的输入信号要在它的“推荐工作条件”内,否则影响性能。

因此,ADC的满量程输入范围,就相当于放大器的输出,输入信号已知,放大器的增益基本就确定了。放大器可能是单端,可能是差分。具体跟ADC输入极有关系。另外,差分输入的ADC,也是可以单端输入的,只不过输入范围只用了一半。

混叠

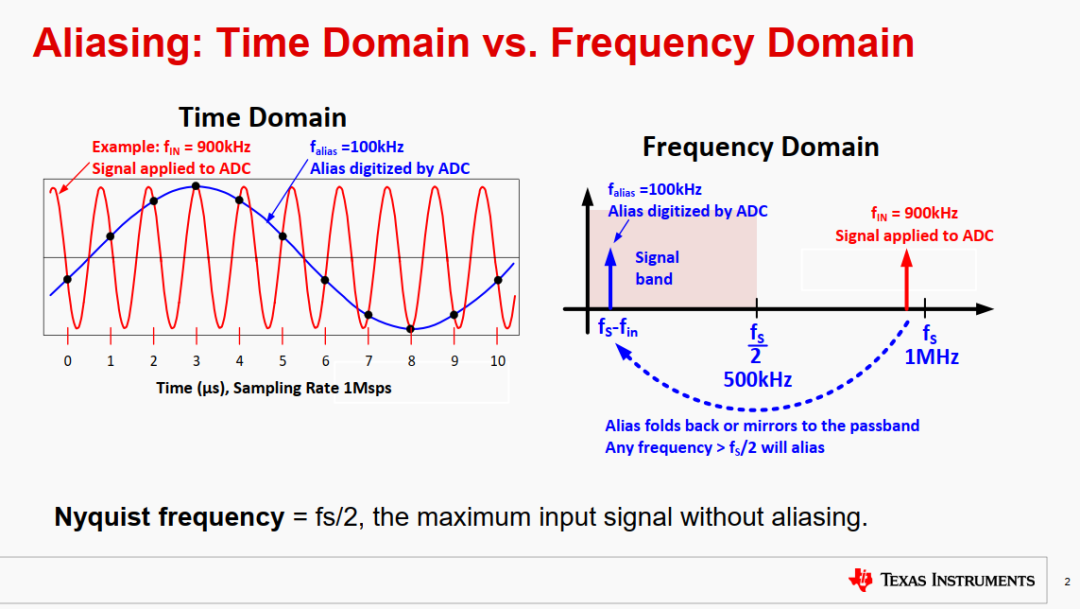

可能大部分应用都是欠采样,输入信号低于奈奎斯特采样频率,即1/2采样率,否则会有混叠问题。

图2 混叠的时域和频域示意图

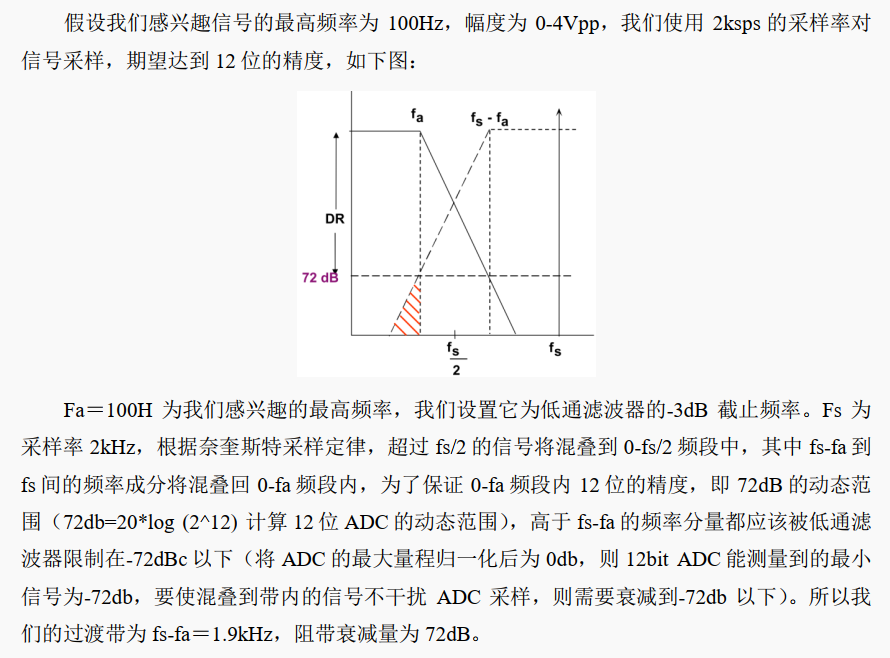

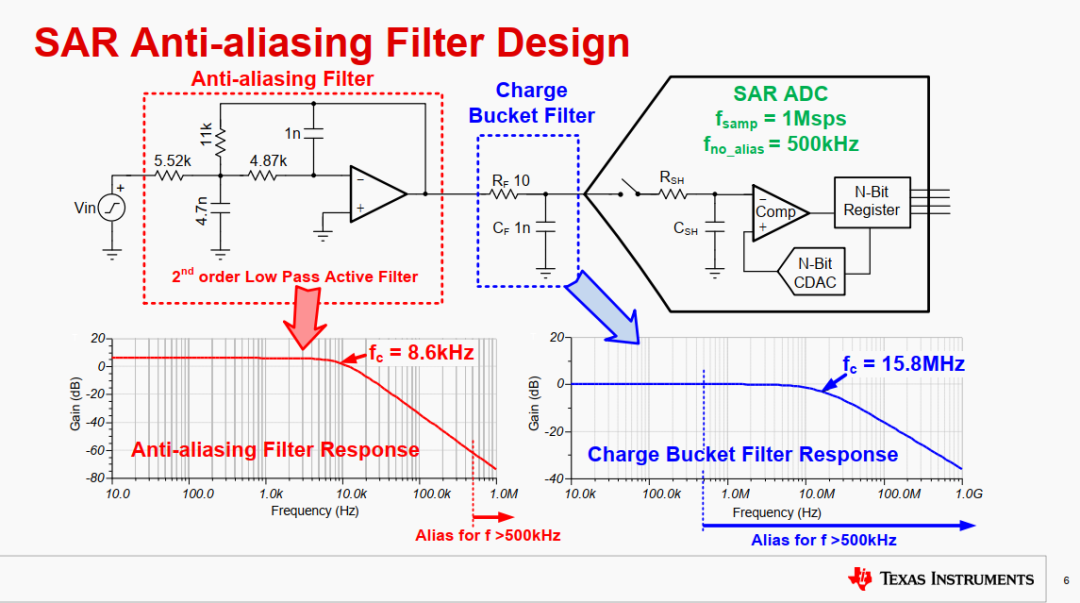

一般ADC前端还需要一个抗混叠滤波器,因为噪声是会高于奈奎斯特频率的,这部分噪声会混叠进输入信号。一个设计例子参见图3。

图3 抗混叠滤波器的设计实例

推荐参考资料为TI precision lab ADC系列中AC规格部分,还有sbaa282a和zhcac38d这两篇文档,都可以在TI官网直接搜到。另外TI的《德州仪器高性能模拟器件高校应用指南 信号链与电源》也很不错。

输入驱动电路

需要特别注意的是,SAR型ADC的前端输入电路(一般是一个跟随器和RC),不是用来滤波的,是用来驱动ADC的。 ADC数据手册中,RC的截止频率一般比信号频率高几十倍甚至上百倍,显然不是滤波用的。因为SAR型ADC的输入极采样保持电路中有个电容,采样周期时,输入信号直接接入到了Csh上,需要快速充电给它,否则会有电压下冲。 采样率越高,设计难度越大 。因此,这部分电路一定要注意。

图4 SAR型ADC的前端输入电路

推荐参考资料为TI precision lab ADC系列中SAR型ADC输入驱动设计,ADI也有个在线工具precision ADC driver tool可以用。

基准源

SAR型ADC的基准源也要格外注意。有些ADC支持外部和内部基准源,一般外部基准源的温漂、精度参数都更好,通常会让ADC性能更好;但是内部基准源简单。

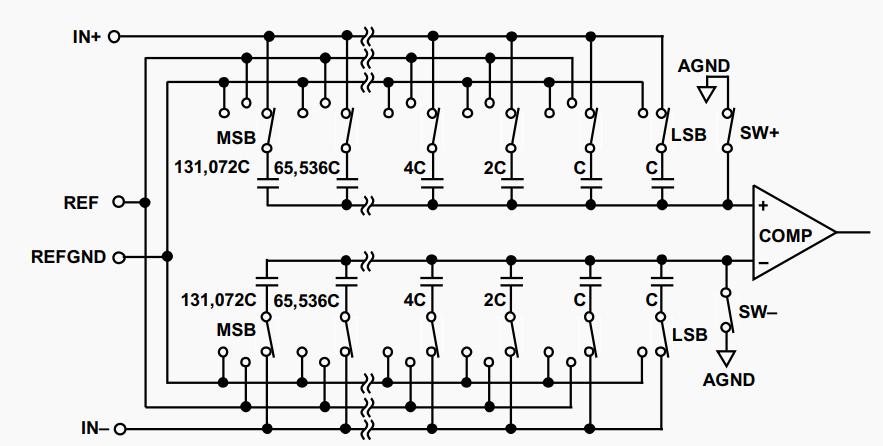

SAR型ADC内部一般都是开关电容架构,内部有比较器逐次比较输入电压与电容上的电压。电容上的电压是怎么的呢?它就是基准源提供的。所以需要基准源的瞬态响应能力特别好,它需要快速充电给电容。精度越高、采样率越快,挑战越大 。不过目前大部分ADC内部是有个buffer的,可以把基准源直接接到buffer输入端,buffer的带宽很高,可以快速充电给电容。有些ADC也提供buffer输出端的接口,这时候就需要自己加buffer了,增加了设计难度。所以建议用内部buffer。对于ADC基准源附近的电容,布局一定要特别注意,越近越好,注意减小ESL。

图5 SAR型ADC的开关电容结构

推荐参考资料为TI precision lab ADC系列中SAR型ADC参考输入驱动,ADI的AN-931文档也很好。

Layout

对于模拟电路来说,PCB通常是电路设计的下一阶段 。高性能的ADC layout一定要格外小心,按照数据手册中的推荐layout设计,以及参考评估板。

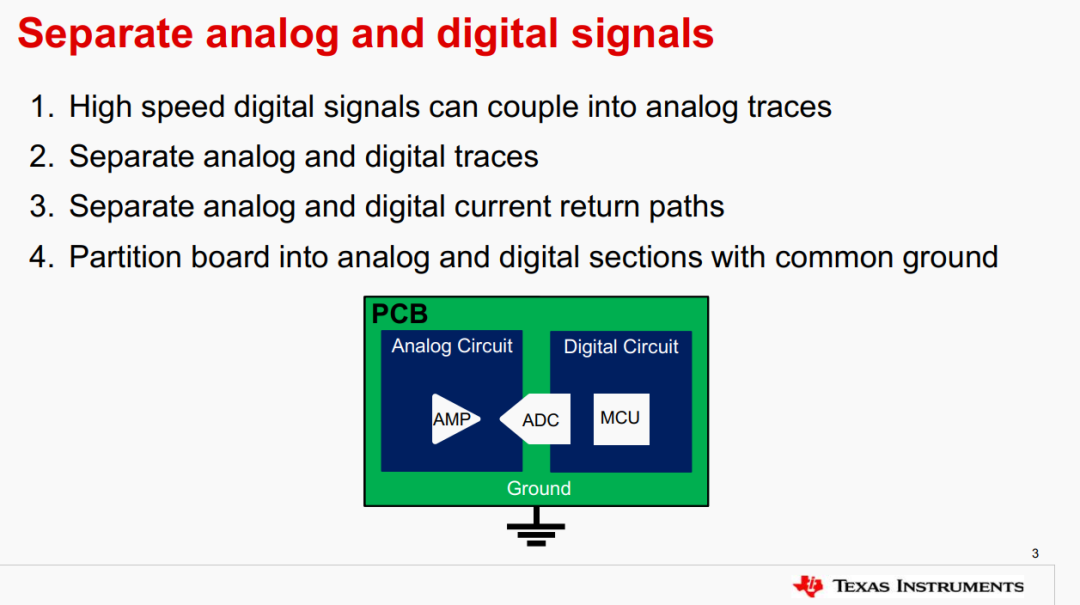

模拟数字混合电路板,一般都会涉及接地这个问题。 接地是个复杂、深奥、非常容易引起争论的问题 。但是TI percision labs中同样给了一个建议,就是模拟数字分开布局,但是不分地。这是实践证明比较有效,且简单的接地方法,参见图6。实际上TI的高速ADC评估板也是这样做的。

图6 TI推荐的一种实践证明有效且简单易行的接地方法

推荐参考资料为ADI的《高速数据转换器电路设计及布板指南》文档,以及TI precision labs中的《op_amp_pcb_layout_mixed_signals_grounding_and_bypass_capacitors》文档。

最后,关于SAR型ADC设计,特别是高速ADC,还有很多很多需要特别注意的地方,比如可靠性的ESD/EOS,高速时钟端接匹配电阻,时钟抖动(一般选外部时钟)等等,本文只是个人的一个小总结,可以作为设计ADC电路的一个小开始。

-

SAR ADC的工作原理是什么?SAR ADC的优点和缺点有哪些?2023-09-08 20994

-

SAR型与Σ-Δ型ADC的区别在哪?2023-08-10 4652

-

高性能全集成SAR型ADC2023-03-31 2131

-

SAR ADC是什么 SAR ADC应用优势2023-02-22 7474

-

SAR型ADC的结构及采样过程2023-02-07 5367

-

SAR型ADC的驱动电路设计2022-11-09 5719

-

SAR ADC的原理以及SAR ADC驱动电路设计要点2022-04-28 21595

-

标准的SAR型ADC驱动电路需要基准及驱动电路2022-01-14 3244

-

哈尔滨站-杨松岩:如何实现SAR型ADC系统的设计与调试(1)2019-08-08 3246

-

SAR型ADC应用2019-08-06 4226

-

AD7767超低功耗SAR型ADC的应用介绍2019-07-29 5570

-

SAR型ADC有哪几种输入类型?其区别是什么?2018-08-13 12401

-

SAR型ADC原理简析2017-12-03 17563

全部0条评论

快来发表一下你的评论吧 !