聊一聊平时咱们等长绕线的方式到底存在一些什么问题?

描述

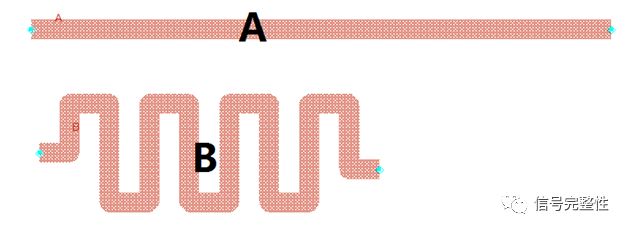

在文章的开头,给大家提一个问题: 相同物理长度的两段传输线如下图所示,一段直线A,一段绕线B,A和B哪一段的延时会更大?

随着高速电路的发展,电路的设计在朝着高速高密度的方向发展。速度和密度高了的话,各种信号完整性、EMI的问题就出来。这也就出现了各种各样的设计要求规则,比如阻抗稳定性、同组同层、等长设计等等。今天咱们就来讨论一个由等长而引发的一个设计问题,即绕线设计,

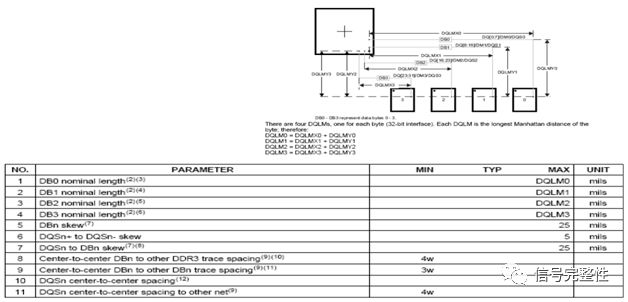

在设计中,特别是DDR3/4/5这类的设计,总会有很多的信号线存在,每一组的数据或者地址控制命令信号线都有一定的等长要求,如下所示为某芯片手册的要求:

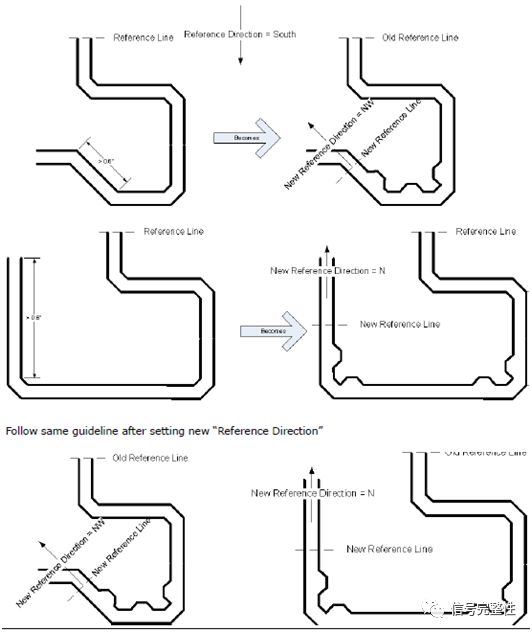

在设计时,当达不到要求时,工程师首先想到的都是绕线,然后还出现了非常多的绕线方式。如下图所示(此图来自Intel PDG):

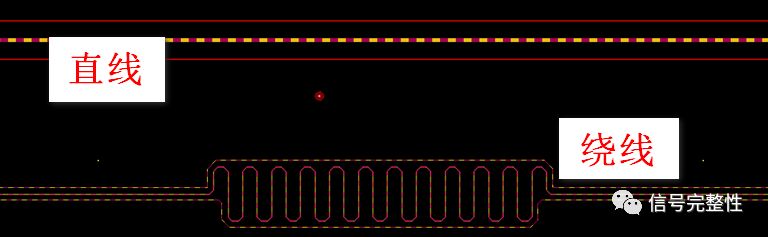

本文就和大家聊一聊平时咱们绕线的方式到底存在一些什么问题?为了完成这个问题的研究,特意做了一个测试板,设计了研究对象为10inch的传输线,一段做参考为直线(上),一段为绕线(下),如下图所示:

一般,大家通常都会认为,这样已经算等长了,而且是完全等长。但是,通过测量其传输特性,测量的结果如下图所示,我们可以看到,其差异还是不小,相差了12.73ps(红色圆圈),而且绕线比直线传输的更快。

这12.7ps换算成物理长度,约为80mil。80mil的长度应该是让有经验的工程师吓一跳,毕竟平时硬件工程师说:给我做好等长,误差在2mil的时候都会跳起脚来大骂。

当然,我们这里做实验设计的为10inch,通常很多布线都没这么长,但是也有一些布线确实非常长的。

但是,不管怎么样,这个实验都告诉了我们,物理等长,不等于实际设计就等长了。这也是为什么,近年来,业界一些厂商都提倡时序等长的原因。

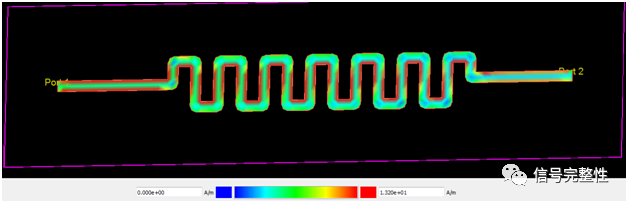

这是为什么呢?原因就在于绕线之后,由于趋肤效应和电磁场效应,信号都是在表面传递。为了解释此现象,在ADS中设计了一段绕线,进行了电磁(EM)仿真,结果如下图所示:

从上图中,我们可以看到,在绕线的地方,都是在相对比较紧耦合处场电流密度比较大,呈红色,在上方(与传输线平行)以及传输线的中心处,电流密度比较小,呈浅色,这就说明信号靠近边沿处传递,这样就导致了信号传递的“更加快速”,所用的时间更少(本来可以给大家放一张动态图的,但是没能做好,有机会的时候,再给大家show一下)。

而直线的仿真结果如下图所示(长度太长,所以只截取一部分):

通过以上的分析即可说明,相同的物理长度,绕线的一段延时更小,这样,我们就能回答前面提出来的问题了,显然是A的延时更大(在上文中也说了绕线更快)。

那么问题又来了,工程师在设计时遇到不“等长”的时候,如何做好设计呢?

第一,把物理等长的观念改为等时,及不管绕线还是直线,需要的是传输延时是一样的。有的PCB设计工具是可以使用时间来表示物理长度的;

第二,有时序关系的信号线,在设计时做到同进同出同设计,尽量减少绕线;

第三,如果某一段传输线确实要绕线,绕线的形状大一点,波与波的距离大一点,或者绕的比直线更长一点,至于绕多长,我也不知道,还是请工程师进行下仿真吧(这也就是为什么要进行后仿真了)。

当然,好的、方便的设计方法非常多,此为抛砖引玉,希望大家把好的方法也分享出来,有兴趣的也可以进一步的与我交流探讨。

编者注:这种绕线的研究,并不是说每一种总线设计都需要这样做,对于一些低速信号、对时序没有特别要求的信号或者对EMI没有特殊要求的项目,工程师可以不用考虑。以上内容仅供参考。

审核编辑:刘清

全部0条评论

快来发表一下你的评论吧 !