电磁干扰(EMI)如何减轻PCB上的电磁干扰

EMC/EMI设计

描述

电磁辐射是指穿过空间的电磁能波。

我们都熟悉无线电、微波、光和X射线等术语——这些都是不同频率的电磁辐射。我们用眼睛看到的光只是电磁光谱的一小部分,大约400-700太赫兹(THz)。

无线电波指的是KHz和GHz范围内的频率,包括WiFi、蓝牙、移动电话通信、卫星通信,当然还有调频广播。

当然,根据上面的例子,无线电波和通信非常有用,但是我们的电子设备有时也会产生无意和不想要的辐射,这会干扰其他设备及其有意的通信。当邻居打开微波炉时,我们不希望我们的WiFi停止工作。

在极端情况下,电磁辐射可以被武器化,例如用电磁炸弹产生的电磁脉冲,或者用无线电干扰器故意干扰通信。

就我们的电子设备而言,EMI(电磁干扰)和EMC(电磁兼容性)指的是我们的设备在电磁辐射方面表现如何。这通常是指无线电波范围内的EM,因为我们的电子设备通常以KHz、MHz和GHz范围内的时钟频率工作。

EMI是指我们的设备发出的意外电磁辐射(可能会干扰其他设备)。

EMC指的是我们的设备在电磁辐射方面表现如何。

就EMC而言,我们需要知道,我们的重要设备(医疗设备、车辆引擎管理系统等)即使暴露在一定量的有害电磁干扰下,仍将继续正常运行。

就EMI而言,请注意,任何电流切换的所有电子器件都会产生至少一定水平的电磁辐射,但我们需要将这些辐射保持在一定水平以下,以符合法定标准。

产品认证

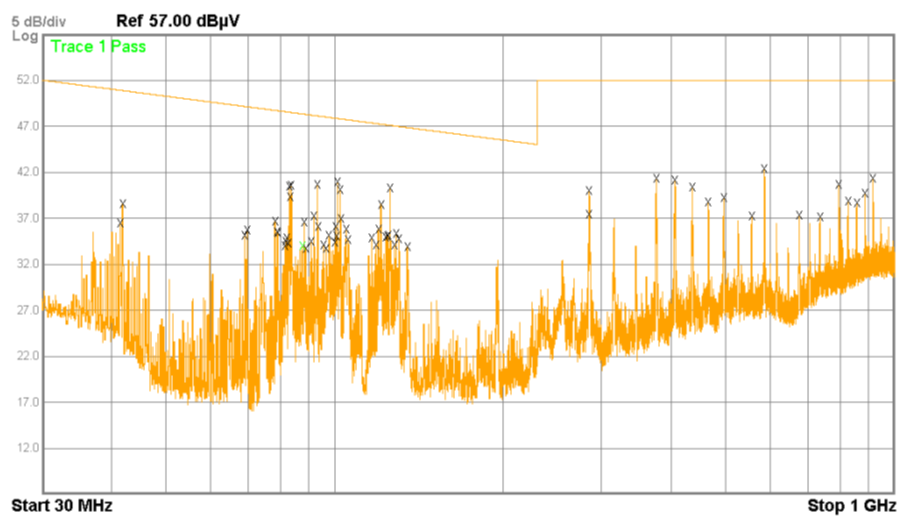

为了获得我们产品的认证(在某些市场销售时可能需要),通常需要通过EMI/EMC测试,该测试由经过认证的测试机构执行。EMI辐射测试可能如下所示:

EMI辐射发射测试波特图。

这是一个波特图或频率分析图,其中横轴代表频率,纵轴代表幅度——它显示了一个频率范围内的辐射幅度(参见我们的傅立叶变换文章)。为了通过测试,所有排放必须低于顶部橙色线所示的水平。

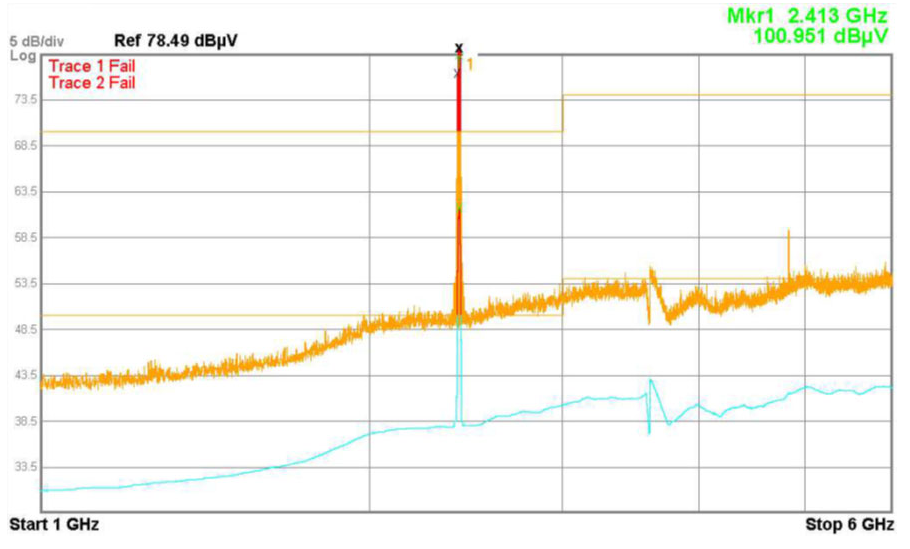

如果排放高于规定限值,则该装置不能通过测试:

排放超标-设备故障。

测试在标准化条件下,在一个特殊的试验箱中进行:

天线接收设备发出的辐射,频谱分析仪将它们标绘在图上。

EMI/EMC兼容设计在某种程度上与无线电设计相反。我们希望确保我们的设备不是收音机(至少除了我们特别希望它处于特定频率的地方,例如如果我们的设备通过WiFi进行通信)。众所周知,收音机需要天线。当交流电连接到天线时,天线会发出电磁辐射(EMI),当天线接收到电磁辐射时,会产生电压/电流(EMC)。

从技术上来说,电磁辐射是由正在加速的带电粒子发出的(这发生在电流改变方向,或者开始和停止的时候)。EMI/EMC设计需要注意系统中的交流(开关电压/电流)元件,以及系统中可能充当天线的走线(导线)。

一般来说,实现良好的高速设计技术(参见我们的高速PCB设计介绍文章)也将有助于EMI/EMC。

返回电流

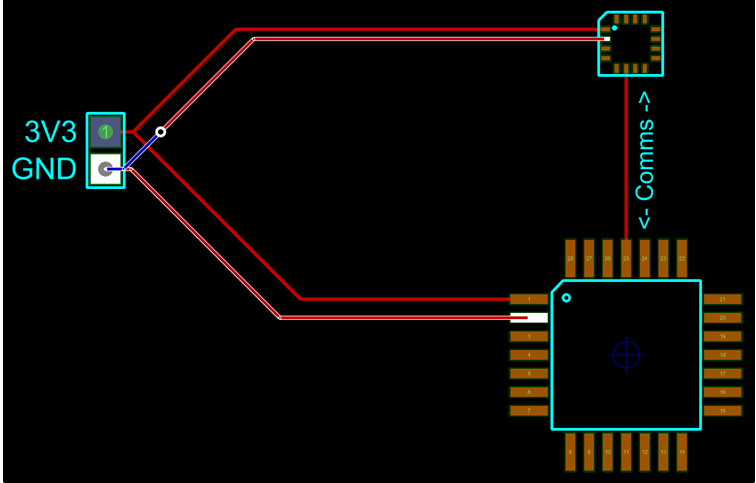

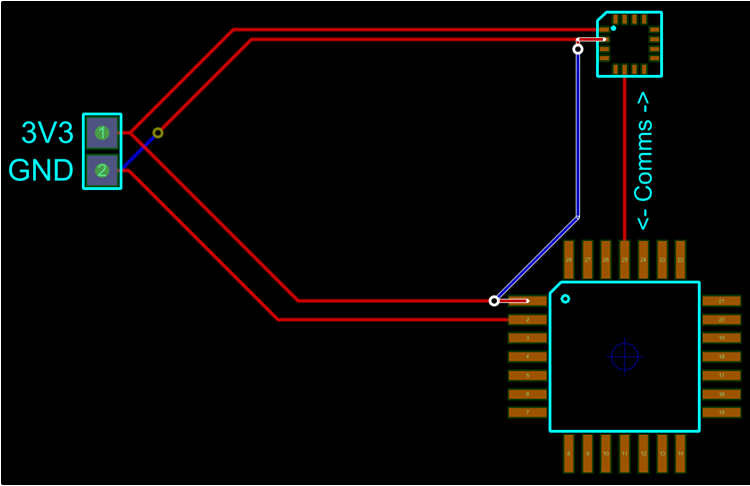

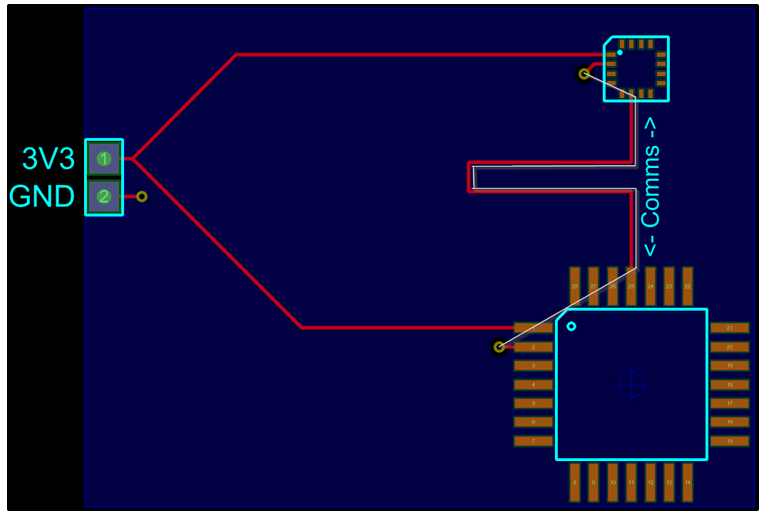

我们可能没有想到这一点,但我们板上的每个信号都必须有一个返回路径。通常这是通过电力网,如地面(GND)。考虑以下场景:

我们的板上有两个相互通信的器件(比如一个微控制器和一个传感器)。它们之间的通信线路相对较短,从概念上讲,当我们考虑设备之间的通信时,这通常是我们所关注的全部内容;但是,通信线路也必须有一个返回电流,这是通过一条电源线来实现的,可能需要更长的路径。更长的路线意味着更大的天线。在进行EMI/EMC设计时,我们还需要考虑返回电流路径(电源线),并尽量缩短路径(更小的天线)。

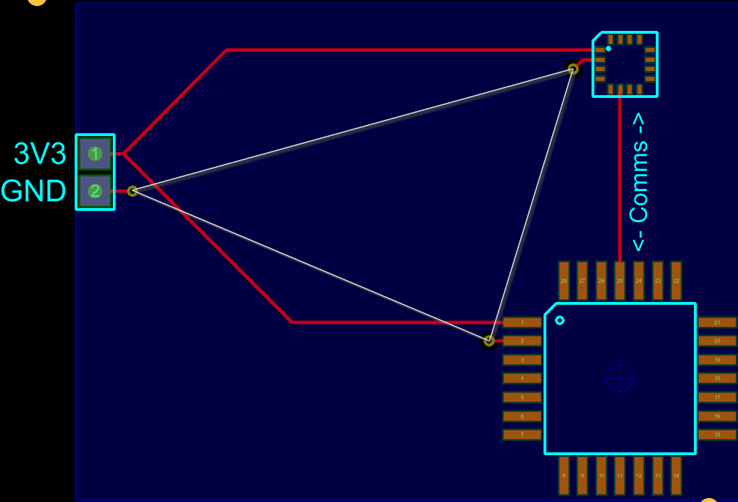

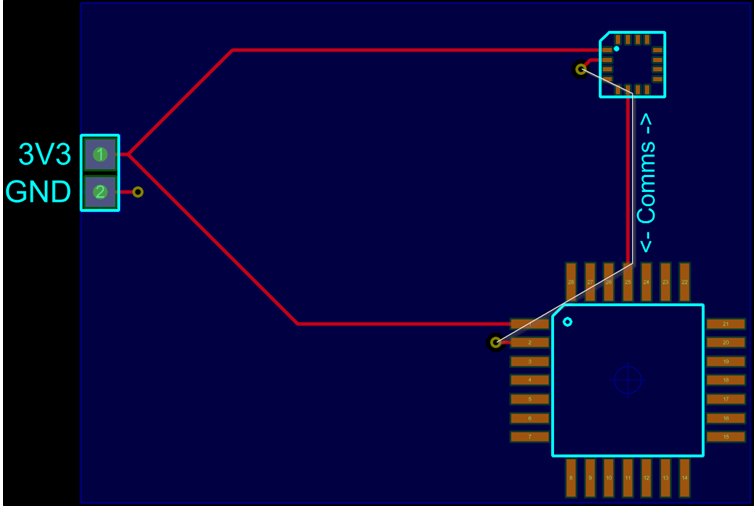

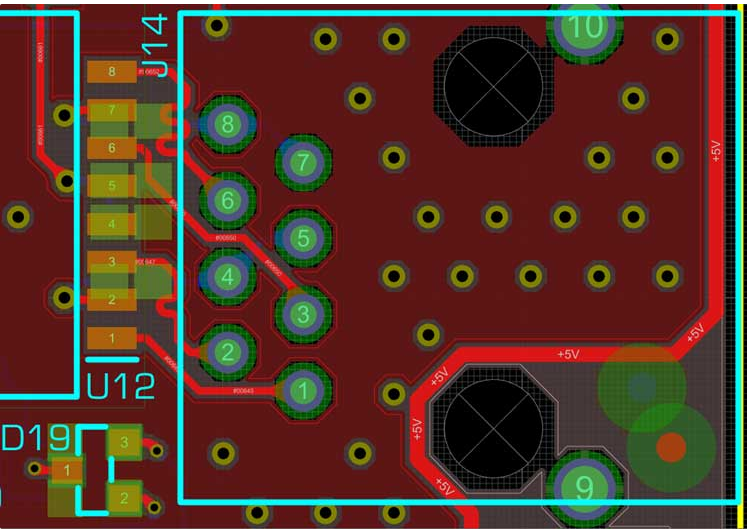

实施高速设计原则时,通常涉及4层以上的电路板,我们通常使用内层作为电源层。只需在器件附近的电源层增加过孔,我们就可以确保电流返回路径较短(电源层用蓝色表示,白线表示概念性电流路径):

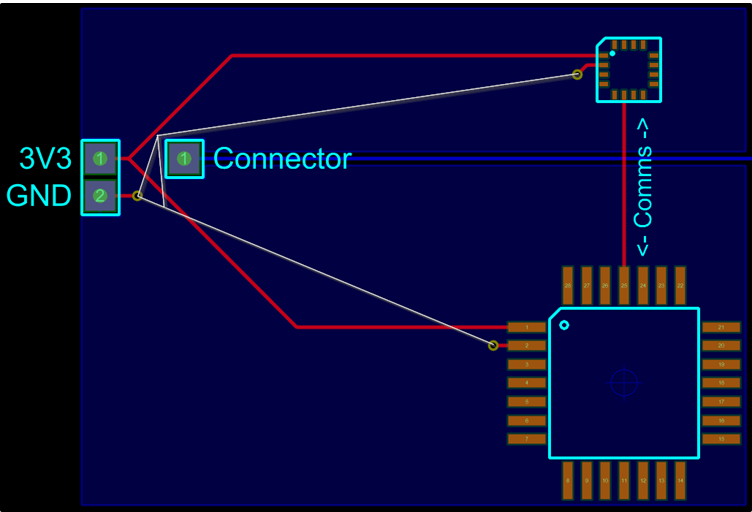

我们应该小心,确保电源层中没有可能再次导致更长电流路径的断点(同样,白线表示概念性电流路径):

同样,这符合确保高速线路阻抗恒定的高速原则。

最小阻抗路径

说到阻抗;有趣的是,直流电流(DC)遵循最小电阻的路径,而交流电流(交流)遵循最小电抗(阻抗)的路径。当我们考虑电抗是电阻的交流等价物时,这是有意义的。如果你不熟悉电抗/阻抗,那么请查看我们关于无源滤波器的文章。随着频率的增加,电抗的电感成分起着更大的作用,电流基本上开始沿着电感最小的路径流动。这意味着,随着频率增加,电流实际上会直接在相关信号线下方流动:

这就是为什么高频线路下方的电源层必须保持完整。即使信号线遵循一条奇怪的路径,在较高频率下,返回电流仍会直接在其下方通过:

去耦电容

随着电路板上元件所需的电流发生变化(例如,CPU突然需要更多功率来进行复杂计算),电路板上电源走线中的电流也会发生变化,再次将这些走线变成天线。通过在电路板上放置足够多的去耦电容,并尽可能靠近相关元件,我们可以尽可能地降低这种影响。从另一个角度来看,去耦电容在电源和地之间提供一条低阻抗路径,以便交流电流流过。你可以阅读更多关于去耦电容在这篇博客文章中。

通过缝合

过孔拼接是指在不同的电路板层上放置多个过孔,连接两个(或多个)电源层。

虽然我们在概念上认为电源层是相连的,即使它们仅通过电路板角上的一个过孔相连也是相同的,但不断变化的电源需求和电磁辐射实际上可能会导致两个(或更多)电源层之间的电压略有不同。通过在电源层放置拼接过孔,我们可以确保任何可能出现的电压差都可以通过短电流路径解决,从而再次缩小天线的尺寸。

压摆率

压摆率指信号上升或下降的速度。我们可能在概念上认为电压电平会瞬间变化,但事实并非如此,电压从一个电平转换到另一个电平总是需要一定的时间。非常快速的转变导致带电粒子在短时间内加速,因此产生更高的电磁辐射。另一种看待这个问题的方式是,根据傅立叶变换(参见我们的傅立叶变换文章),信号的边缘越方,它包含的高频分量就越多。出于这个原因,一些微控制器具有可调的压摆率,以降低信号转换的速度,并减少信号边沿的方形度。降低压摆率(在实际所需信号频率所需的速度范围内——我们不能对1GHz信号进行1ns的压摆率,因为1GHz的频率周期为1ns)可以减少电磁辐射。

蹒跚

一些具有宽通信总线的IC可以选择错开总线内各条线路的开关。交错切换,而不是一次切换所有线路,有助于将产生的电磁干扰分散到整个时间,从而将任何给定时刻的总电磁干扰降低到可接受的水平。

防护的

就EMI/EMC而言,屏蔽通常是第一个想到的解决方案,但实际上,在解决上述问题后,它通常应该是最后考虑的问题。信号可以从甚至很小的缝隙中逃逸,例如PCB的侧面,屏蔽有时相当于试图用大量的胶带来固定一个机械产品。也就是说,屏蔽确实有它的位置——在没有首先确保正确的PCB设计的情况下,它不应该是首选的解决方案。

EMI/EMC设计包括考虑系统的交流(开关)元件,并采取措施减小电流环路的尺寸。通常,考虑到高速设计原则的设计也会具有良好的EMI/EMC。确保高速走线下的电源层不间断、充分利用去耦电容、开关IC周围的电源层过孔以及尽可能保持高频走线相对较短等原则将有助于改善EMI/EMC。例如,DC-DC转换器电路应尽可能小而紧凑,附近应有良好的去耦电容。EMI/EMC不合格的2层设计可以通过,只需将内层接地层改为4层,并在IC附近缝合过孔即可。可采取的进一步措施包括查看电路板产生的特定频率并追踪其来源,使用近场探头等工具查明发射源,使用TEM cells进行快速认证前测试并查看硬件和软件变化的结果,以及使用其他EM分析工具,如EM扫描仪;这些可能是另一篇文章的主题。

审核编辑:黄飞

-

EMI电磁干扰如何减少2024-11-20 3707

-

EMI电磁干扰厂家:如何专业解决电磁干扰问题2024-05-13 1269

-

EMI电磁干扰:EMI电磁干扰的识别与解决之道2024-04-25 2821

-

EMC与EMI:电磁兼容与电磁干扰的原理与影响2024-04-09 2176

-

EMI(电磁干扰)对策有哪些?2023-02-08 4723

-

EMI电磁干扰的来源和分类2022-01-06 1060

-

EMI电磁干扰有哪些类型2021-12-28 1917

-

EMI电磁干扰的传播过程2019-05-31 1882

-

如何降低PCB板设计时的电磁干扰EMI2019-03-26 2065

-

教你减少PCB板电磁干扰的设计技巧2018-09-18 1397

-

电磁干扰(EMI)与电磁耐受(EMS)2018-09-03 4714

-

电磁干扰(EMI)与电磁耐受(EMS)问题2018-08-28 4209

-

电磁干扰是什么?2017-01-12 4217

-

电磁干扰的PCB设计方法2009-04-07 1323

全部0条评论

快来发表一下你的评论吧 !