系统解复位的特殊处理

描述

书接上文嗷接上文。

【芯片设计】复位那些小事 —— 异步复位,同步撤离

解复位就是复位撤离,系统解复位就是复位结束了系统准备开始工作。

前文咱们提过,复位撤离比复位要复杂一些,因为复位了大家就是一起回到初始状态去,寄存器也不采样了,有什么毛刺啊亚稳态啊只要不影响其他系统(这个之后讲)都没关系的。这就相当于晚上回家上床准备上床睡觉,你爱穿啥衣服睡就穿啥衣服不穿也没人管。但是解复位就不一样了,这就是起床要出门上班了,怎么着也得准备好才能出去工作,不能穿着秋裤就往外跑。

所以的对于解复位(其实也不光是解复位,局部复位本身也很危险)就需要做跟多的额外工作了,上一篇说的同步撤离之后,还有什么问题需要解决呢?

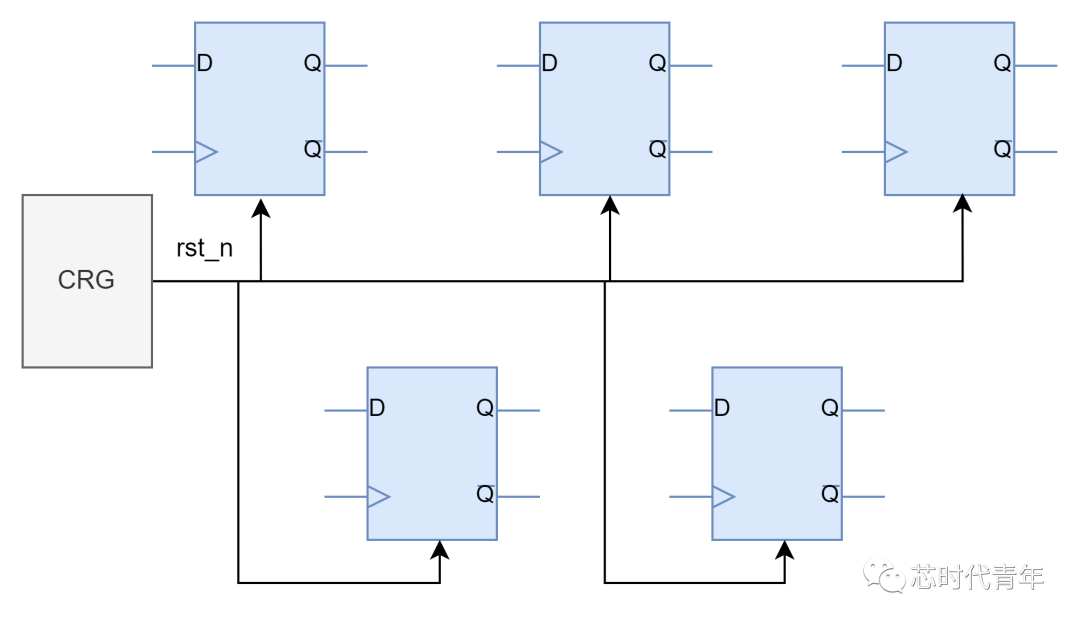

主要是复位信号到达各个寄存器的时间不一致的问题。复位信号在系统内是有很大的扇出的,连接到所有需要复位的寄存器的复位端。这也就导致了复位在系统中的走线特别长,过长的走线又会导致工具在复位信号上增加buffer以提升驱动能力,那么如果时钟频率很高,复位信号最终到达各个寄存器的时间也就无法保证在同一拍。

复位走线到达各个寄存器不在同一拍会有什么后果呢?这个不能一概而论。对于一些复位解除后就开始工作的电路系统比如自动计数取指模块,各个寄存器之间可能存在依赖关系,如果只部分寄存器被复位或解复位,可能会导致不一致的状态,从而影响系统的正确运行。同时呢,如果复位方案做的不好,某系统进行复位时一部分复位了一部分没有复位,也可能会产生毛刺被未复位的寄存器采样,进而输出使能影响到其他系统的正常工作。

总之呢,复位走线到各个寄存器不在同一拍,可能存在系统稳定性的风险。因此在对复位还需要对系统的复位做一些特殊的处理。特殊的处理有哪些呢,不同的团队也有多种多样的选择,这里列举一些我所听闻过的方案吧。

降频后复位。

先把时钟降频,再进行复位和解复位的操作,再提频回正常工作时钟频率。你不是怕复位走线到各个寄存器的时间不一致导致不在同一拍复位吗?那好,我把时钟降频总可以吧,1GHz太快了降到500M,500M还快降到100M,100M还快到10M总可以了吧,一个周期这么长时间足够你复位信号慢慢溜达到各个寄存器的。所以采用这种方案时,会在复位前将工作时钟32分频或者64分频(取决于系统的面积和工作时钟,可以算的),然后进行复位和解复位,之后在将时钟提频至工作状态。

这种方案下,可以在sdc中将复位信号设置为multicycle,检查其在64个时钟周期内能够作用到所有的寄存器复位端。

关时钟后复位。

这个方法更彻底,怕各个寄存器看到复位和解复位的时间不一致导致功能错乱?那直接把工作时钟给关断不久好了,反正是异步复位不用担心没有时钟复位信号作用不到寄存器端。时钟一关所有寄存器相当于原地停工,这个时候别说复位信号了,啥信号过来都没事,寄存器都不干了嘛。所以此时复位信号的走线也就不称问题了,先复位再慢慢悠悠的解复位,都搞定了歇一会再把时钟打开。

这种方案下,可以在sdc中将复位信号设置为false_path,毕竟相当于准静态的信号,工作时复位信号不会跳变。

复位保护。

这个方法的思路是,不是担心我这块的复位影响其他系统工作嘛,那么不去处理复位和时钟,而是把系统裹起来。怎么裹起来呢,把所有的对外输出使能啊、握手啊这类信号都先和低电平与在一起,保证不管一会发生啥事,都不会有关键信号发生跳变。保护好之后,再去拉复位信号,过一会再解复位,再等会时间等系统稳定下来了,再把保护电路解除开始正常工作。

这种方案下,也可以在sdc中将复位信号设置为false_path。

复位之后等待一定时间再开始下任务。

这个方案更多的是在任务层面看,也就是说面对解复位后可能存在的系统不稳定性,先不要着急下任务下配置下指令,而是等待一定时间等系统中可能存在的不稳定状态都结束了,再开始进入工作模式去下任务。

当然了不是说所有系统都适用以上的方法,比如某个系统确实是解复位后就立即开始工作,那用复位保护就没效果,因为你内部状态都乱了保护其他系统还有啥用呢。所以说还是具体问题具体分析吧,以上也只是经验之谈难免有所疏漏。

审核编辑:汤梓红

-

GD32 MCU电源复位和系统复位有什么区别2024-02-02 2717

-

对于芯片中的复位信号我们通常会有哪些特殊处理?2023-12-25 4929

-

复位那些小事—系统解复位的特殊处理2023-12-04 3405

-

stm32软复位 内核复位和系统复位2023-08-01 7047

-

STM32芯片的那些系统级复位功能2022-10-19 6839

-

STM32复位来源、以及系统和内核复位区别2022-02-10 883

-

引起处理器和系统复位的原因有哪些呢2022-01-17 737

-

复位系统组成部件2021-08-02 1463

-

基于Xilinx FPGA的复位信号处理2020-12-25 3442

-

CM3(STM32) 内核复位与系统复位区别及应用2020-03-20 6362

-

STM32复位来源 以及系统和内核复位区别2020-02-28 9136

-

请问ADUC7060的复位电路有特殊要求吗?2018-11-16 2222

-

stm32复位电路设计 浅析stm32复位电路方法2018-08-08 102405

-

特殊尺寸机器人的位置反解算法2011-06-24 817

全部0条评论

快来发表一下你的评论吧 !