d触发器有记忆功能吗 D触发器的基本原理

描述

d触发器有记忆功能吗

D触发器(D flip-flop)可以存储一位二进制数据的状态,因此具有记忆功能。D触发器通常用于数字电路中,用于实现寄存器、计数器等电路,可以通过时钟信号进行同步操作,使它们可以存储和操作二进制数据。值得注意的是,D触发器只能存储一位二进制数据,如果要存储更多的数据,则需要使用多位寄存器。

D 触发器

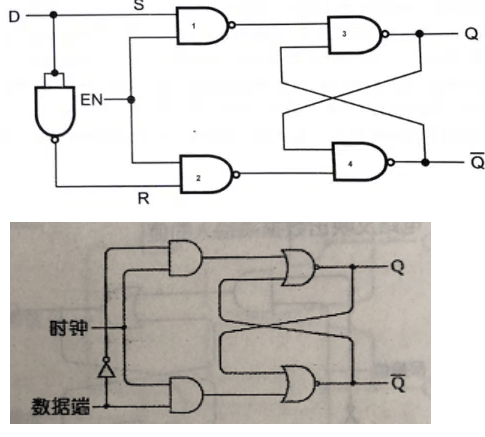

采用与和或非的D触发器功能是一样的,但都是或非元件减少对元件种类的要求。

SR latch:S输入端水平对面的是Q非端,但锁存的数据是出现在Q端;D flipflop的S端水平对面就是Q端,因为中间加了元件。

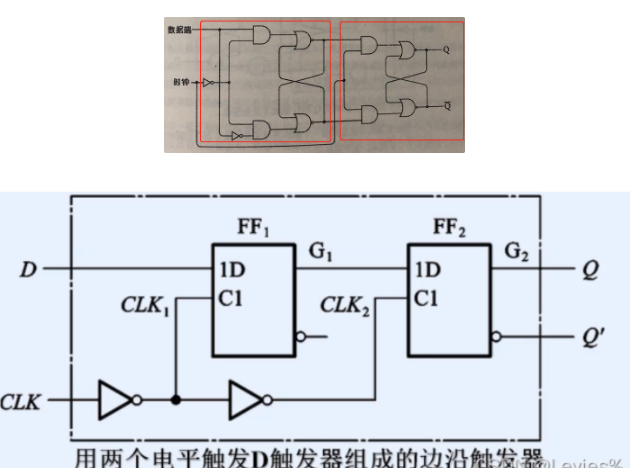

边沿触发的D触发器需要两个电平触发的D触发器组合而成,原理就是第一级的D触发器随着电平改变了输出,但第二级需要等到高电平的到来才能改变,也就是时钟的跳变。

D触发器的基本原理

D触发器是数字电路中最常用的触发器类型之一,它用于存储一位二进制数据的状态。其基本原理如下:

D触发器由两个交叉耦合的反相器(也称为非门)组成,常用的形式是由两个NAND门构成。这两个NAND门的输出分别连接到对方的输入端,形成一个正反馈回路。

D触发器具有一个输入端D(Data)和一个时钟输入端CLK(Clock)。当时钟输入为高电平(上升沿或下降沿)时,D触发器会根据输入端D的值来改变其输出。

具体操作如下:

1. 当CLK为低电平时,D触发器处于暂存状态,输入信号D不会被传递到输出。

2. 当CLK为高电平时,D触发器被使能,此时输入信号D的值会被传递到输出。

3. 在CLK的边沿(上升沿或下降沿)上,D触发器会将输入信号D的值保持到输出端,即存储起来。D触发器的输出保持在这个状态,直到下一次时钟边沿到来,并依据新的输入值进行更新。

总结一下,D触发器在时钟边沿发生时将输入信号D的值传递到输出,并在时钟保持期间保持该值。这使得D触发器能够存储输入信号的状态,具备记忆功能。

D触发器的输出会受到时钟的控制,只有在时钟边沿的瞬间才会发生变化。

审核编辑:黄飞

-

d触发器是电平触发还是边沿触发2024-08-22 3324

-

t触发器与d触发器的区别和联系2024-08-11 7415

-

d触发器的功能 d触发器的状态方程2024-02-18 18422

-

d触发器有几个稳态 d触发器和rs触发器的区别2024-02-06 6365

-

比较器和施密特触发器的基本原理2022-04-11 17625

-

D触发器基本原理2019-07-12 103105

-

主从sr触发器基本原理分析2018-02-08 64046

-

D触发器组成T和J-K触发器电路图2010-09-20 22046

-

D触发器,D触发器是什么意思2010-03-08 5401

-

D触发器/J-K触发器的功能测试及其应用2009-02-14 5551

-

D触发器2008-10-20 3210

-

JK触发器 D触发器 RS触发器 T触发器 真值表2007-09-11 20478

全部0条评论

快来发表一下你的评论吧 !