硬件电路设计之DDR电路设计(4)

描述

1 简介

DDR4(第四代双倍数据速率同步动态随机存取存储器)是一种高带宽的存储器,今天主要讲述一下DDR4在Layout过程中的一些细节。在DDR的设计过程中,DDR的Layout是十分重要的环节。

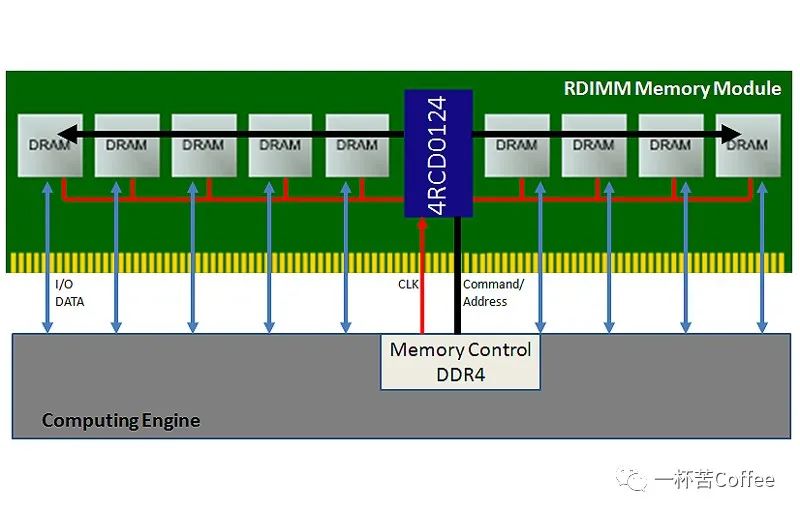

2 DDR4的拓扑结构

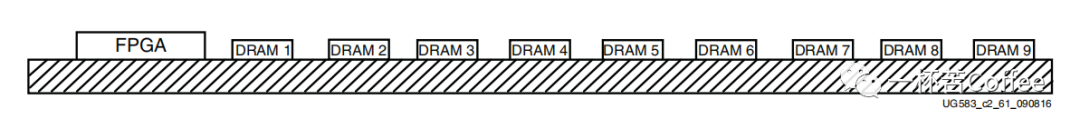

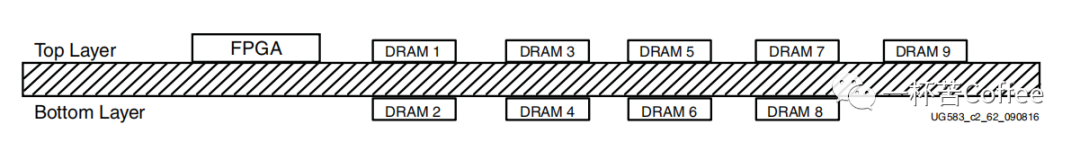

DDR4 SDRAM支持两种拓扑类型:FLY-BY和Clamshell。

FLY-BY拓扑结构

FLY-BY拓扑结构将所有存储设备放置在同一层(详见下图),这种拓扑结构更有利于数据通信,并且可以提供最佳的信号完整性,但是会占用宝贵的电路板空间。

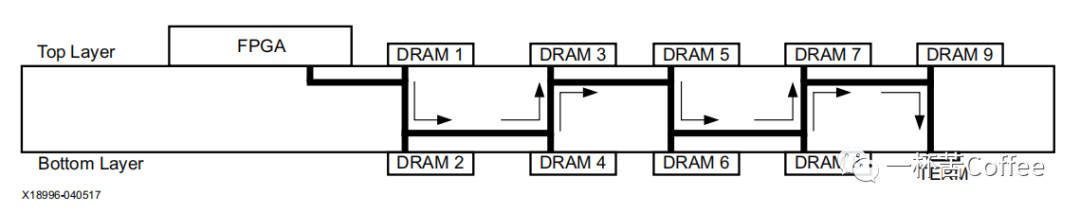

Clamshell拓扑结构

Clamshell拓扑结构将存储设备可以同时放置在TOP层和BUTTON层(详见下图),相对于FLY-BY拓扑结构,这种拓扑结构不利于数据通信,但是能节省大量的电路板空间。

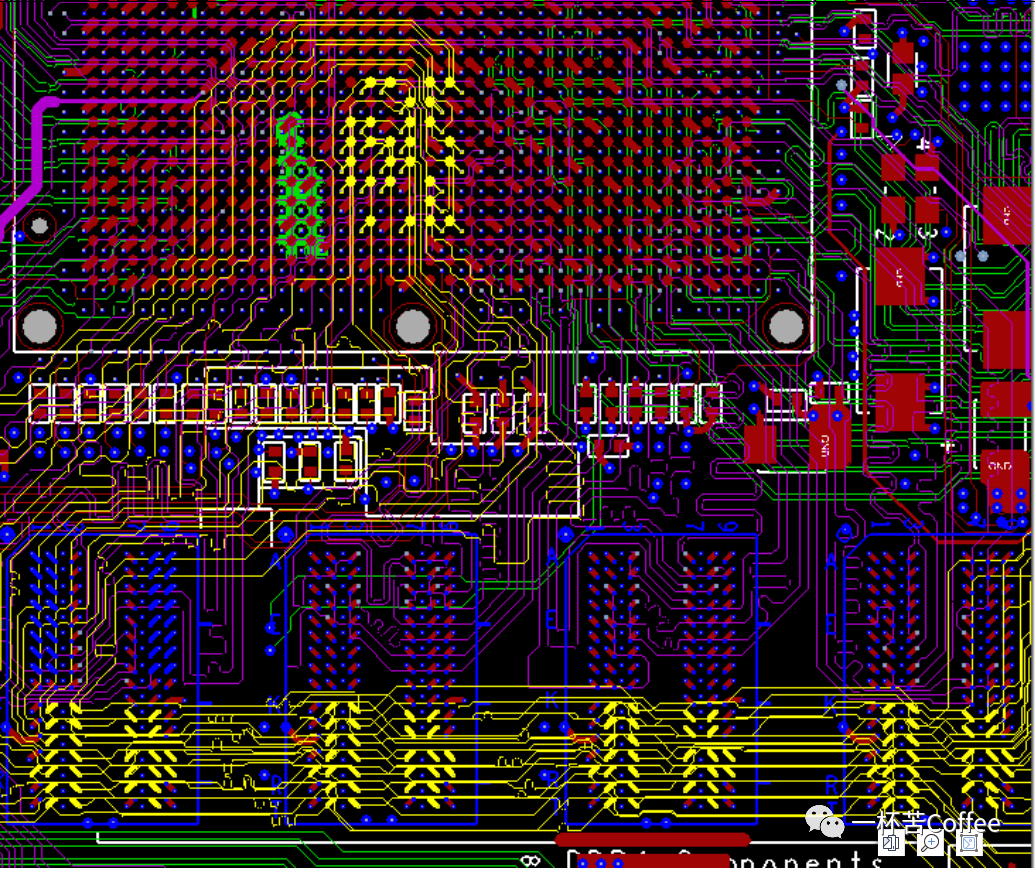

3 Layout要求

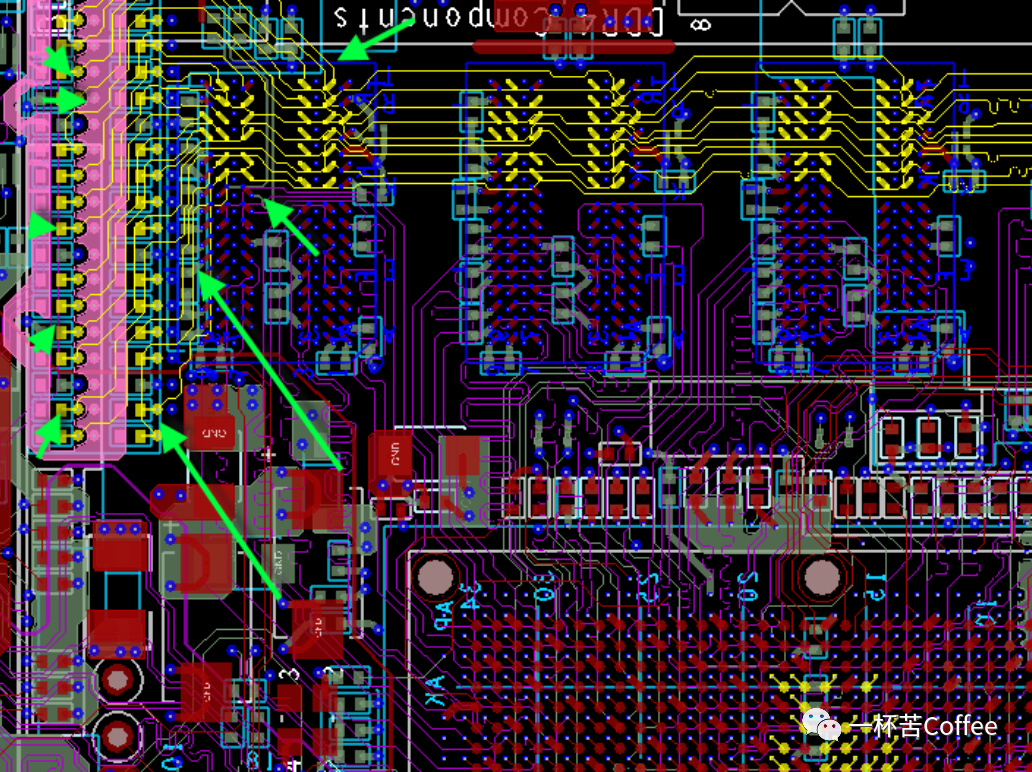

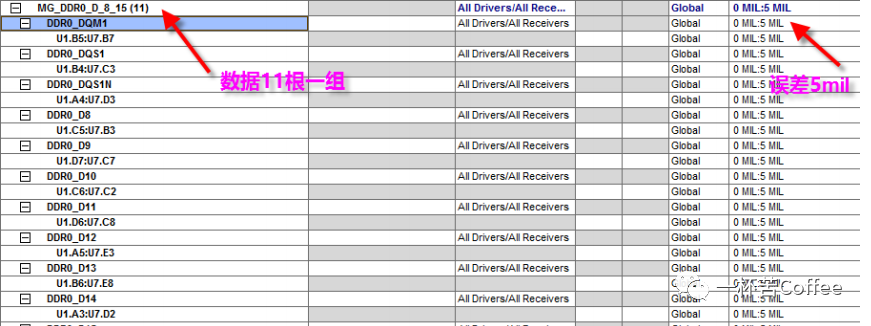

信号分组:

- DQ[7:0]、DQM0、DQS0(Diff)为一组(共是11根信号线);

- DQ[15:8]、DQM1、DQS1(Diff)为一组(共是11根信号线);

- 所有的地址线、时钟线以及控制线为一组。

阻抗控制:

- 单端信号的阻抗控制在50欧姆;

- 差分信号的阻抗控制在100Ω。

3.1布局要求

地址线布局布线要求优先选择Fly-BY拓扑结构,鉴于地址线一般不会走在表层,所以出线后打过孔。过孔到引脚的长度尽可能短,长度在150mil(3.81mm)左右。

地址线和控制线的上拉匹配电阻放置在最后一个颗粒的末端,与颗粒的走线长度不要超过500mil(12.7mm),并且每个上拉电阻都要放置一个对应的VTT滤波电容(0.1uF),最多可以两个上拉电阻共用一个滤波电容。

3.1布线要求

走线要求

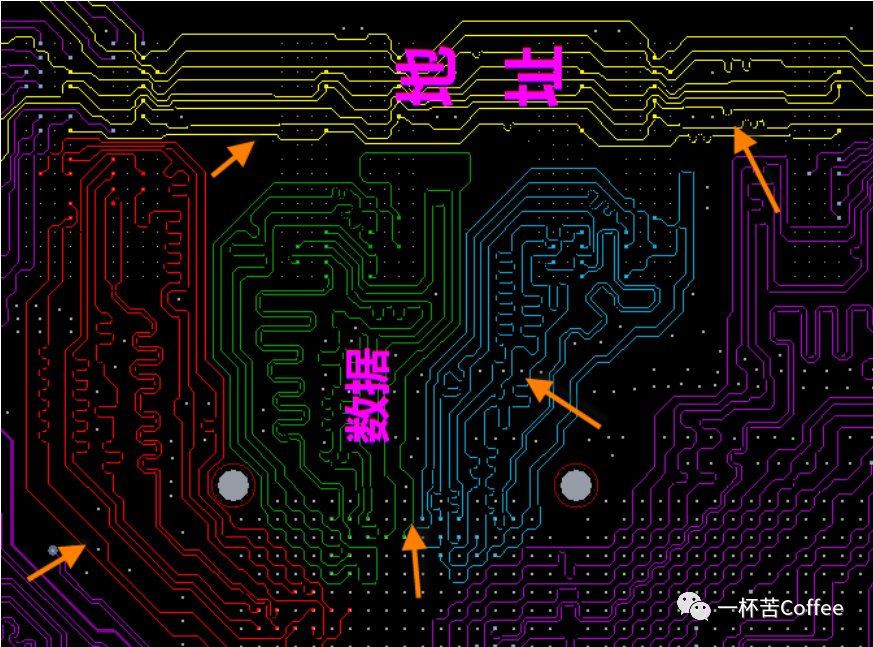

8根同组DQ数据线必须保证同层,DQM0、DQS0(Diff)有效保证与DQ数据线同层。另外地址线、控制线、以及时钟线按照FLY-BY拓扑结构走线。

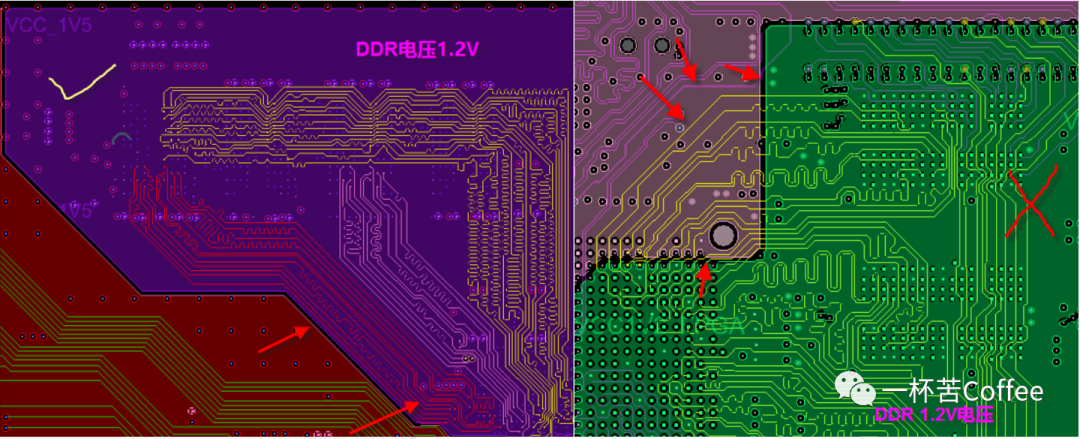

平面分割要求

为了保证电源完整性和信号完整性,DDR4的走线必须有完整电源参考平面,坚决杜绝跨分割现象,叠层时考虑让地平面紧挨着电源平面,保证电流回流路径最短。

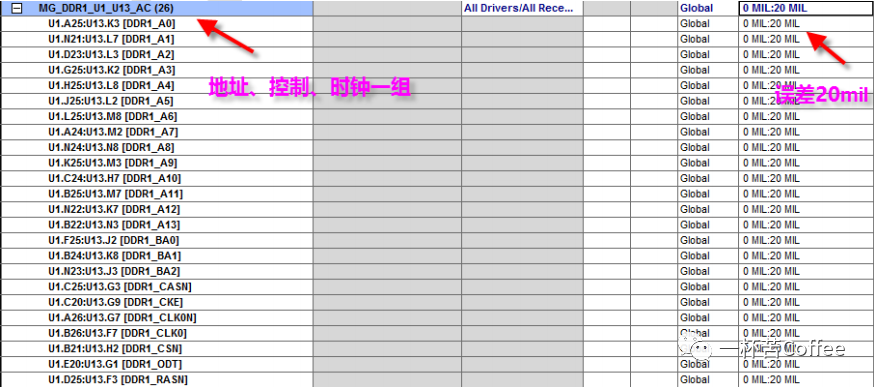

等长要求

数据线走线尽可能短,走线总长度不能超过2000mil(50.8mm),分组等长,组内等长误差需要控制在±5%。(DQS和时钟线没有等长误差要求,部分芯片有组件以及DQS和时钟线的等长要求,具体需要参考手册)

地址线、控制线、时钟线作为一组等长,组内误差不允许超过±20%;

DQS和时钟差分线对内误差范围控制±1%;

信号的实际长度包括PIN脚长度、PIN Delay等。

4 FPGA布线要求

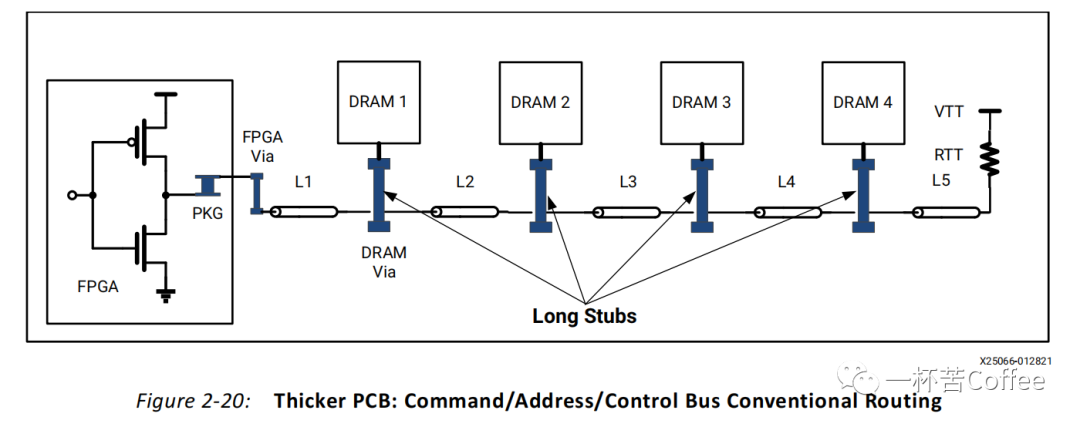

在PCB上,命令、地址和控制总线的路由见下:

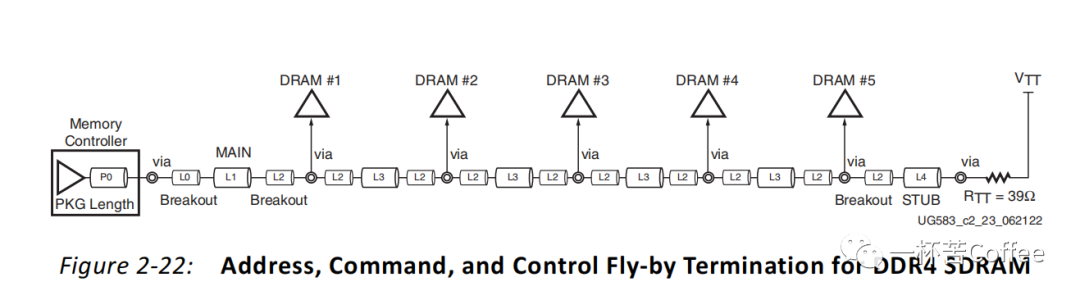

4.1 FLY-BYU拓扑结构

命令、地址和控制总线的布局布线

命令、地址和控制总线布局方式见下:

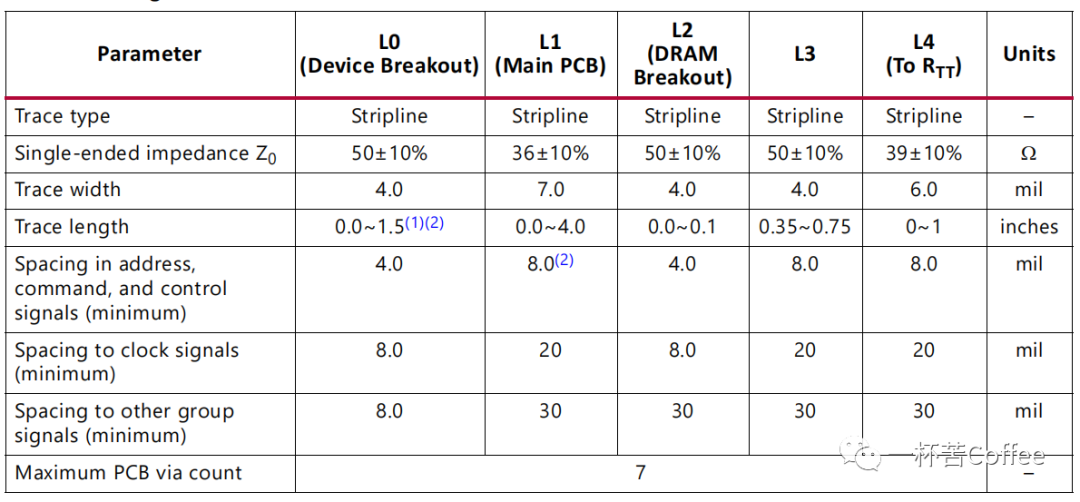

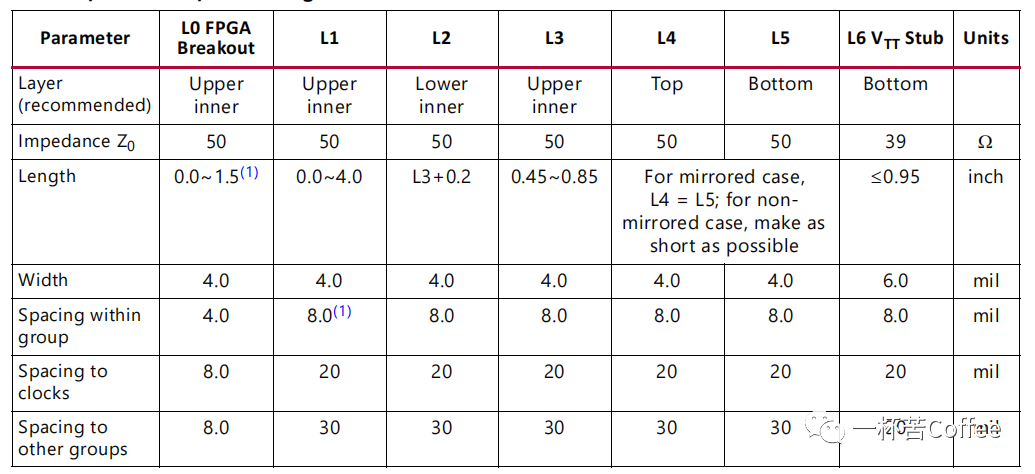

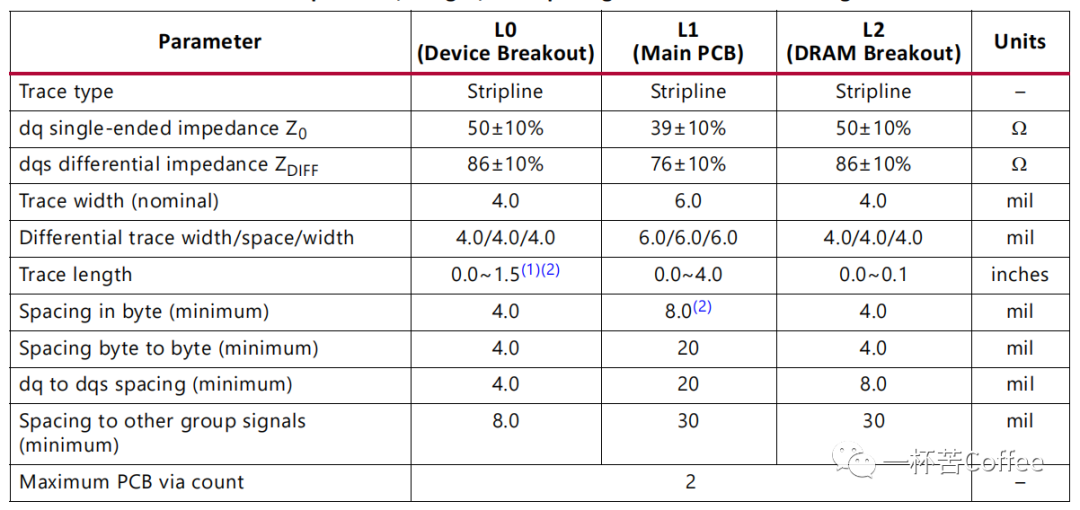

数据线的阻抗、长度以及布线指导见下表:

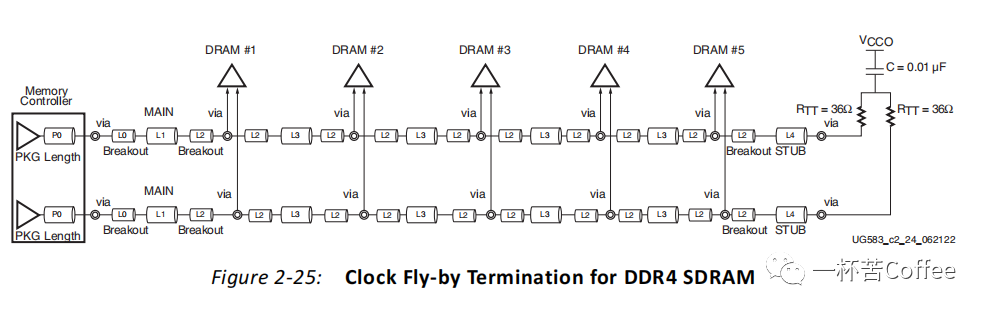

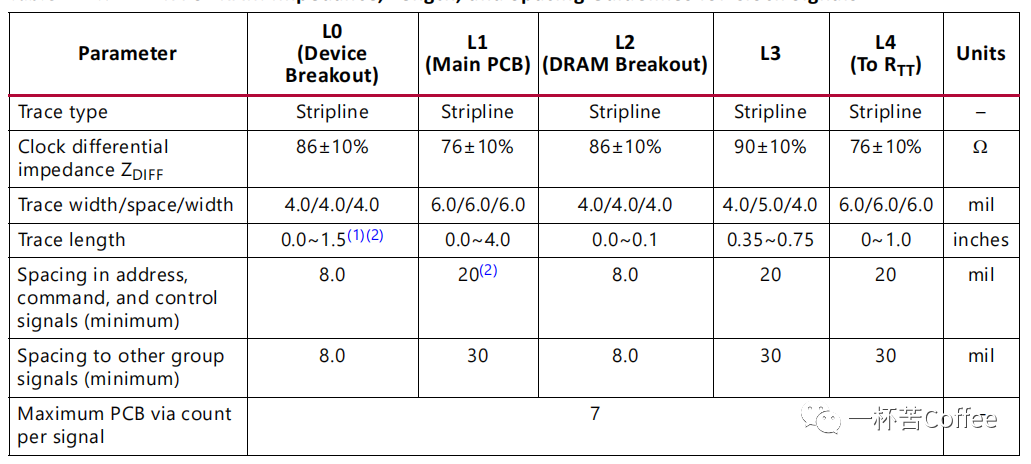

时钟线的布局布线

命令、地址和控制总线布局方式见下:

数据线的阻抗、长度以及布线指导见下表:

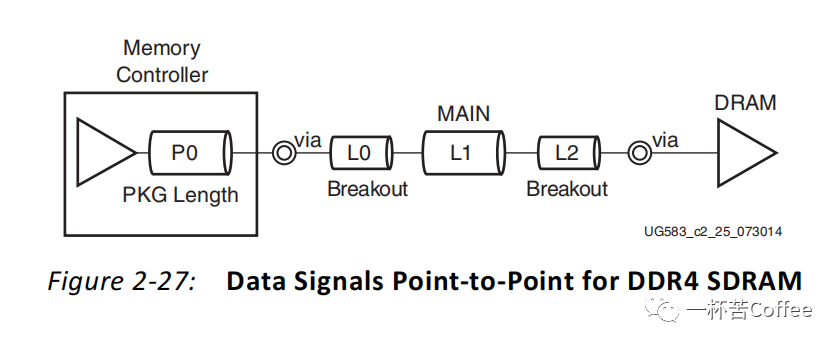

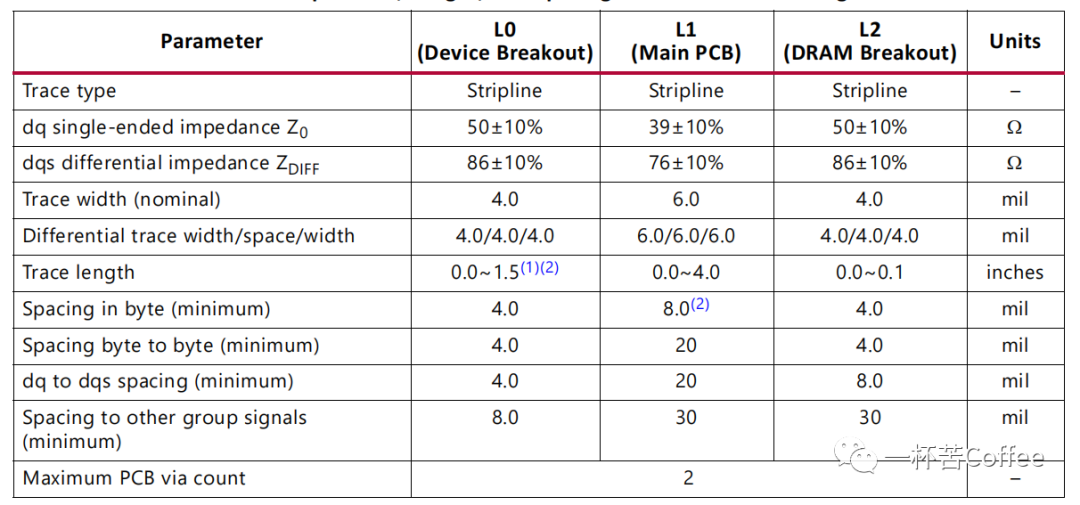

数据线

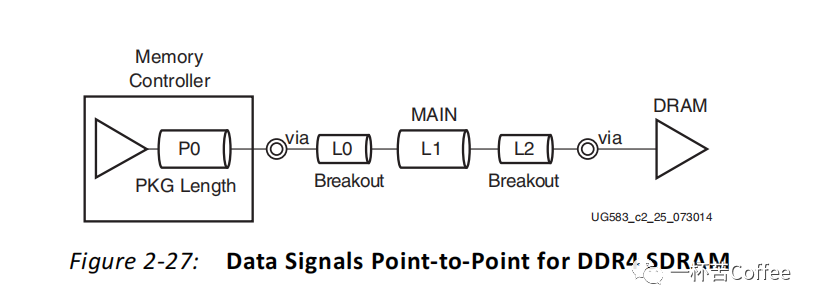

两种拓扑结构的数据线(DQ、DM、DQS)的点对点连接方式相同。

数据线的阻抗、长度以及布线指导见下表:

4.2 Clamshell拓扑结构

命令、地址和控制总线的布局布线

命令、地址和控制总线布局方式见下:

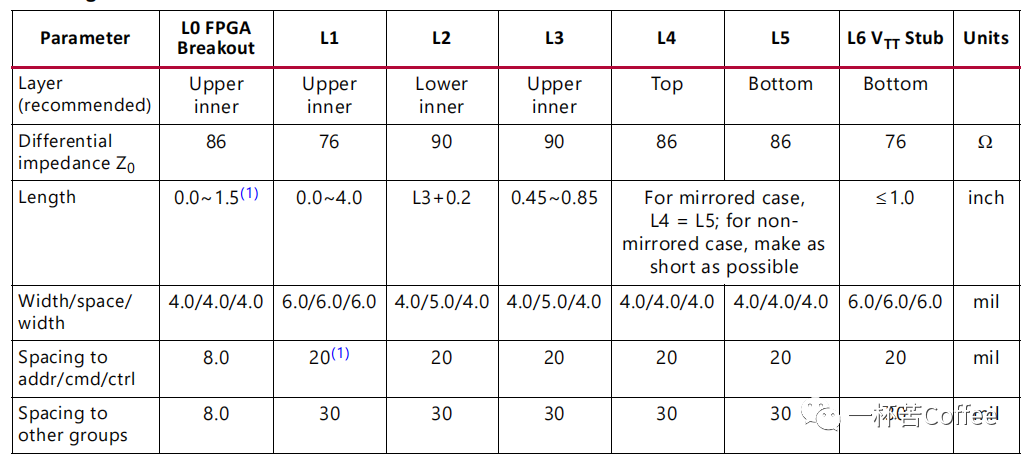

数据线的阻抗、长度以及布线指导见下表:

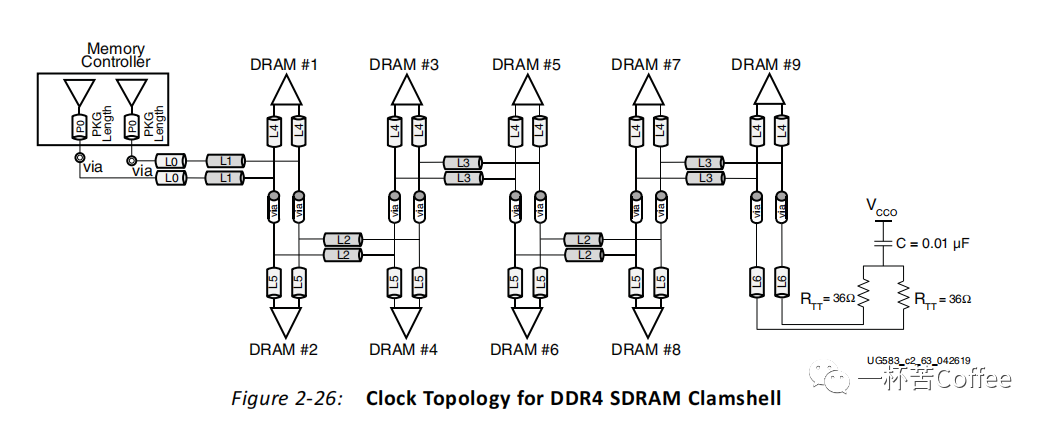

时钟线的布局布线

命令、地址和控制总线布局方式见下:

数据线的阻抗、长度以及布线指导见下表:

数据线

两种拓扑结构的数据线(DQ、DM、DQS)的点对点连接方式相同。

数据线的阻抗、长度以及布线指导见下表:

-

怎么成为硬件电路设计高手?2023-07-28 9749

-

硬件电路设计之晶体与晶振电路设计2023-11-22 4416

-

硬件电路设计之DDR电路设计(1)2023-11-24 9767

-

硬件电路设计2013-11-08 34352

-

高速电路设计2015-07-06 3716

-

硬件电路设计流程系列2017-10-17 3773

-

核心板硬件电路设计2021-02-01 3445

-

硬件电路设计的思路分享2021-11-11 2452

-

硬件电路设计与实践2015-12-08 1169

-

硬件电路设计具体详解2016-04-05 945

-

硬件电路设计流程--原理图设计2016-10-10 1719

-

FPGA的硬件电路设计教程和FPGA平台资料简介2020-07-06 2437

-

硬件电路设计之“磁珠”的应用资料下载2021-04-15 1262

-

主板电源DC-DC电路设计之电容的选择2021-11-18 1553

-

硬件电路设计的基本流程、作用和注意事项2023-06-30 3432

全部0条评论

快来发表一下你的评论吧 !