建立时间和保持时间对数字电路的影响

描述

不论数字信号的上升沿是抖还是慢,在信号跳变时,总会有一段过渡时间处于逻辑判断阈值的上限和下限之间,从而造成逻辑的不确定状态,更糟糕的是,通常的数字信号都不止一路,可能是多路信号一起传输来代表一些逻辑和功能状态,这些多路信号由于电气特性的不完全一致,以及PCB走线路径的长短不同,在到达其接收端时还会存在不同的延时,延时的不同会进一步增加逻辑状态的不确定性。

1、同步电路

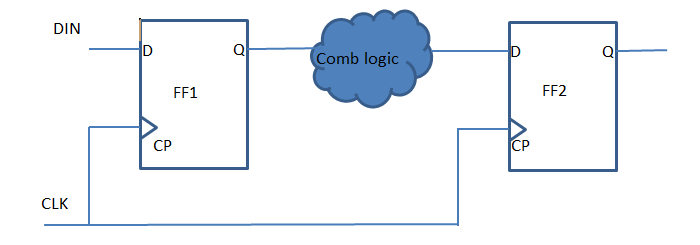

同步电路示意图

由于我们感兴趣的逻辑状态通常是信号电平平稳以后的状态,而不是跳变时刻的状态,所以现在大部分数字电路都采用同步电路,即系统中有一个统一的工作时钟对信号进行采样,虽然信号在跳变过程中可能有不确定的逻辑状态,但是如果只在时钟的上升沿对进行进行判决采样,则得到的就是稳定的逻辑状态。

采用同步时钟的电路减少了出现逻辑状态不确定的可能性,而且可以减小电路和信号布线延时的累积效应,所以在现代的数字系统和设备中广泛采用,在采用同步电路以后,数字电路以一定的时钟节拍来工作,我们把数字信号以每秒钟跳变的最大速率叫做信号的数据速率(单位通常是bps或者bit/s),大部分并行总线的数据速率和系统中时钟的工作频率一致,也有一些特殊场合采用DDR方式(Double Data rate ),即数据速率是时钟工作频率的2倍。

2、建立/保持时间

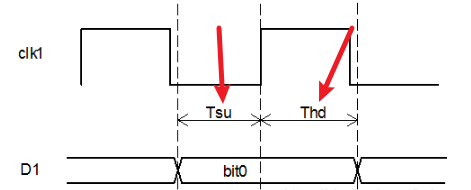

建立时间/保持时间示意图

在同步电路中,如果要得到稳定的逻辑状态,对于采样时钟和信号间的时序关系是有要求的,如果时钟信号的有效边沿正好对应数据的跳变区域附近,可能会采样到不可靠的逻辑状态,数字电路要得到稳定的逻辑状态,通常都要求在采样时钟有效边沿到来时被采信号已经提前建立一个新的逻辑状态,这个提前的时间通常被称为 建立时间(setup time) ,同样的,在采样的时钟的有效边沿到来后,被采的信号还需要保持在这个逻辑状态一定时间以保证采样数据的稳定,这个时间通常被称为保持时间(hold time)。

3、建立/保持时间对数字电路的影响

建立时间和保持时间相加起来的时间叫做建立/保持时间窗口,是接收端对于信号要保持在同一个逻辑状态的最小时间要求,数字信号的比特宽度如果窄于建立/保持时间窗口就无法同时满足建立时间/保持时间的要求,所以接收端对于建立保持时间窗口的要求实际上决定了这个电路能够工作的最高数据速率,通常工作速率高一些的芯片,很短的建立时间、保持时间就可以保证电路可靠工作,而工作速率低一些的芯片则会要求比较长的建立时间/保持时间。

建立时间和保持时间是数字电路非常重要的概念,是接收端对于可靠信号接收的最基本要求,也是数字电路可靠工作的基础,可以说,大部分数字信号的测量项目(数据速率、眼图、抖动)的测量都是为了间接保证信号满足接收端对建立时间和保持时间的要求。

-

关于建立时间和保持时间的测量方法2023-12-05 4076

-

建立/保持时间对数字电路的影响2023-10-29 1557

-

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量2023-09-04 1746

-

SOC设计中的建立时间和保持时间2023-08-23 2089

-

到底什么是建立时间/保持时间?2023-06-27 19404

-

芯片设计进阶之路—从CMOS到建立时间和保持时间2023-06-21 3025

-

静态时序之建立时间和保持时间分析2022-08-22 5787

-

关于数字IC的建立时间以及保持时间你想知道的都在这2021-09-18 2896

-

为什么触发器要满足建立时间和保持时间2021-08-09 7766

-

保持时间与建立时间2018-11-29 3978

-

什么叫建立时间,保持时间,和恢复时间2017-04-08 4366

-

建立时间和保持时间讨论2015-03-10 4887

-

数字电路中,建立时间和保持时间对于触发器的时钟信号有2012-01-27 5542

全部0条评论

快来发表一下你的评论吧 !