PCB走线为什么不能太长?线间距为什么不能太近?

电子说

描述

PCB(Printed Circuit Board)是电子设备中的重要组成部分,用于连接和支持电子元件。走线是将电子元件之间的电路连接起来的过程。在PCB设计中,过长的走线可能会导致一些问题,包括以下几点:

*信号衰减:电路中的信号在传输过程中会受到衰减,过长的走线会增加信号衰减的可能性。信号衰减可能导致信号失真、噪声增加和通信错误。尤其是对于高频信号和快速信号传输,过长的走线会更加明显地引起问题

*信号延迟:电路中的信号传播需要一定的时间,过长的走线会增加信号传播的延迟。在一些应用中,如高速通信和时序敏感的电路,信号延迟可能会导致系统性能下降或功能失效。

*串扰干扰:过长的走线会增加电路之间的串扰干扰的可能性。串扰干扰是指一个信号线上的信号对其他信号线产生的干扰。当走线过长时,信号线之间的电磁相互作用可能会导致信号的串扰,从而引入错误或干扰。

*PCB布局困难:过长的走线可能导致布局上的困难。PCB布局时需要考虑信号的路径、电源和地线的分布、元件的布置等因素。如果走线过长,可能会增加布局的复杂性,使得设计更加困难。

因此,在PCB设计中,通常需要尽量控制走线的长度,以确保信号的可靠传输和系统的性能。这可以通过合理的电路布局、信号线的路径规划、使用适当的层间连接等方法来实现。

PCB走线太长,最终综合的寄生电容会增加

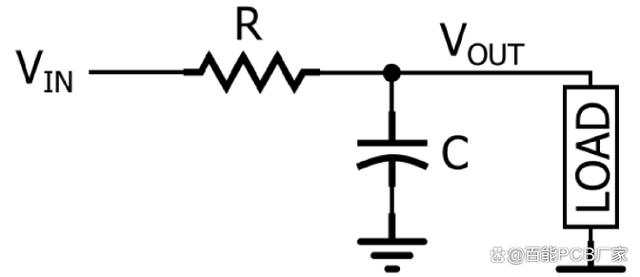

不用到微观层面去分析。我们根据电容的定义就知道:两个间距保持不变的平面,面积越大,电容值越大。所以走线越长,则会导致综合的对地容性会持续增大。电容的容值越大,则相当于低通滤波器,会衰减掉高频分量。

我们不需要到微观层面去分析,就知道走线太长,在接收端肯定影响高频分量。

当PCB走线过长时,寄生的电容会变大。这是因为走线的长度增加会增加电路元件之间的物理距离,进而导致电容的增加。以下是导致寄生电容增加的几个主要因素:

走线长度增加:走线的长度是电容值的一个关键因素。根据电容的定义,电容值与电场中的电场强度以及物体之间的距离成正比。当走线的长度增加时,物体之间的距离增加,导致电容值增加。

走线宽度和厚度:走线的宽度和厚度也会对寄生电容产生影响。通常情况下,走线宽度越大,走线之间的电场强度就越小,从而减小了电容值。而走线的厚度增加则会导致电容值增加,因为走线厚度的增加会增加走线的表面积,从而增加了电容的效果。

周围环境和临近走线:寄生电容的大小还与周围环境和临近走线的位置有关。当走线过长时,与其他走线之间的距离可能变得更近,这会导致临近走线之间的电容增加。此外,周围环境中的其他导体或地平面也会对走线之间的电容产生影响。

需要注意的是,寄生电容的增加可能会对电路的性能产生负面影响。它可以影响信号的传输速度、引入干扰和串扰等问题。因此,在PCB设计中,需要合理规划走线长度和布局,以控制寄生电容的大小,确保电路的可靠性和性能。

PCB走线太长,最终综合的寄生电感会增加

当PCB走线过长时,寄生的电感会变大。这是因为走线的长度增加会增加电路元件之间的物理距离,进而导致电感的增加。以下是导致寄生电感增加的几个主要因素:

走线长度增加:根据电感的定义,电感值与电路中的线圈(走线)长度成正比。当走线的长度增加时,线圈的长度也增加,导致电感值增加。

走线宽度和厚度:走线的宽度和厚度对寄生电感也有一定影响。较宽的走线和较厚的走线会减小走线的电感值,因为它们提供了更多的导体表面积和截面积,从而减少了线圈的长度。

走线形状和布局:走线的形状和布局也会影响寄生电感。例如,蜿蜒曲折、盘绕或环绕式的走线形状会增加走线的电感值。此外,如果走线与其他走线或导体之间存在临近或相互耦合,也会增加走线的寄生电感。

寄生电感的增加可能对电路产生负面影响。它可以导致信号传输速度减慢、引入串扰、降低电路的带宽等问题。因此,在PCB设计中,需要合理规划走线长度、宽度和布局,以控制寄生电感的大小,确保电路的可靠性和性能。

PCB走线太长,增加寄生电阻

这个按照电阻的定义就想得通,此处不做解释。

通过布局优化走线长度

在设计中,布局是一个重要的环节。布局结果的好坏将直接影响布线的效果,因此可以这样认为,合理的布局是PCB 设计成功的第一步。简单的理解,PCB布局就是把所有的元器件按照功能结构、模块化、满足DXF的要求、满足顺畅布局、布线等原则进行。

考虑整体美观,一个产品的成功与否,一是要注重内在质量,二是兼顾整体的美观,两者都较完美才能认为该产品是成功的。在一个PCB 板上,组件的布局要求要均衡,疏密有序,不能头重脚轻或一头沉。

合理的布局,才能优化整理的走线最短路径。布局不合理,就会导致不必要的走线长度。

**我们把还没连接的PCB,用细线表示连接关系的线,叫做鼠线,又叫飞线。鼠线指两点间表示连接关系的线。如你在原理图上设定的两个焊盘之间有连接关系,那么导入LAYOUT后就会在两个焊盘间生成一根鼠线以指导你布线。

**

鼠线也是帮助你初步判断会不会走得太绕线。所以,这种朴素的知识也就是人人都知道:一个器件布下去之前,转几个90°,看看怎样走线最短。

例如一些大型的处理器的电源管脚的分布,是考虑到你的走线的。所以你在设计电源模块的摆放的时候,也要考虑各个大电流电源供电走线不要交叉。所以一开始就要规划好,电源怎么供电、时钟怎么布放、接口怎么出,其实除了为了布局阶段“布进去”,还为了布线阶段“走得顺”。

既然PCB走线要走得短减少寄生参数,为什么会有“蛇形走线”

蛇形走线最主要是为了保证电路时序约束的正确。数字电路中高低电平相互翻转的时候是需要时间的,为了保证在接受端电平能被正确的采样,通常会预留一点时间给信号电平建立起来,同样,正确的采样也需要一点时间,就需要信号翻转到某个电平后保持一段时间。

这就是所谓的建立时间(setup time)和保持时间(hold time)。

建立时间、保持时间模型展现;建立时间余量、保持时间余量的计算;以及系统允许时钟频率的最大频率计算。

建立时间(Tsu):在时钟采样沿之前,数据必须保持稳定的时间,该时间量称为建立时间。

保持时间(Th):在时钟采样沿之后,数据必须保持稳定的最短时间。

理想最优的建立时间和保持时间出现在数据中间采样的位置,如下所示,实质就是使触发器在采样沿得到稳定的数据,如果数据在时钟上升沿的建立保持时间内{latch edge-setup,latch edge+hold time}发生跳变,则会产生亚稳态输出,即输出值在短时间内处于不确定态,有可能是1,有可能是0,也可能什么都不是,处于中间态。

在现在的高速数字设计中,其实串行总线的接口已经大行其道了。在我们刚工作的阶段,其实还是大量的并行总线在大量使用:包括DDR、PCI、LPC、LocalBus,这些并行的接口需要时钟去采样数据,基本原理就是大家数字电路去学习的“D触发器”。

所以,现在还在用"蛇形走线"绕等长来满足建立保持时间的设计主要应用于DDR相关的设计。大量的并行接口已经被PCIe、USB、SATA……这样的串行总线代替了。所以在高速数字设计上,大家非常关注“眼图”。

-

pcb线宽和线间距的设置原则2024-08-15 11299

-

pcb布线间距与电压的关系2023-12-20 18338

-

为什么在PCB layout时不能走直角线2023-11-20 3656

-

为什么PCB走线中不能出现锐角和直角呢?2023-04-11 2090

-

PCB为什么不能直角走线?三大理由!2023-01-06 6880

-

PCB为什么不能直角走线?2022-09-28 5938

-

【必看知识】PCB为什么不能直角走线?2022-08-15 2385

-

pcb layout能不能以90°走线?2021-02-26 2634

-

请问PCB走线线间距能走5mil吗?2019-09-26 8658

-

请问多根走线时怎么调节线间距?2019-04-01 5671

-

PCB走线之安全间距到底是多少2016-06-17 5542

-

信号在PCB走线中传输时延(下)2014-10-21 2995

-

打板时关于走线间距的工艺要求2012-11-08 5032

全部0条评论

快来发表一下你的评论吧 !