ADC中采样开关引起的误差的两种因素分析

模拟技术

描述

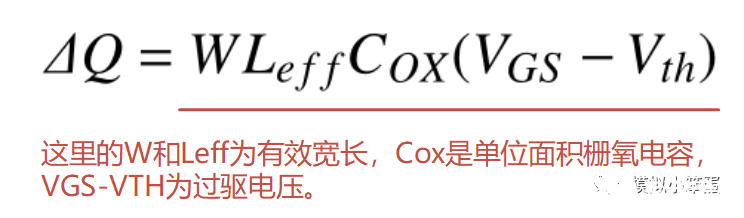

在ADC中,采样开关引起的误差主要由两个因素导致,分别是电荷注入和导通电阻非线性。前者主要由MOS管导通时导电沟道电荷的产生和消失引起。当一个MOS管工作在三极管区时,沟道电荷的大小为:

当开关关断的时候,沟道电荷需要消失,电荷只能流入到MOS管本身的S端或D端,对两端的电压造成影响。因此流入采样电容上的电荷会产生一个offset,offset的大小取决于多个因素,如:工艺、晶体管尺寸、输入电压和开关时序等。最重要的是offset和输入相关,这会在采样时导致产生谐波。

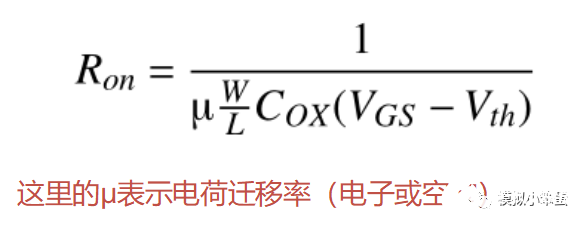

导通电阻非线性主要由开关导通电阻与输入信号的相关性引起。下图为导通电阻的大小:

可以看到,无论哪种因素,当VS=VIN时,过驱动电压VGS都是输入电压的函数。

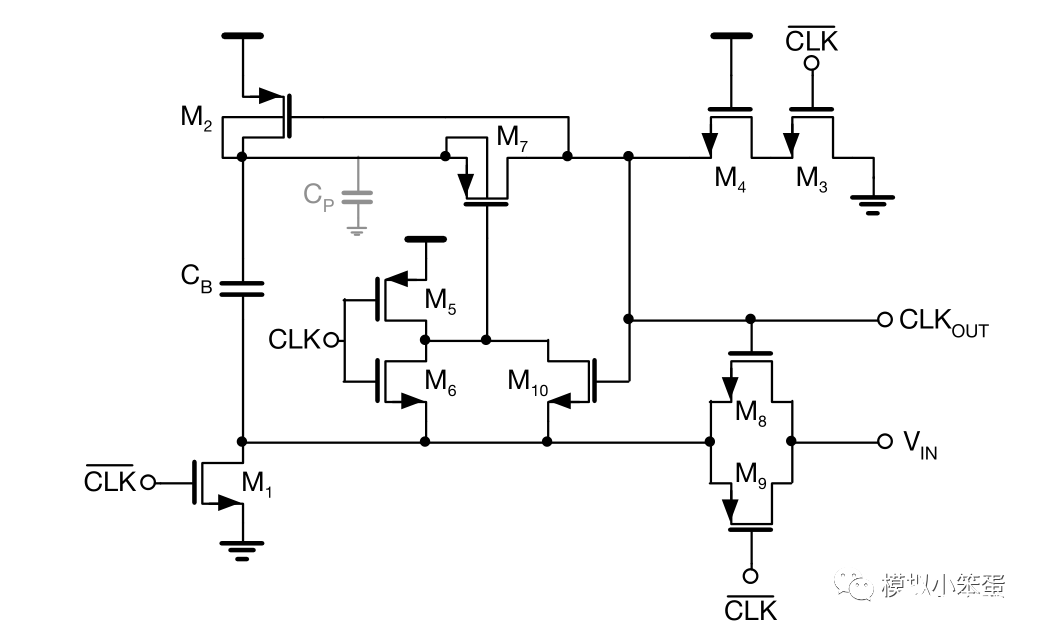

下图所示为栅压自举电路,该电路理论上可以摆脱VGS对输入信号的依赖,使VGS成为一个恒定值,提升导通电阻线性度,降低谐波。

图1 栅压自举电路

在CLK=0时,电容器CB被M1和M2预充电到V DD。M3和M4紧接地输出时钟CLK OUT,关闭M8和M10,而M5关闭M7。

当CLK=1时,M6打开M7, M7打开M8,M8和M9在CB的底板处分别得到VIN。这使得CB的上板变成V DD + VIN并由M7向CLK OUT提供这个值。实际上,这个值会被寄生电容C P衰减。该寄生电容主要是M2和M7的体寄生电容和版图的走线寄生构成。因此,在自举电路的有效性和电路可达到的最大采样速度之间存有一个折中关系。

M4 的作用是在CLK=1阶段降低了对M3施加的VDS和VGS,确保不会有超压风险。M4和M3一般需要足够大,使之不会在采样时钟的下降沿引入过多的抖动噪声。而M10确保整个采样阶段M7的持续导通。

注意:图1中的M9并不是必须的。它是一个虚拟开关,以平衡在CLKOUT看到的负载,并确保对称性(和后级电路相关)。

审核编辑:黄飞

-

两种LED开关电源控制方式入门科普2016-01-29 3217

-

ADC误差的产生以及如何提高ADC的精度2021-07-09 11976

-

单片机adc采样原理2021-07-14 1083

-

CH573 ADC采样误差大怎么解决?2022-08-24 1000

-

高速、高精度频率采样中的量化误差分析2008-12-13 866

-

ADC中的ABC理解ADC误差对系统性能的影响2009-04-16 1397

-

超声波液位计的误差分析与校正2011-12-15 1635

-

水下GPS定位误差分析2013-07-24 946

-

采样法交流电参量测量的误差分析2015-12-31 1060

-

ADC转换误差率的测试分析2017-11-15 9239

-

改善实际ADC应用中的量化噪声性能的两种方法分析2020-08-24 6558

-

ADC中的增益误差和失调误差的分析2021-04-01 2186

-

中频采样和IQ采样的比较分析2022-07-28 5482

-

数字电源ADC采样时间的原理分析2023-03-08 6282

-

ADC中可能贡献误差率的基本因素2023-11-28 470

全部0条评论

快来发表一下你的评论吧 !