应用指南 | 使用LTSSM功能表征PCIe设备性能 (附直播回顾)

描述

点击上方“泰克科技” 关注我们!

点击上方“泰克科技” 关注我们!

二十年前,PCI-SIG组织首次定义了PCIe标准。PCIe的引入旨在实现CPU与外围组件之间的高速串行通信。自2003年以来,为适应现代计算机的带宽需求,PCIe标准几经迭代。PCIe最初作为一种串行接口引入,用于替代众多主板架构使用的并行总线,但PCIe拥有一项独特特性:通道数量可从1个扩展至32个。借助这一并行总线特性,PCIe兼容设备之间可以根据数据传输要求,建立宽度为1个、2个、4个、8个、16个甚至高达32个通道的链路。

随着数据传输速率的不断增加,物理层协议的复杂性也与日俱增,以确保在符合PCIe规范基本原则的同时(包括通道宽度灵活性和向下兼容“传统”设备,即使用早期版本PCIe开发的设备),实现高效的数据传输。例如,使用PCIe Gen4 规范开发的设备必须向下兼容早期版本PCIe(如Gen1和Gen2)开发的设备。

先来回顾一下今年的泰克云上大讲堂—PCIe测试面面观

本期应用指南则说明讲述了如何使用泰克TMT4 PCIe性能综合测试仪提供的高级链路训练状态机(LTSSM)监视信息。借助这一高级功能,结合硬件触发输入/触发输出功能,用户可以根据PCIe状态机的描述,识别物理层与数据链路层交互中的异常。

LTSSM监视器可就TMT4 PCIe性能综合测试仪在与被测设备(DUT)交互过程中实现的各种状态提供相关信息(无论是作为根复合体(RC)还是端点 (EP))。

实际调试流程可能包括以下一个或多个步骤:

■ A. 检验DUT能否按照PCIe规范或“允许的转换”中的序列,在可用状态间进行转换。

■ B. 如果DUT没有按照预期序列转换状态,确定DUT最后已知的正常运行状态。

■ C. “可疑”状态或转换被隔离后,用户可以选择在进入特定状态时,通过发出硬件触发输出,在示波器上捕获数据。

PCI Express架构和链路训练的必要性

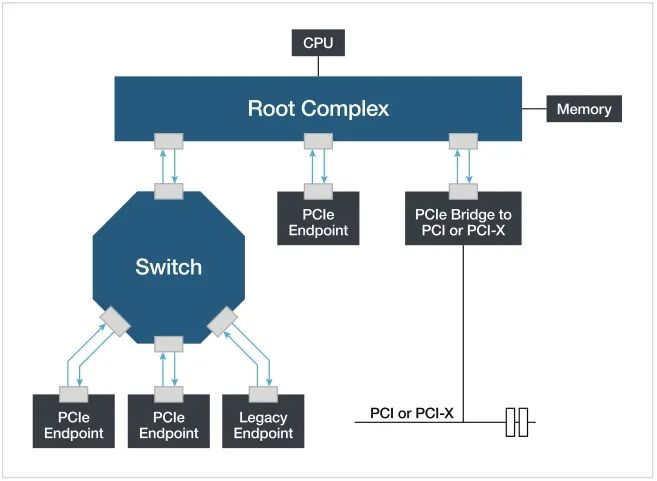

尽管PCIe为点对点协议,但数据源与目标之间的交互有着明确的层次结构。PCIe系统由大量点对点接口组成,通过一个基础架构或Fabric接口连接多个外围设备和模块。主CPU(或处理器子系统)位于顶端,通过适当的用户接口连接到一个RC。此RC是顶层PCIe互连组件,通常连接主内存,CPU通过RC访问主内存。PCIe接口直接或通过一个交换器连接RC(图 1)。

图1. PCIe层次结构

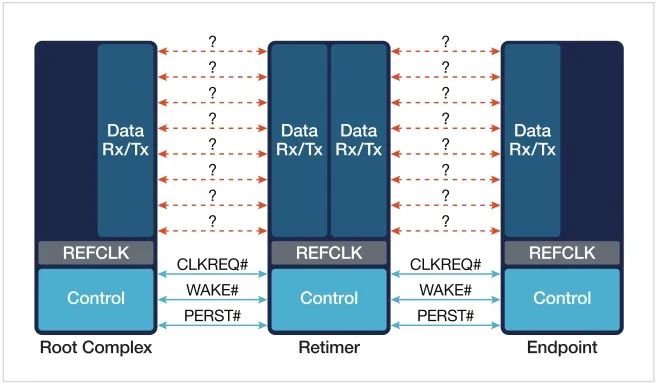

每个互连都有一个下行链路(来自上游组件,如 RC)和一个上行链路(来自下游组件,如上行链路(来自下游组件,如EP)。最典型的RC设备包括 PC 主板或嵌入式系统控制板。对于EP,显卡或网络接口卡等设备可通过交换器连接RC,这有助于扩展规范内的可寻址设备数量。EP设备也可直接与RC通信,如图1所示。通常,这种通信并非100%的直接通信,而是在RC与EP设备之间插入一个信号调节设备(一个重定时器,或一个重驱动,图2),以确保信号质量,补偿高速传输下的信号质量损失。

PCIe规范建立了链路训练过程,用于确定给定通道是否适用于接口支持的各种数据速度传输,有多少这样的通道可用,以及物理层的各种其他因素,从而确定特定PCIe设备是否有可以配对的链路伙伴。

图2. 重定时设备的PCIe物理层连接

PCIe中如何建立和监控链路?

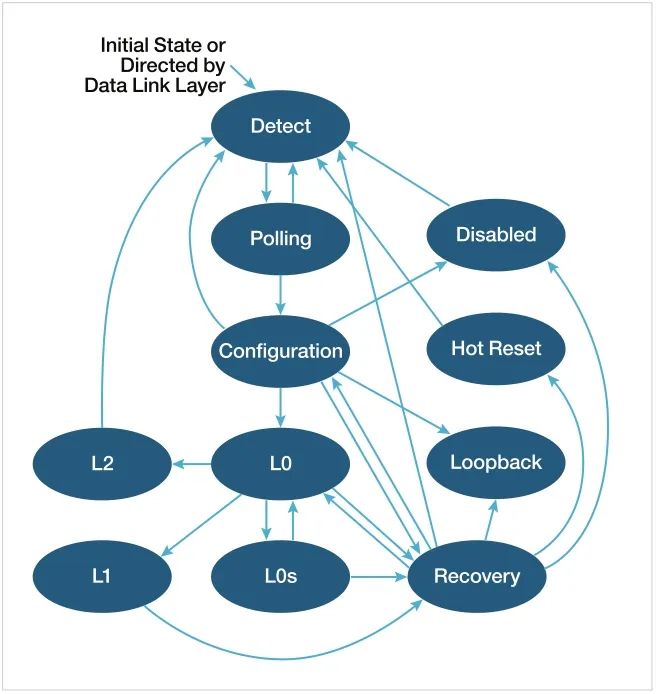

当对所有设备(至少一个RC和一个或多个EP)供电并提供参考时钟,PCIe设备就会开始链路训练。整个链路训练过程包括接收器检测、轮询、配置和恢复。这一过程中,可以通过观察“LTSSM状态”确定链路状态。如PCIe规范所述,共有十一个顶层状态,每个状态进一步细化,包含多个子状态。

图3. 链路训练状态机

总结

• PCIe链路状态由链路训练和状态机(LTSSM)定义。从初始状态开始,状态机经历一系列主状态(检测、轮询、配置、恢复),训练和配置链路,直到完全进入链接状态(L0)。

• 其他状态还包括电源管理状态“Lx”,一种用于测试和调试的“回环”模式,或“热重置”状态,用于使链路返回初始状态。禁用状态是针对经配置暂停通信的链路。

• 初始状态通常由数据链路层确定,但一般来说,PCIe链路的默认初始状态为“检测”。

泰克TMT4 PCIe性能综合测试仪用户界面可显示状态机示意图,如上图所示,当选择发起LTSSM监控测试时,可以看到它进入各种状态的实时进度。

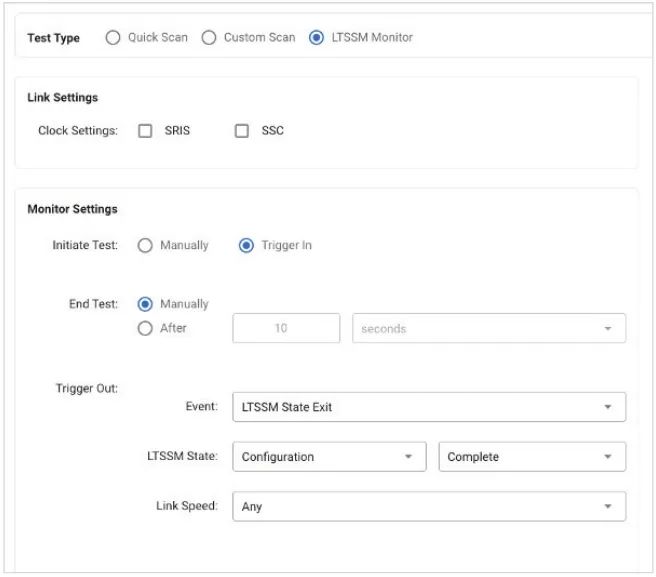

图4. LTSSM测试配置

LTSSM监控可以手动发起,或在发出有效的硬件触发输入信号时发起。此外,当发生与LTSSM状态相关的选定事件时,可以生成触发输出信号(图4)。测试完成后,测试结果存档(*.zip)中将包含观察到的 LTSSM 状态日志。

泰克工程师小助手

扫码添加小助手,订阅更多相关技术内容及下载本期直播讲义!

TMT4作为链路伙伴

TMT4 PCIe性能综合测试仪是一款符合PCIe规范的灵活仪器,既可作为RC设备,也可配置为支持PCIe Gen3和Gen4速度的EP设备。与DUT建立连接的关键在于选择正确的适配器配置。

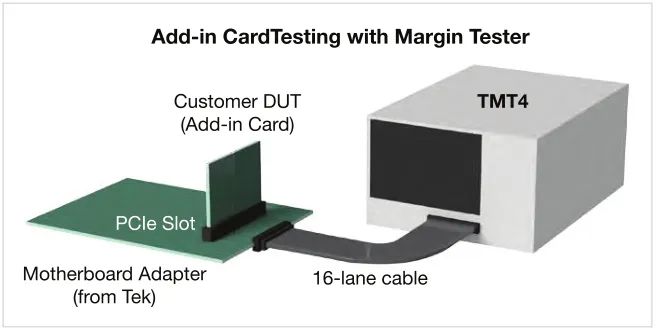

例如,当扩展卡(AIC)是DUT时,TMT4 PCIe性能综合测试仪为RC设备(图5)。

图5. TMT4作为RC设备

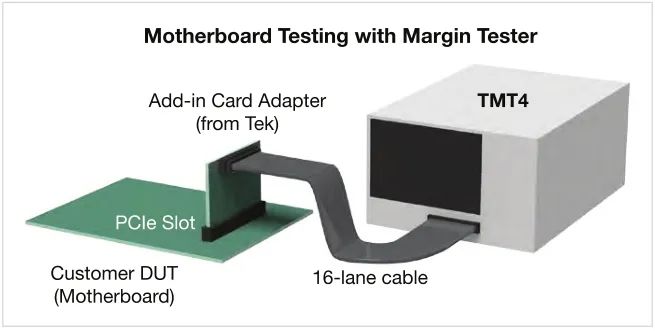

而当对典型的RC设备进行评估时(如计算机主板),TMT4将作为EP设备与DUT进行交互(图6)。

图6. TMT4作为EP设备

深入了解链路训练过程

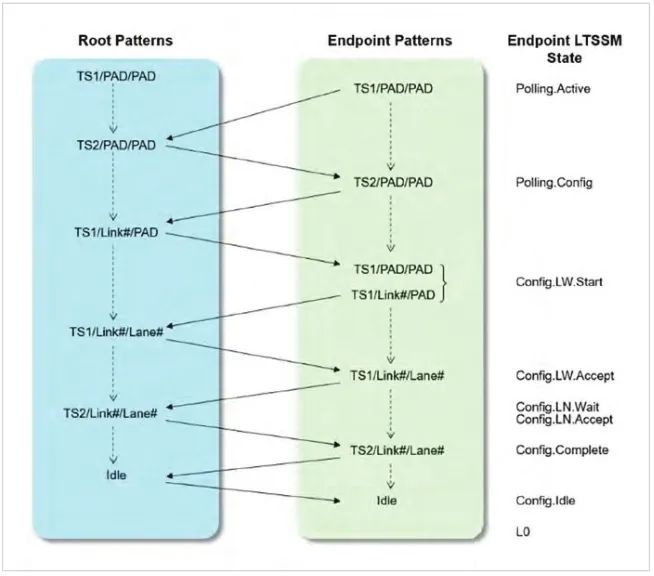

当PCIe设备开启链路训练过程时,链路两端之间会进行双向数据交换。随着测试数据和模式(TS=训练集)从链接的一端发送到另一端,接收端会响应发送端,并在从一个状态进入下一个状态时切换发送和接收数据的角色(图7)。

图7. RC与EP之间的链路训练序列

执行LTSSM监控测试时,日志始终会从TMT4 PCIe性能综合测试仪的视角记录达成的状态。

使用TMT4监控链路训练状态机

在链路训练过程中,DUT与TMT4之间的交互包括生成各种测试模式,使DUT从初始的检测状态,经过轮询和配置状态,最终达成L0状态,这表明RC设备与EP可以成功通信。

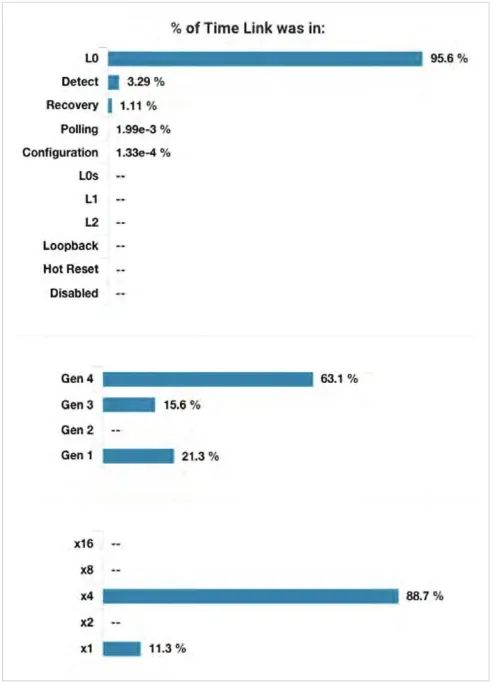

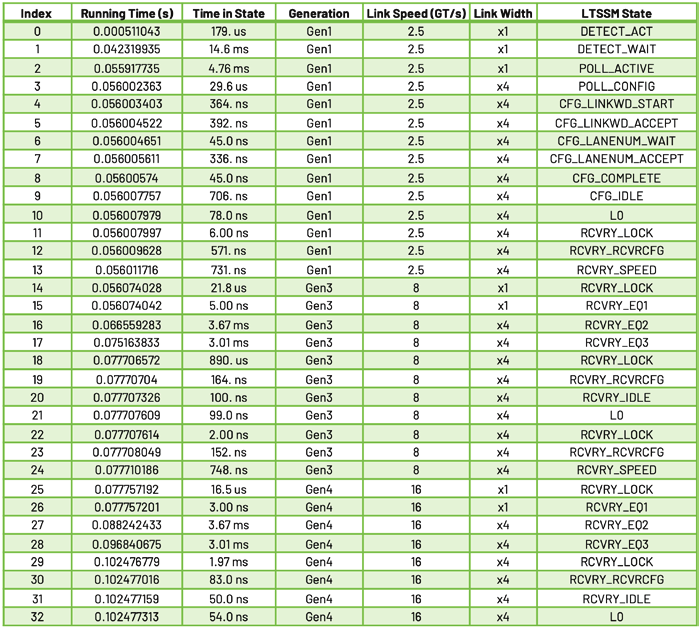

• 对于正常/有效链路(如下方LTSSM测试结果中所示),TMT4是作为RC设备运行。正常运行条件下,链路训练过程中的DUT和链路伙伴都处于L0状态,只有在链路配置的任何重要物理层属性发生变更时才会转换到其他状态,如通道宽度,链路速度或通道反转等。

当显示.csv格式的LTSSM日志数据文件时,用户可依据DUT的有关信息确定LTSSM状态的序列,判断是否严重偏离预期流程。

在这个示例日志中,有三个实例的DUT达成L0状态(如在TMT4上所见):

• 第一个,达到基本的PCIe Gen1速度和“四通道”(×4)宽度,从检测状态转换为轮询状态,最后进入配置状态。

• 第二个,从PCIe Gen1(2.5Gt/s)转换为PCIe Gen3(8GT/s),首先进入恢复状态,然后进行链路均衡。

• 第三个, 从PCIe Gen3(8Gt/s) 转 换 为PCIe Gen4(16GT/s),同样是首先进入恢复状态,然后进行链路均衡。

从以上三个实例来看,所有连接的PCIe设备都经历了初始链路训练过程,以建立基本功能(第一步),然后进行额外的链路均衡,以在设备之间建立稳定可靠的连接(第二和第三步)。当PCIe链路中的所有设备都支持PCIe Gen 3或更高的数据速率时,就会进行链路均衡。由于高于Gen 3的每一代PCIe连接都需要优化(链接),链路均衡可能发生多次,从最小通道宽度(×1)开始,如果成功,逐步扩展到最大可用通道数。

当然,也可能有其他情况,例如观察到一个或多个状态转换并不能表明DUT正常运行。

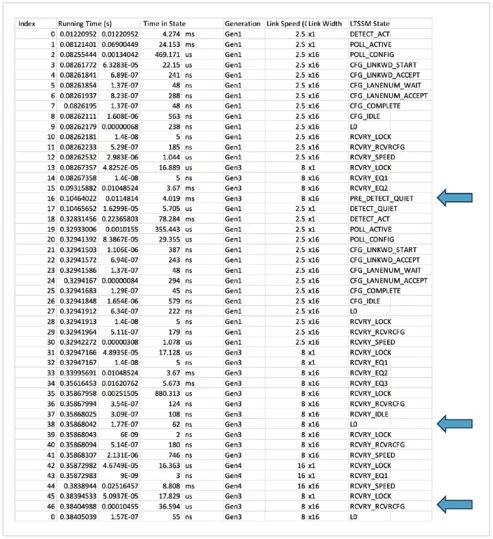

例如,以下日志源于一块无法达到16通道Gen4数据传输速率的主板DUT,因此发起了一个下行链路过程,最终在Gen3 (8Gt/s) 的速度下稳定在16通道。

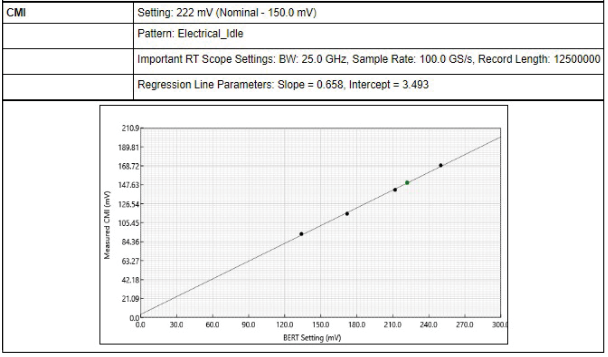

DMI是在已知损耗的通道上测量的,该通道代表物理通道。ISI/DMI/SJ共同用于以确定性方式设置EH和EW。

在第一个蓝色箭头处,DUT退出均衡过程,直接返回“预检测静默”配置(可能是受数据链路层指示,并非预期的PCIe行为)。

• 在第二个蓝色箭头处,DUT使用正常的链路均衡过程,使所有16个通道都达到Gen3速度,在达成L0状态前进入恢复空闲状态。

• 然而,在第三个蓝色箭头处,DUT似乎无法在一个或多个通道上继续均衡过程,并直接从恢复接收器配置跳到L0状态,表明可能与Rx设置不匹配(并未受数据链路层指示返回检测状态)。

为了更好地理解Tx与Rx设置之间的交互,这种情况下LTSSM监视器可以就异常行为提供可能的原因分析。其他LTSSM功能还包括使用硬件触发信号开始和停止实时示波器的模拟数据收集。

|结论|

泰克TMT4 PCIe性能综合测试仪作为稳定可靠的链路伙伴,可观察链路训练和均衡过程中的LTSSM状态,并支持使用硬件触发信号获取波形,提供关于链路状态的准确信息,从而解决可能的链路不一致问题。

点击阅读原文,了解更多!

欲知更多产品和应用详情,您还可以通过如下方式联系我们:

邮箱:china.mktg@tektronix.com

网址:tek.com.cn

电话:400-820-5835(周一至周五900)

将您的灵感变为现实

我们提供专业的测量洞见信息,旨在帮助您提高绩效以及将各种可能性转化为现实。

泰克设计和制造能够帮助您测试和测量各种解决方案,从而突破复杂性的层层壁垒,加快您的全局创新步伐。我们携手共进,一定能够帮助各级工程师更方便、更快速、更准确地创造和实现技术进步。

扫码添加“泰克工程师小助手”

立享1对1专属服务!

点击“阅读原文”了解更多!

原文标题:应用指南 | 使用LTSSM功能表征PCIe设备性能 (附直播回顾)

文章出处:【微信公众号:泰克科技】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- 泰克科技

-

nvme IP开发之PCIe上2025-05-17 6147

-

PCIe AMBA集成指南2023-08-17 1252

-

如何使用TMT4 PCIe性能综合测试仪创建PCIe参考模板?(附白皮书下载)2023-08-09 1155

-

直播回顾 | STM32 Innovation Live2023-03-24 1618

-

虹科直播精彩回顾 | 太赫兹TDS技术的工业测厚与表征应用2022-11-23 2481

-

【桃子同学笔记4】PCIE训练状态机(LTSSM)基础2022-09-05 21615

-

【直播回顾】OpenHarmony知识赋能六期第五课—WiFi子系统2022-08-12 3560

-

【中奖公示】8.11瑞芯微RKNN系列直播二:RKNN模型精度优化指南2022-08-11 3173

-

【直播回顾】战码先锋首期8节直播完美落幕,下期敬请期待!2022-07-01 1857

-

【直播回顾】Hello HarmonyOS系列应用篇完美收官!2022-06-16 6954

-

14565B设备表征软件快速入门指南2019-10-17 1435

-

6678 pcie_phy_loopback无法training2019-01-03 3497

-

74LS系列功能表2017-01-01 5883

-

请教一个关于Xilinx pcie的问题2015-01-29 4690

全部0条评论

快来发表一下你的评论吧 !