1.5位结构MDAC的电路结构分析

描述

也是一个平常的工作日,和同事就PipelinedADC中的MDAC电路拉了几句家常。他说:“你看,这个1.5bit结构的MDAC电路,一堆的开关加电容,看起来似乎很复杂,但如果推导出它的传递函数,会发现只是一条简单的数学公式,其传输曲线也很简洁明了。所以,很多电路本质上还是数学,只不过是用电路的形式实现而已。”

我觉得,这算是一个老工程人的中肯的见解,很是让人信服(心里默默点个赞)。

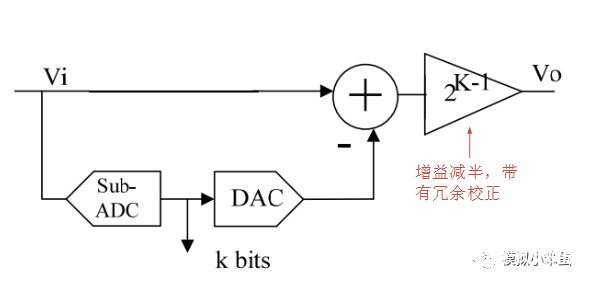

图1:MDAC原理框图

MDAC 电路一般由开关电容电路来实现,和 S/H 类似,它在两相非交叠时钟 控制下工作,工作阶段分为两个阶段:采样阶段和放大阶段。

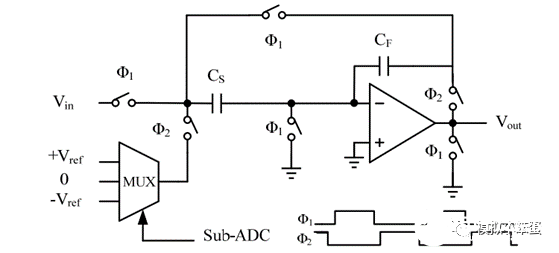

图2给出了 1.5 位结构 MDAC的电路结构示意图,其中电容 CS和 CF容值相同。时钟 Φ1 和Φ2为两相非交叠时钟。

图2:1.5bitMDAC电路结构

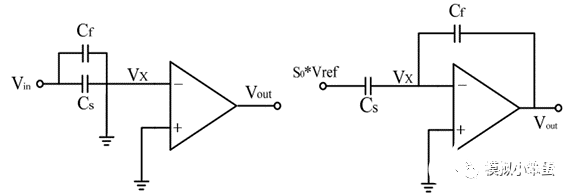

图3:1.5 位MDAC 工作原理 (a)采样阶段 (b)放大阶段

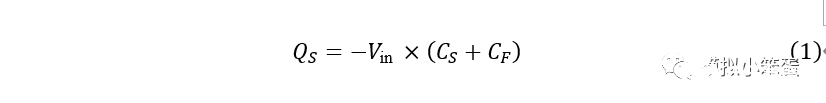

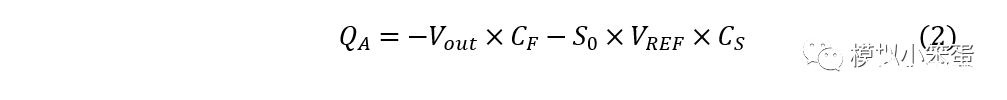

MDAC 电路工作过程如下:假定时钟为高的时候有效。在采样相,连接关系如图3(a)。两个电容对输入信号 Vin进行采样,运放此时处于复位状态。采样结束时刻,Vx节点存储的总电荷量为:

在放大阶段, 电路处于闭环状态, 连接关系如图3b所示。CS电容的一端接S0*Vref , 它的值可以为Vref、0、-Vref , 由本级sub-ADC输出决定, 在放大相, 节点上的总电荷为:

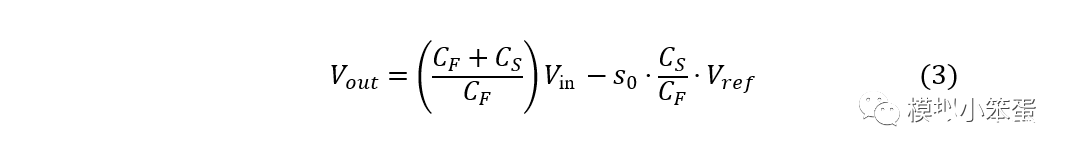

根据电荷守恒,可得出MDAC的最终输出为:

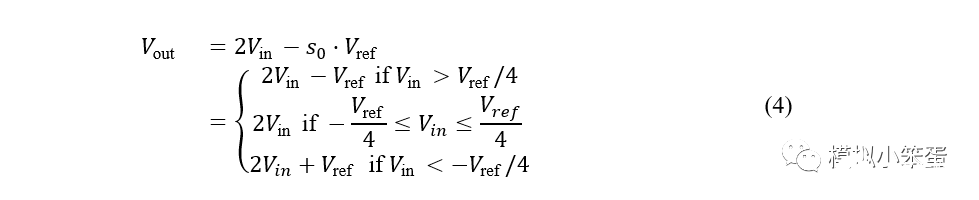

因为CS=CF,S0根据Sub-ADC结果不同可为+1、0、-1。因此上式可以写成如下分段形式:

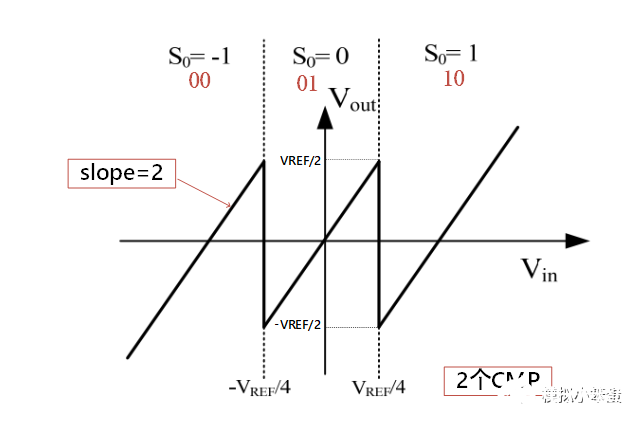

MDAC 的输出也称为余量电压。式(3)所示的余量会被传输到下一级流水线级进行继续量化,直到最后一级的 Flash 级,完成所有的量化,输出 N 位数字码。从式(4)可以得到 1.5位流水线级的传输曲线,如图4所示。其中±VREF/4是 sub-ADC 中比较器阵列的参考电平,S0为-1、0、1分别对应着数字输出00、01、10。有效位数为 1位,另外一位为冗余位,和后级流水线级的数字输出码进行错位相加,消除比较器的失调带来的误差。因此这样的结构,被称为1.5 位流水线级结构。

图4: 1.5 位MDAC 传输曲线

审核编辑:黄飞

-

位结构解析2011-03-26 3324

-

电阻器梯形结构:R-2R DAC与MDAC架构2018-09-17 6717

-

请问什么是电机结构分析的大局观?2018-10-31 1276

-

硬件的引脚和电路结构分析一下要如何启动2022-02-28 803

-

U盘的结构,U盘的电路结构2009-04-25 4592

-

NCP1562的有源钳位正激拓补结构及电路2010-01-04 4376

-

监护仪原理、电路结构及其应用分析2012-04-24 17710

-

NAND_Flash结构与驱动分析2016-03-17 879

-

什么是电路拓扑结构_多种pfc电路的拓扑结构介绍2018-01-23 55131

-

什么是数据结构?为什么要学习数据结构?数据结构的应用实例分析2018-09-26 1477

-

AD7837/AD7847:LC<sup>2</sup>完整MOS,双12位MDAC产品手册2021-04-24 837

-

天线结构分析、优化与测量2021-06-08 1112

-

差动放大器电路结构及静态工作点分析2022-10-24 2641

-

怎么分析Cross Couple的结构?2023-09-17 3941

-

ADC架构的无采样保持(SHA-less)结构分析2023-12-14 2093

全部0条评论

快来发表一下你的评论吧 !