极低抖动频率综合器的多速率时间戳建模

描述

继实现振荡器闪烁相噪理论统一后,我们再次实现频率综合器的相噪理论一统。

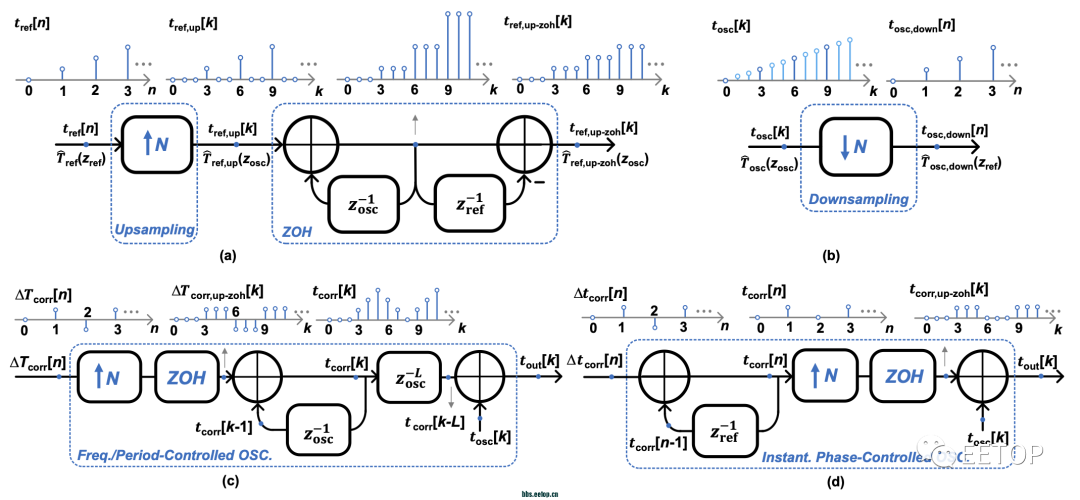

引入全新的 “双z变量多速率时间戳建模”,将几乎全部频率锁定技术(特别是极低抖动,高带宽),如:亚/采样模拟PLL,全数字PLL,注入锁定/电荷分享锁定,纳入到统一的理论框架,为设计6G通信所需的sub-50fs抖动频综,提供系统的理论指导。

我们认为,基于ADC的ADPLL和电荷分享锁定技术,将是极低抖动的先进CMOS工艺频综的重要发展趋势。

(特别地,基于新模型,我们厘清了经典架构 “亚采样锁相环” 中长期存在的关于 “电荷泵噪声不被放大N^2倍” 的理论迷思(myth)。)

1.双z变量多速率时间戳建模基础

2.极低抖动,高带宽APLL建模

3.电荷分享锁定,注入锁定建模

4.计算结果和时域仿真结果验证

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

时间频率标准源有什么功能西安同步电子科技有限公司 2025-11-04

-

时间同步获取时间戳2014-03-20 9355

-

怎么从时间戳恢复时钟频率2019-04-29 3025

-

时间抖动的概念及其分析方法介绍2019-06-04 2735

-

请问UCOSIII的时间戳计数器是哪个?2019-10-29 2813

-

带有接口的时间戳PCF212xAT2020-03-20 1396

-

时间戳PCF2127AT TCXO的应用2020-03-24 1621

-

时间戳有效PCF2127AT TCXO的应用程序2020-03-26 1831

-

时间戳的简介与实现2022-02-28 1125

-

基于椭圆曲线盲签名的安全数字时间戳方案2009-04-18 1029

-

UNIX时间戳和北京时间的相互转换2021-11-21 1340

-

uCOS-III(2) 时间戳2022-01-14 705

-

介绍一款极低电压低抖动低功耗频率综合器芯片2023-03-20 2493

-

Java中时间戳的使用2024-11-06 1009

-

相位噪声与时间抖动有何关系?如何测试时间抖动?2024-01-31 2186

全部0条评论

快来发表一下你的评论吧 !