芯片功耗组成—internal power与总功耗的理解

电子说

描述

芯片的功耗主要分为静态功耗和动态功耗

一、静态功耗

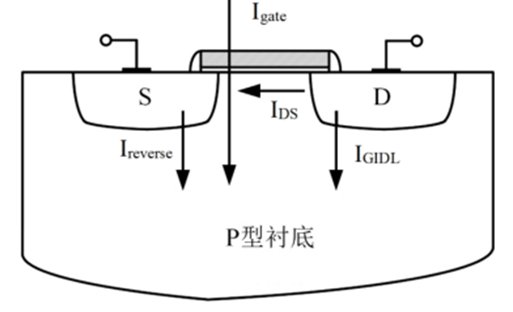

静态功耗(漏电功耗)是指芯片待机状态下所产生的的功率消耗,来源于MOS管内部的泄漏电流;泄漏电流有多个组成部分:

• (1)亚阈值泄漏电流,IDS

• (2)栅氧化层隧穿电流,Igate

• (3)反偏二极管电流,Ireverse

• (4)漏极泄漏电流,IGIDL

因此总的漏电流:

Ileakage = IDS + Igate +Ireverse + IGIDL

Pleakage = Ileakage * VDD

二、动态功耗

动态功耗指的是由于MOS管状态跳变所产生的的功耗;动态功耗又分为开关功耗和短路功耗;

1.开关功耗

开关功耗是由于逻辑门翻转时对电容充放电所产生的的功耗;

以一个反相器为例,当输入信号从高电平变为低电平,电源VDD通过PMOS对输出电容(C L )充电;

输出电容包括三个部分:门自身的输出节点电容C drain 、总的互联线电容C interconnect 、被驱动门的输入电容C input ;

• (1)这个过程从电源抽取的能量计算如下:iVDD和Vout是随时间变化的,在dt的时间范围内,

由于Vout达不到VDD,因此将CL充电至VDD需要无穷大的时间,充电过程的消耗的总能量为:

• (2)对于电容CL来说,在dt的时间范围内,其消耗的能量为:

在这个过程中,电容CL消耗的总能量为:

由(1)(2)可以看出,电源在一个充放电周期(放电过程中不消耗电源能量)中提供的总能量为C L *VDD ^2^ ;其中一半以热的形式在充电过程中被消耗在PMOS上,另一半储存在电容CL中;储存在电容CL中另一半在放电过程中被NMOS消耗掉;

如果反相器每秒开关favg次,则功耗为:Pavg,sw = EVDD / T = C L *VDD ^2^ *favg

其中T为周期,favg为开关频率;

1> 引入节点转换因子α T ,代表单位时钟周期内逻辑门的翻转概率,因此实际的开关频率favg低于时钟频率f CLK ,favg = α T *fCLK

考虑到电源网络的IR drop,逻辑门的电源Vi实际上要小于电源VDD 因此,功耗的公式改写为:

Pavg,sw = (α T *C L *V i )VDDfCLK

每次充电或放电一次,动态功耗P dynamic,sw :

Pdynamic,sw = 0.5 Pavg,sw = 0.5 (α T *CLV i )VDDfCLK ~= 0.5α T *f CLK *C L *VDD^2^

2.短路功耗

上面的讨论中,输入信号上升和下降时间为0,当输入信号存在slew时,存在短时间内PMOS和NMOS同时导通的过渡区,从VDD到VSS形成直流通路,从而产生的能量损耗P sc ;

如下图所示,NMOS在Vin > VTnmos后开始导通;而PMOS在电压达到VDD – VTpmos之前一直导通,在这段时间内PMOS和NMOS同时导通;

常用三角形脉冲模拟电流随时间的变化,每经过一个开关周期0 -1 -0所消耗的能量为:

Esc = Escr + E scf ,其中Esc和Escf分别为输入信号上升和下降期间的由短路电流所消耗的能量;消耗的能量就等于i(t)曲线下的面积和VDD的乘积;

因此, Escr = Escf = 0.5*VDD *I peak *tsc

总能量 Escr = VDD* I peak * tsc

一个周期内的平均功耗为Psc = E sc /T =E sc *f = VDD * I peak *t sc *f = C sc *VDD ^2^ *f

其中,Csc为过渡区等效电容;f为输入信号Vin的电平跳变频率;

3.internal power与总功耗

由上述讨论可知,

Ptoal = Pleakage + Pdynamic = Pleakage + (Pdynamic,sw + P sc )

在实际应用中将开关功耗分为器件功耗和网线负载功耗两部分:

Ptoal = Pdevice + Pnet

(1) Pnet为在网线上消耗的功率;对于电容的充放电,实际上只有半个周期会消耗功率,取节点转换因子αT为0.5,因此:

Pnet = 0.5* CL *VDD ^2^ *Tnet

其中CL为三部分组成的电容;Tnet为net的翻转率;

在net上消耗的只有动态开关功耗;

(2)其中 Pdevice = Pleakage + Pinternal

其中,Pinternal 包括动态开关功耗Pdynamic,sw的一部分和全部的P sc ;

器件的动态功耗包括短路功耗和动态开关功耗两部分;

因此,Ptoal = Pleakage + Pinternal + Pswitch

(这里用Pswitch替代P net ,switch power是更通用的说法)

Pinternal 包括动态开关功耗Pdynamic,sw的一部分和全部的Psc

上面的解释来自《数字集成电路物理设计》,个人理解这句话是没有问题的,但是此时Pnet中的CL就不是三部分组成的电容了;

见下图(liberty ug): 如果lib中output pin上没有capacitance,那么由output pin capacitance带来的影响已经被考虑到internal power中了;

因此,可以将internal power理解为发生在cell内部的功耗;

4.lib中的功耗

1.漏电功耗

下图为库中的漏电功耗,漏电功耗与单元的状态有关,即stage dependent(SD);

基于输入电源的leakage信息:

• leakage_power_unit:工具根据Leakage_power_unit属性确定单位;

• leakge_power:定义状态相关(when)的漏电功耗,如上图中的!A&!B表示当A=B=0时,leakage power的值;

• cell_leakge_power:如果某个状态在leakge_power中未定义,则使用cell_leakge_power的值;

总的漏电功耗,由每个状态下的漏电功耗乘以该状态下的总仿真时间的百分比,并求和得到每个单元的总漏电功耗;

由于leakage_power是状态相关,堆叠效应(stack effect)可以降低leakage_power。

例如将一个MOS管强制拆分成2个堆叠的MOS管,2个堆叠的MOS管有相同的输入;

2.internal power

internal power与状态有关,与路径有关,即即stage dependent path dependent(SDPD)

• (1)单输入的cell,internal power为input transiton和output load的二维表;

这里的internal power是定义在输出端的,包括两部分,rise_power和fall_power;

例如下图中定义了从A pin到Z pin的internal power;

-(2)对于多输入的组合逻辑门如nand,xor等;

这类cell在特定条件下某一个或者几个pin的输入值对输出不造成影响,在lib中定义在input pin,input pin的internal power只与该pin的input transition相关(也叫hidden power);

例如当nand的B输入为0时,不管A的输出是什么,最终输出都是0。此时尽管A对输出没有贡献,但是它仍然会消耗一部分功耗;

当B为1的时候,从A pin到Z pin的internal power同样也是二维查找表;

-(3)对于时序逻辑单元 -CK pin即使在锁存的数值没有变化的时候仍然会消耗能量;

3.internal power的建模方式

• 在PTPX ug中有如下描述,PTPX默认lib中的internal power计算公式为formula 1和formula 2;

由于switch消耗的总能量switch_energy为C L *V^2^

在这种方式中,0.5 * switch_energy算在了上升沿,0.5 * switch_energy算在了下降沿;而实际上switch_energy只发生在对上升沿电容充电过程中,此时得到的值并不代表真实的internal power值;

-另外一种计算方式如下formula 3和formula 4

关于如何判断:如果lib中internal power的fall power多为负值,那么为第一种方式;

4.internal power的单位

lib中internal power不是功率,而是消耗的能量,因此单位是焦耳而不是瓦特;

由3.中的式子可以看出,internal power的单位与CV^2^相同;

在lib中,电容C单位为Pf,电压单位为V,因此internal power的单位为Pf*V = PJ

-

芯片功耗组成—internal power与总功耗的理解2024-03-29 7595

-

PTPX功耗分析之Peak Power Analysis2022-10-24 9623

-

#硬声创作季 不同电源的空载功耗Mr_haohao 2022-10-22

-

#硬声创作季 #FPGA Xilinx开发-33 功耗估计和优化-1水管工 2022-10-08

-

480.SOC芯片的数字低功耗方法小凡 2022-10-04

-

浅析CMOS集成电路的动态功耗2022-06-09 9231

-

为什么需要对芯片的leakage功耗特别关注 精选资料分享2021-07-29 751

-

[UPF]低功耗(Low Power Design)and UPF介紹 精选资料分享2021-07-27 2350

-

功耗的来源主要分为哪几种2021-07-26 1675

-

芯片设计中的低功耗技术介绍2020-07-07 3354

-

请问C6678芯片的功耗差异有多少?2019-01-15 4235

-

LED芯片功耗的组成及其芯片设计中的优化技术详解2017-10-24 710

-

低功耗资料SNUG_Power2012-08-17 3833

-

低功耗闪烁器电路--Low power blink led2010-01-13 2140

全部0条评论

快来发表一下你的评论吧 !