带skew的时序计算基础分析

电子说

描述

一、时序计算基础

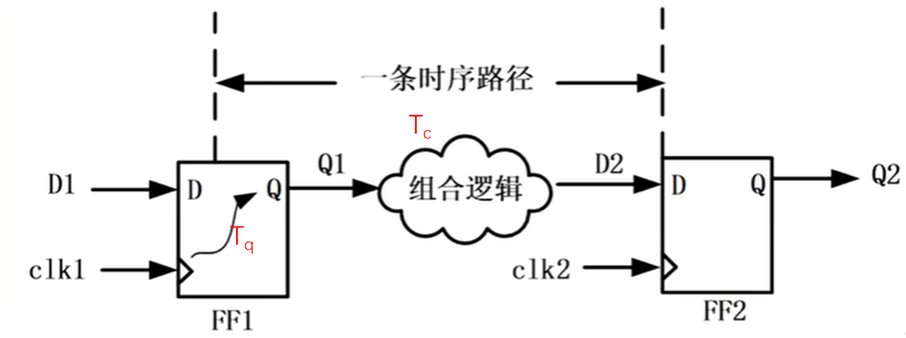

组合逻辑的延迟T c ,从FF1/CK到FF1/Q的延迟为T q ,定义Treal = Tq + T c ,从建立时间和保持时间这两个标准去考察T real 。

现在假设clk1和clk2相位对齐且没有skew。我们考虑D2,当clk1的第一个上升沿a发出数据1时,需要经过Treal的时间1才变成2;

在clk2的f沿,我们要想稳定地采到2,需要在采样窗口内到达,即2要在采样沿f之前一段时间就到达;因此要求Treal < Tperiod - Tsetup

另外,要想采到f沿的数据2,除了2要提前一点到之外,2还不能马上变成3,即2要在采样沿之后稳定一段时间;

我们考虑e沿,e沿采1,要求a沿打出的2不能很快就到,即1变成2的时间要在Thold之后;因此要求Treal > T hold 。

所以,T2 = Thold < T real < (Tperiod - T setup )=T 1 ;T1和T2之间就是数据可以到达的范围;

二、带skew的时序分析

现在我们考虑skew对setup和hold的影响。

对于setup,当 Tcapture > Tlaunch时(正skew)

如果没有skew,那么要求在A点之前1就要变成2,此时不符合要求。

但是有skew存在,setup检查的点从A点延迟到B点,setup检查就满足了。

此时,Treal < (Tperiod - Tsetup + T skew ),即正的skew对setup有好处。

对于hold,当 Tcapture > Tlaunch时(正skew)

不考虑skew的情况下,c沿应该采0,要求0在A之后再变化才算是采稳了。当有skew之后,采样点变成了c沿再加上一个Thold的时间即B点,0可能会采不稳。

此时的要求变成了,Thold + Tskew < T real ,即正的skew让hold更严格。

因此,T2 = (Thold + T skew ) < Treal < (Tperiod - Tsetup + T skew )=T 1 。

当skew为负的时候,上述公式不变,只是 Tskew的值变成负数。

三、从慢速到快速

setup

clk_slow是9ns,clk_fast是6ns;取最小公倍数,工具只考虑前18ns;

a打出数据1,b打出数据2,c打出数据3,d打出4;

f采1,g采2,i采3,j采4;

对于建立时间来讲,g采2的窗口是最短的;对于g沿,还是一样的分析方法,T2 < Treal < T1

此时T1 = Tb - Tsetup

hold

考虑hold,f沿采1,要求1在f沿到达之后还要保持Thold的时间,实际上很好满足;事实上,2还要到b沿之后并经过Treal的时间才会到;同理,g沿的hold也很好满足;

最严苛的就是在e沿,要求0在Thold时间之后再变化。实际上是有可能发生违反的。此时T2 = T hold ,所以,T2 = T hold < T real < Tb - Tsetup =T 1 。

从慢到快和同频同相的区别:

从慢到快,天然会存在重复采样的问题。例如在上面的例子中,e采0,f采1,g采2,h采2(因为3还要等Treal时间之后才能到达),i采3,j采4。

即launch发出了:1 2 3 4,Capture采到了:1 2 2 3 4。

更为常见的例子是分频的例子,例如clk1 6ns,clk2 12ns。那么capture采到的就是11 22 33 44。

可以通过修改RTL的方式来避免这样的问题,见后续讨论;

四、从快速到慢速

这里可以看到a沿发出bbb,c沿发出ccc;

如果clk_fast每一拍都发一个数据,那么clk_slow必然会漏采数据;

因此实际的数据周期并没有那么快,在这个例子中,数据周期是12ns;即a和b沿发出bbb,c和d沿发出ccc;

此时我们的分析范围是12ns和9ns的公倍数,即36ns;3个周期的data,4个周期的clk_low;此时相当于将从快到慢的问题转化为了从慢到快的问题;

又看到了重复采样的问题,h采到bbb,i采到ccc,j采到ddd,k也采到ddd;

我们可以想办法消掉一个采样沿。例如,在e沿发出j沿来采,setup最紧张,我们让j沿不采,那么e沿发出k沿来采。

如下图所示,在设计中做相应的修改,工具会自动插入一个门控时钟,将clk1中没有用到的时钟沿屏蔽掉了(红色虚线)。

在这个例子中,(1)产生了一个counter,我们的目的是对clk2每四个上升沿去掉一个上升沿;看到一个上升沿加1,大于等于4的时候再从1开始;

再利用counter产生一个D2_vld信号,当cnt为3的时候,D2_valid为0,其余情况都为1。

我们最终是要得到Q2。遇到一个clk2上升沿,先看D2_valid信号。G沿采到aaa,H沿采到bbb,I采到ccc;

到J的时候,D2_valid信号无效,没有采样,毕竟k也可以采到ddd;K采到ddd。

上述RTL也会在clk2上的分支上插入一个icg用来控制这个触发器,将J沿消掉,icg由D2_vld信号控制。

五、multicycle约束

当clk1和clk2是倍数关系的时候,使用multicycle的方式更合适。

从慢到快

例如,Clk1的A沿打2,但是Treal很大(组合逻辑很长,也可以插入FF,变成两条path),大于Tb,到达endpoint的时候,clk2已经过去一个周期了;

工具默认E应该采2,但是现在只能采到1,于是就会报违例;例如可以在F处分析,F处才需要变成2;

以clk2周期为单位(-end),我们以第一个上升沿为起点,向右移动2个clk1周期,即在F分析setup:

set_multicycle_path 2 -setup -endrom clk1 -to clk2

上面这句话,不光移动了setup的检查沿,还移动了hold的检查沿;

未设置multicycle_path 2时,A是第一个launch沿,E是第一个capture沿,D是第零个capture沿;

当设置multicycle_path 2时,第一个capture沿从E移动到F,那么第零个capture沿从D移动到E(工具默认在setup检查沿的上一个上升沿检查hold);

此时,Tb + T hold < Treal < Tb - T setup ~ + Tb~;

即要求,数据1要一直保持到Tb + Thold之后才能变;其实数据1在clk2第一个上升沿D之后就可以变了;因此还需要做如下设置:

set_multicycle_path 1 –end –hold -from clk1 –to clk2

这条command只会移动hold的检查沿,以clk2周期为单位移动向左移动1个周期,将检查沿移回到D;

即使设置了multicycle path,告诉工具了E沿不去check,RTL代码也需要做相应的修改(考虑计数器,生成使能信号);以避免输出在有触发沿的时候翻转,造成亚稳态的问题;

从快到慢

假设clk2是clk1的二分频。如前所述,从快到慢的问题应该先转换为从慢到快的问题,再转换为相同周期的问题。

例如,如果clk1是6ns,那么clk2是12ns,D2也是12ns,就和clk2有相同的周期了。因此,尽管从B到G是setup检查最严格的,但实际上rtl也要做相应修改,B沿不发数据,A沿发1,C沿发2。

我们以clk1的周期为单位,将F沿向右移动2个周期,即在G处分析setup:

set_multicycle_path 2 -setup -start -from Clk1 -to Clk2

然后,以clk1的周期为单位,将hold的检查沿移回到F处:

set_multicycle_path 1 -hold -setup -from Clk1 -to Clk2;

-

FPGA 高级设计:时序分析和收敛2024-06-17 2111

-

哪些因此会导致时钟skew过大呢?FPGA中降低时钟skew的几种方法2024-03-13 3373

-

基于FPGA的时序分析设计方案2023-11-22 1405

-

FPGA时序约束之Skew讲解2023-08-14 2253

-

时序分析基本概念介绍<Skew>2023-07-05 5591

-

介绍FPGA设计中时序分析的一些基本概念2023-03-16 3503

-

还是时序分析,但是带skew - 1皮特派 2022-12-07

-

FPGA设计中时序分析的概念分析2022-11-15 2171

-

高速电路信号完整性分析与设计—时序计算2022-02-10 1013

-

时序分析基础2019-03-08 4672

-

时序分析之useful skew的作用分析2018-07-23 19566

-

如何减小clock skew?2016-01-14 6895

-

系统时序基础理论之源同步时序要求2014-12-30 7667

-

使用时钟PLL的源同步系统时序分析2010-10-05 1365

全部0条评论

快来发表一下你的评论吧 !