海外半导体巨头纷纷入局 Chiplet

制造/封装

描述

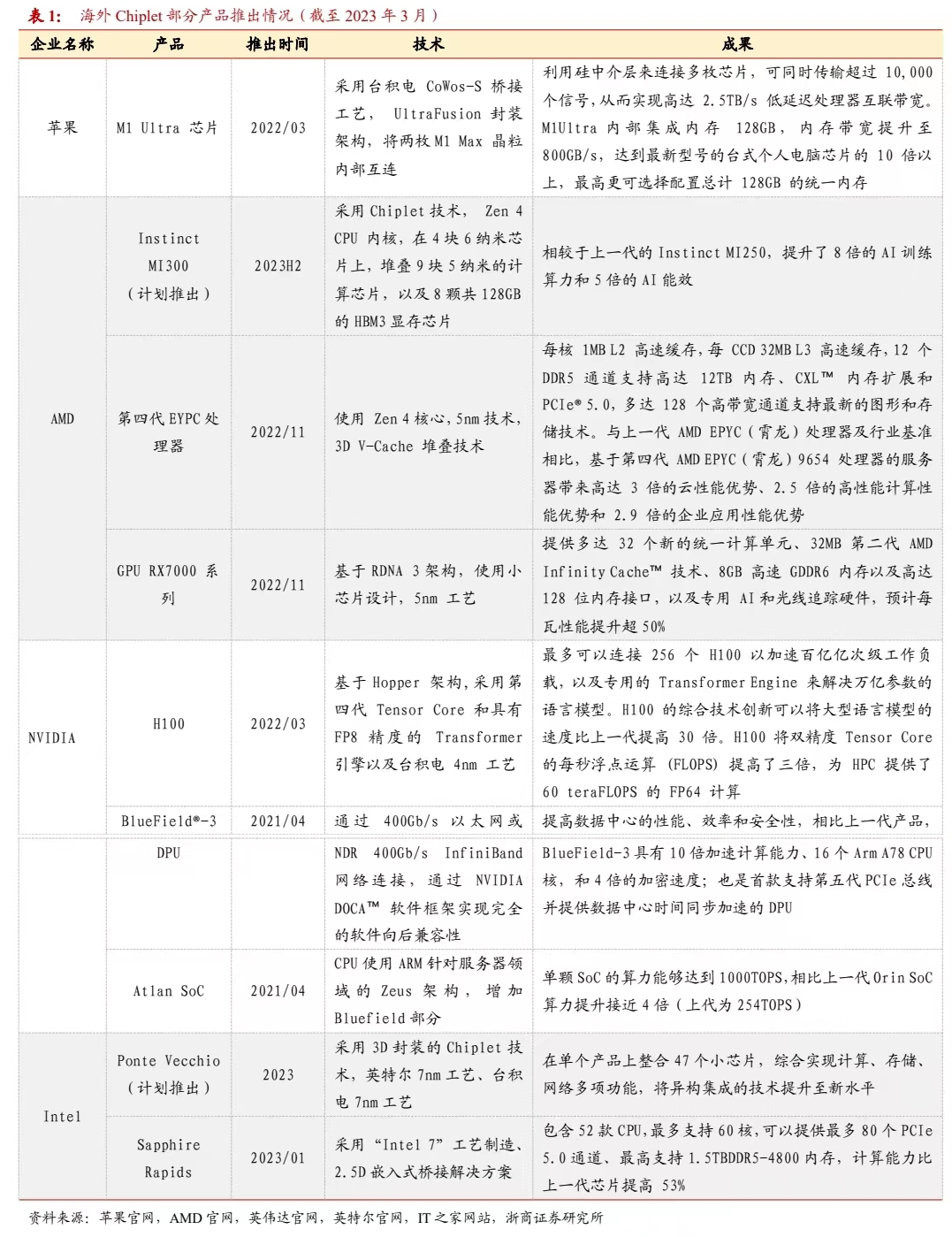

Chiplet能够避开先进制程提升障碍及解决SoC研发问题,已成为各大厂商追逐的焦点。目前,海外的半导体巨头苹果、AMD、英伟达、英特尔等开始纷纷入局 Chiplet,希望以更小的成本来追求更佳的性能。

其中,2022 年 3 月苹果发布的 M1 Ultra芯片采用台积电CoWos-S 桥接工艺,通过 UltraFusion 封装架构实现核心传输速率3200M,算力大幅提升;2023 年1月,Intel官宣推出依靠Chiplet技术研发的Sapphire Rapids 处理器,包含52款CPU,最多支持60核,计算能力比上一代芯片提高 53%。

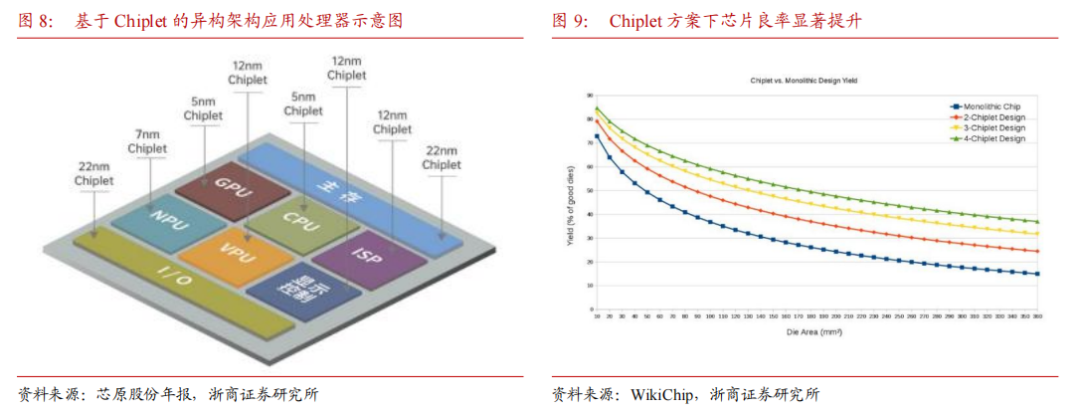

国内厂商抓住当前机遇,不断推进基于 Chiplet 技术的产品布局。由于我国半导体行业起步较晚,尚与国外存在一定差距。Chiplet 能够缓解设备和材料受限的压力,一定程度上解决国内高端芯片难题,是破解海外技术封锁的关键。Chiplet作为提升算力密度的重要路径,有望成为我国缩小与国外差距、解决“卡脖子”问题的重要机会,目前国内相关厂商大力布局中。其中,华为 2019 年 1 月研发推出鲲鹏 920 处理器,采用7nm制造工艺,基于 ARM 架构授权,典型主频下,SPECint Benchmark 评分超过 930,超出业界标杆 25%,能效比优于业界标杆 30%;国产 GPU 厂商壁仞科技 2022 年 8 月发布运用 Chiplet 工艺的 BR100 系列 GPU,包含 2 颗计算芯粒,采用 7nm 制程,实现高达2048TOPS INT8 算力。

国内厂商抓住当前机遇,不断推进基于 Chiplet 技术的产品布局。由于我国半导体行业起步较晚,尚与国外存在一定差距。Chiplet 能够缓解设备和材料受限的压力,一定程度上解决国内高端芯片难题,是破解海外技术封锁的关键。Chiplet作为提升算力密度的重要路径,有望成为我国缩小与国外差距、解决“卡脖子”问题的重要机会,目前国内相关厂商大力布局中。其中,华为 2019 年 1 月研发推出鲲鹏 920 处理器,采用7nm制造工艺,基于 ARM 架构授权,典型主频下,SPECint Benchmark 评分超过 930,超出业界标杆 25%,能效比优于业界标杆 30%;国产 GPU 厂商壁仞科技 2022 年 8 月发布运用 Chiplet 工艺的 BR100 系列 GPU,包含 2 颗计算芯粒,采用 7nm 制程,实现高达2048TOPS INT8 算力。

Chiplet 有望满足不断增长的芯片性能需求和功能多样化需求。国外巨头 Intel、AMD、苹果、SAMSUNG、台积电等已积极布局 Chiplet 领域。2022 年 3 月,Intel、AMD 等十大芯片行业巨头联合组建“UCle 联盟”,推出全新的通用芯片互联标准,使市场上不同 IP 芯粒之间实现高速互联,旨在打造开放性的 Chiplet 生态系统,有望推动解决 Chiplet 标准化问题,有望带动全球 Chiplet 产业链快速发展。

国际:技术领先引领发展

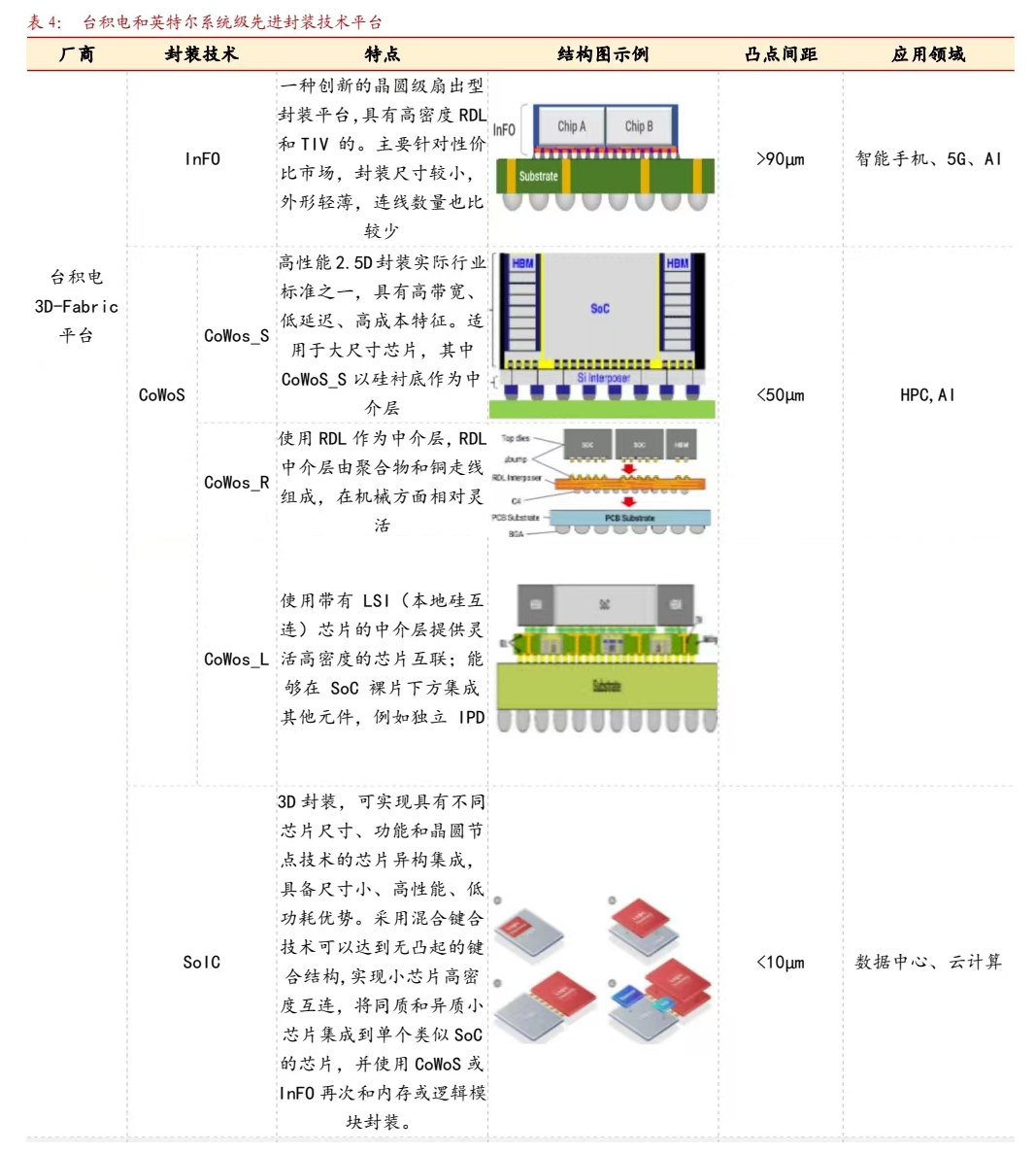

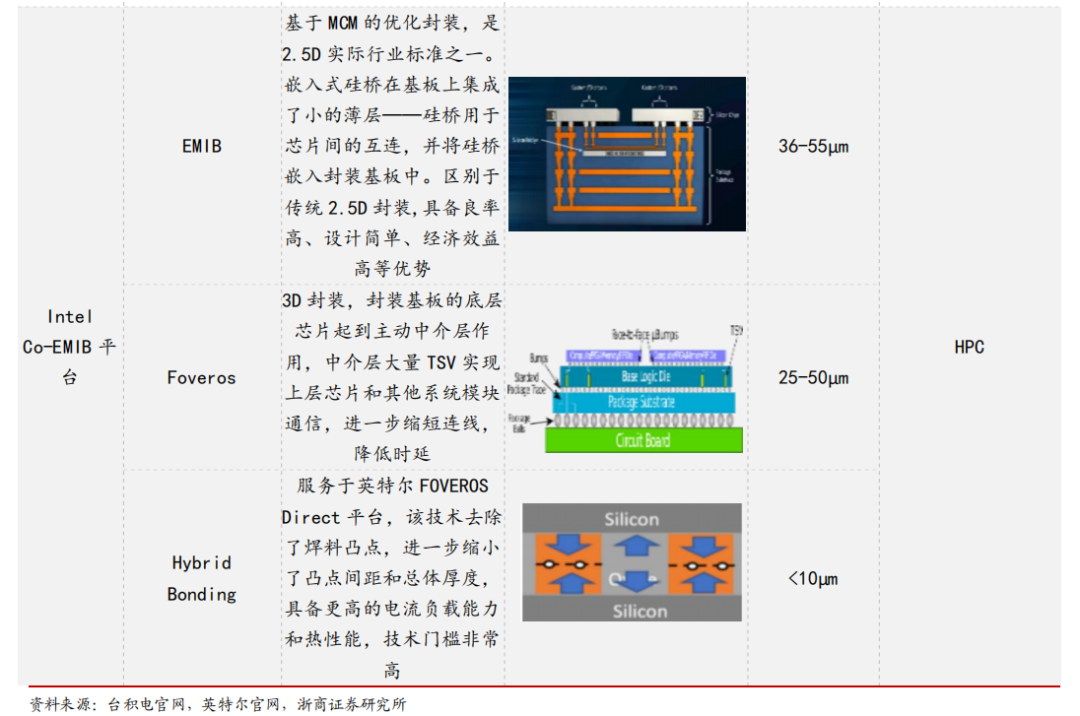

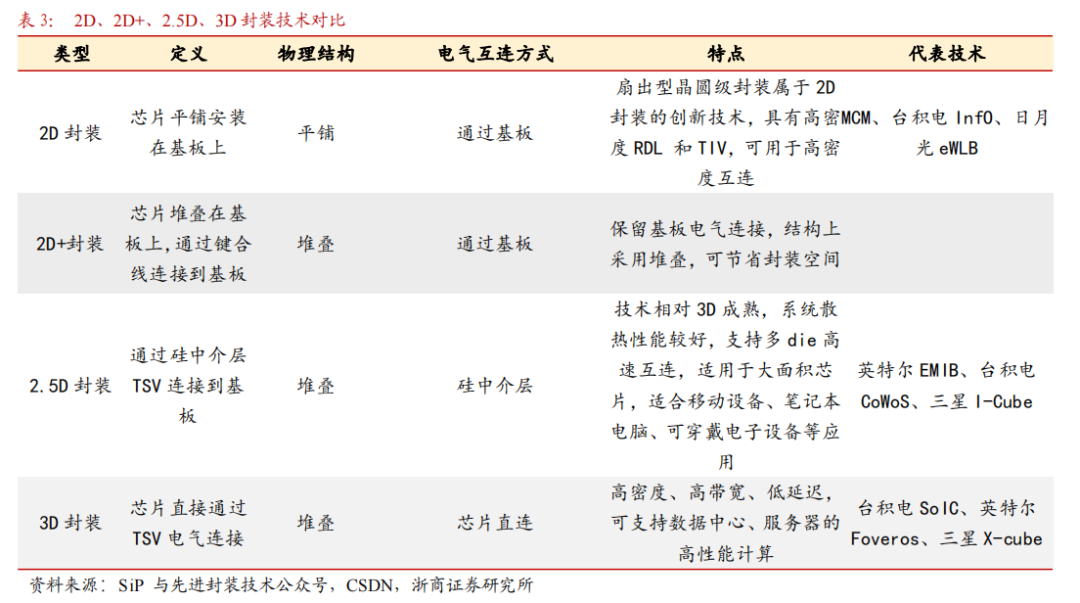

目前国际先进封装巨头 Intel、台积电已拥有相对成熟的 Chiplet 产能布局。1)台积电开发的 InFO、CoWoS 以及 SoIC 先进封装技术现已应用于智能手机、5G 网络、AI、电子穿戴设备等多个领域。2)Intel 开发的 EMIB、Foveros 以及基于以上二者开发的 Co-EMIB 先进封装技术,开拓了全新的 3D+2D 封装设计思路。

台积电:1)INFO 属于 2D 封装技术,可应用于射频、无线芯片、处理器、基带芯片、图形处理器和网络芯片的封装。TSMC 依靠 INFO 取代三星成为苹果 iPhone 处理器的生产厂商。2)CoWoS 属于 2.5D 封装技术,于 2012 年开始量产,是将芯片封装到硅转接板(中介层)上,使用硅转接板上的高密度布线进行互连,再安装在封装基板上。CoWoS 与 InFO 的区别是,前者通过硅转接板互连,主要针对高端市场,连线数量和封装尺寸相对较大;后者通过基板互连,主要针对性价比市场,封装尺寸和连线数量相对较少。3)SoIC 技术采用创新的多芯片堆栈技术,包含 CoW(Chip-on-wafer)和 WoW(Wafer-on-wafer)两种技术,属于 3D 封装。SoIC 没有凸点的接合结构,因而拥有更高的集成密度和更好的性能。

Intel:1)EMIB 是 Intel 提出的 2D 封装技术,属于有基板类封装。因为没有 TSV,EMIB与 2.5D 封装相比工艺和设计更加简单,封装良率更高。同时相比于传统的 SoC 芯片,EMIB可以把 10nm 工艺(CPU、GPU)、14nm 工艺(IO 单元、通讯单元)和 22nm 工艺(内存)整合到一起。2)Foveros 是 Intel 推出的 3D 堆叠封装技术,与 EMIB 相比,Foveros 在性能和功能方面差异不大,但在体积、功耗方面占优势,更适用于小尺寸产品。3)Co-EMIB 是EMIB 和 Foveros 的结合体,其中 EMIB 主要负责横向连接,Foveros 负责纵向堆栈。通过Co-EMIB 可将多个 3D Foveros 芯片进行拼接以制造更大的芯片系统,提供堪比单片的性能。

国内:前瞻布局奋力追赶

根据芯思想研究院数据,2022 年长电科技是全球第三,中国大陆第一 OSAT 厂商,全球市占率 10.71%。2023 年,公司将主要投资的重点放在汽车电子专业封测基地,2.5D Chiplet,新一代功率器件封装产能规划等未来发展项目。Chiplet 小芯片解决方案的多样化研发、PLP 面板级封装实用技术研发、碳化硅,氮化镓等新一代功率器件模组的研发将是 2023 年的重点推进方向。2023 年 1 月,公司宣布 XDFOI Chiplet 高密度多维异构集成系列工艺进入稳定量产阶段,同步实现国际客户 4nm 节点多芯片系统集成封装产品出货。

根据芯思想研究院数据,2022 年通富微电是全球第四,中国大陆第二 OSAT 厂商,全球市占率 6.51%。公司收购 AMD 苏州及 AMD 槟城各 85%股权,是 AMD 最大的封测供应商,占其订单总数 80%以上,已为其大规模量产 Chiplet 产品。目前,公司自建 2.5D/3D 产线全线通线,1+4 产品及 4 层/8 层堆叠产品研发稳步推进;基于 Chip Last 工艺的 Fan-out 技术,实现 5 层 RDL 超大尺寸封装(65×65mm);基于超大多芯片 FCBGA MCM 技术,实现最高 13 颗芯片集成及 100×100mm 以上超大封装;完成高层数再布线技术开发,可为客户提供晶圆级和基板级 Chiplet 封测解决方案,并充分利用其 CPU、GPU 量产封测平台,深度参与国产半导体高端芯片产业化过程。

封测技术:先进工艺升级注入活力

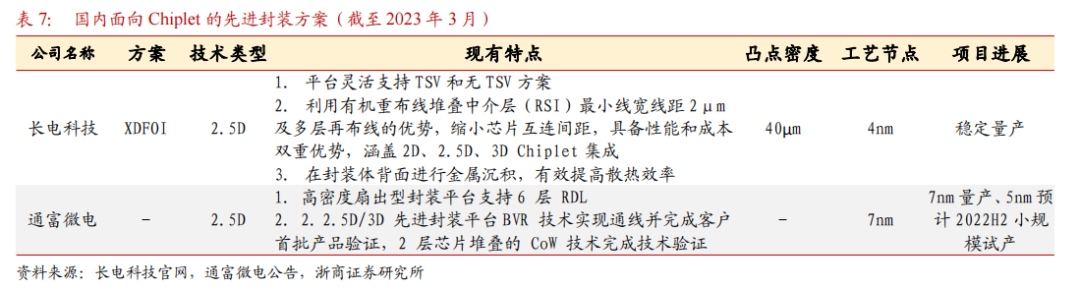

Chiplet 推动封装技术升级,带动测试需求同步增长。1)Chiplet 对封装工艺提出更高要求。Chiplet 与 SiP 相似,都是进行不同元件间的整合与封装,而 Chiplet 的各裸芯片之间是彼此独立的,整合层次更高。Chiplet 方案需要减少 die-to-die 互连时延同时保证信号传输质量,要求实现更高的芯片布线密度,进一步催化先进封装向高集成、高 I/O 密度的路线发展。2)Chiplet 将推动芯片测试需求增长。相比 SoC 封装,基于 Chiplet 架构的芯片制作需要多个裸芯片,单个裸芯片失效会导致整个芯片失效,需要进行更多测试以减少失效芯片带来的损失,带动芯片测试业务需求增加。

国内领先封测企业顺应趋势,在支持 Chiplet 方案的先进封装布局已初显成果。长电科技 XDFOI Chiplet 高密度多维异构集成系列工艺已进入稳定量产阶段,实现国际客户 4nm节点多芯片系统集成封装产品出货。XDFOI 可将有机重布线堆叠中介层厚度控制在 50μm以内,微凸点(µBump)中心距为 40μm,实现在更薄和更小单位面积内进行各种高密度工艺集成,最大封装体面积约为 1500mm²系统级封装。通富微电是 AMD 重要封测代工厂,在Chiplet、WLP、SiP、Fanout、2.5D、3D 堆叠等方面均有布局和储备。公司开启“立足 7nm、进阶 5nm”的战略,已具备 7nm Chiplet 先进封装技术大规模生产能力,深入开展 5nm 新品研发,全力支持客户 5nm 产品导入,现已完成研发逐步量产,助力大客户高端进阶。

封测设备:国产化渗透有望提速

Chiplet 提高封测设备要求,市场需求大幅增加。1)Chiplet 实施关键之一在于先进封装技术的实现,因此对封装设备提高了要求及需求。封装设备需求增加:例如研磨设备增加(晶圆需要做的更薄)、切割设备需求增加、固晶设备增加(DieBond 要求更高);新设备需求:如凸块(bump)工艺涉及到曝光、回流焊等设备等。先进封装设备包括刻蚀机、***、PVD/CVD、涂胶显影设备、清洗设备等。2)Chiplet 技术为保证芯片良率,购置检测设备的数量将大幅增加。Chiplet 需要的测试机数量将远高于 Soc 芯片测试机。目前 Soc芯片测试对于可能数模混合的低成本存储芯片等采用抽检方式,而 Chiplet 技术为保证最后芯片的良率,需保证每个 Chiplet 的 die 有效,将对每个 die 进行全检。

审核编辑:黄飞

-

万年芯解读国产半导体产业年内新增16万家入局者2024-12-02 791

-

Chiplet真的那么重要吗?Chiplet是如何改变半导体的呢?2023-11-27 1637

-

半导体Chiplet技术的优点和缺点2023-06-25 4294

-

半导体Chiplet技术及与SOC技术的区别2023-05-16 2703

-

科技巨头纷纷入局的元宇宙价值有多大2021-11-05 2612

-

科技巨头纷纷入局元宇宙 爆火的元宇宙是什么呢2021-11-03 2812

-

半导体芯片产业的发展趋势2021-02-04 12663

-

木林森入局UVC半导体杀菌消毒行业 将具备更大的发展空间2020-04-10 2113

-

康佳存储正式入局半导体行业 战略及发展方向一览2020-03-20 3329

-

国内科技巨头入局成必然 VR硬件创业公司将面临重重挑战2020-01-14 1466

-

新机遇 科技巨头纷纷入局医疗保健领域2019-01-12 2502

-

智能音箱市场大爆发 巨头纷纷入局2018-07-04 4796

-

国防威胁减除局寻求抗辐射高频模拟和射频半导体2012-12-04 2943

全部0条评论

快来发表一下你的评论吧 !