探讨晶体管尺寸缩小的原理

制造/封装

描述

原文作者:JamesG

所谓关键尺寸的7nm不是真的7nm,是在实际线宽无法大幅缩小的前提下,通过改变晶体管结构的方式缩小晶体管实际尺寸来达到等效线宽的效果

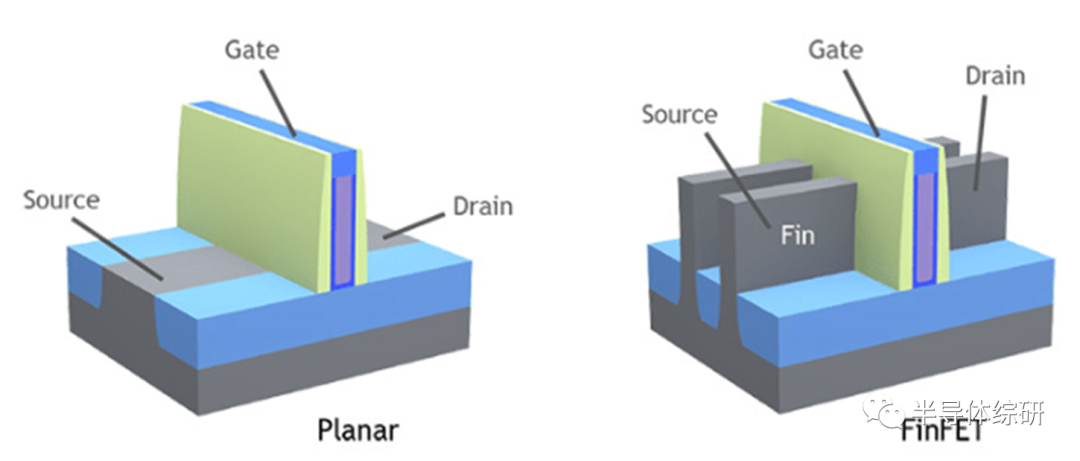

从平面晶体管结构(Planar)到立体的FinFET结构,我们比较容易理解晶体管尺寸缩小的原理。如下图所示:

那么从20nm开始到3nm,晶体管的结构都是FinFET的。结构没有变化的条件下,晶体管尺寸是如何缩小那么多的呢? 之前网络上的解释是:某公司的7nm技术是采用了多重曝光方法以后提升了分辨率 其实这种说法是错误的,或者说至少是有很大误导性的 多重曝光技术是现代先进半导体工艺里的一个通用技术了,如果我没有记错,从32nm或者28nm工艺节点开始,多重曝光技术就已经被应用了 所以从14nm到7nm工艺,如果不是用EUV替代DUV,那现有的光刻技术是无法大幅度降低现况的。也就是说,要缩小晶体管的尺寸,必须另找办法 微缩晶体管的尺寸的方法不少,这里讲几个常用的方法

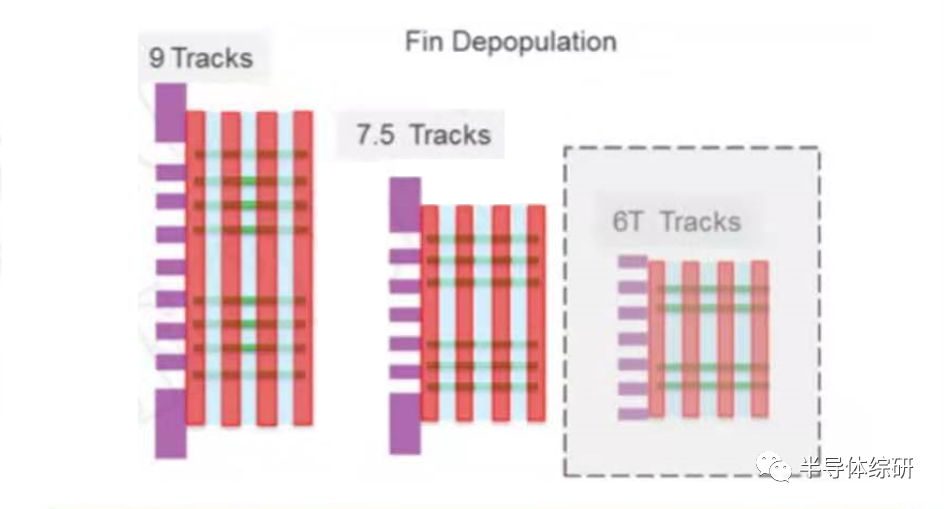

首先,一个CMOS晶体管里无论是P管还是N管,它的鳍片(Fin)的数量一定不止一个。因为单个Fin太细,通过的电流不够大,所以需要多个Fin并联来提高电流

在Fin的间距不变的情况下,Fin的数量就决定了晶体管的高度。所以行业里要缩小晶体管的尺寸,就是尽量减少每个MOS管里需要的Fin的数量 由下图可知,从左到右,晶体管的鳍片数量从4个减少到3个,然后是2个。这样整个晶体管的面积就大幅缩小了。从20nm一直到5nm甚至3nm,这个数量一直在减少(当然,通过采用EUV和多重曝光技术,Fin的间距也是同时在不断缩小)

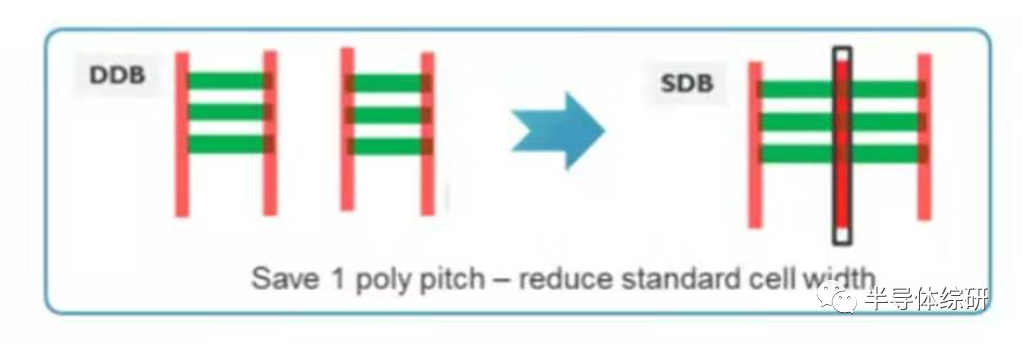

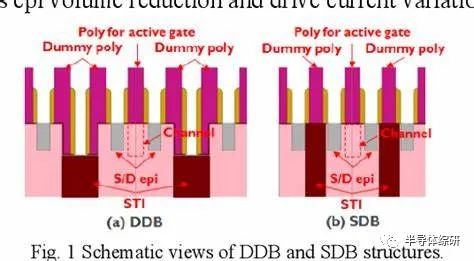

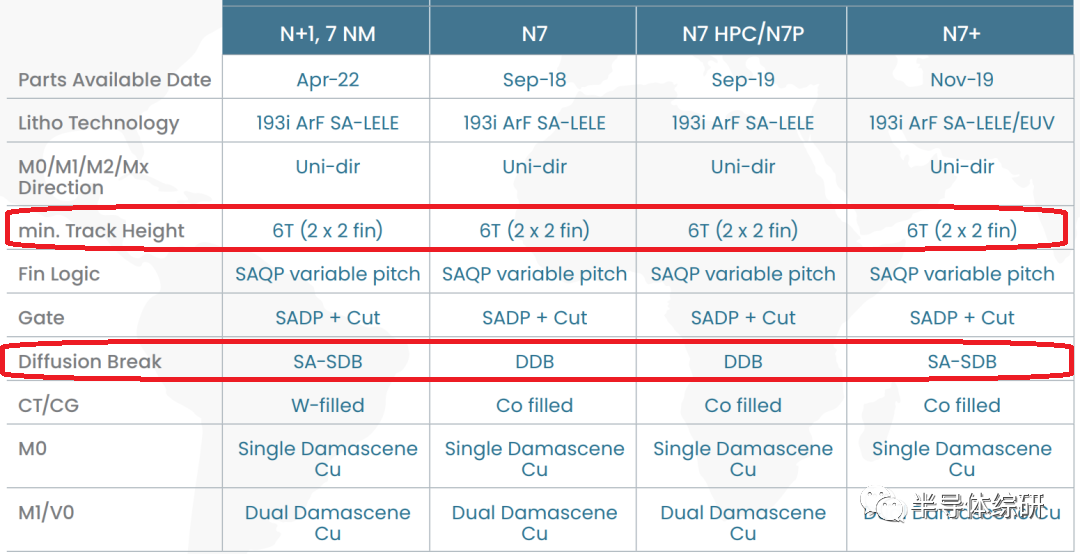

上图里Track这个词是衡量晶体管高度的一个单位。它实际上是第1、2层金属层里最细的连线的间距大小。一个间距大小就是一个Track,晶体管高度是连线间距的几倍,就叫几个Tracks 金属连线的间距值MxP和栅极线条最小间距CPP值(上图里竖直方向的红色线条)就基本反映了图形加工工艺的水平,也决定了晶体管的大小 另外,还有一个比较巧妙的路径就是:如果不能缩小晶体管的面积,那我们也可以缩小晶体管之间的间隔空间来实现密度提升啊 晶体管之间要做电性能隔离,一般都是用扩散层实现的,这个叫Diffusion Breaks。原本每个晶体管各自有一个隔离带,叫DDB(Double Diffusion Breaks),现在为了节约空间,只用一个隔离带了,叫SDB(Single Diffusion Breaks) 就好比你家院子和邻居院子如果各修一个篱笆,自然会占用更多土地面积。于是你们两家商量一下,想办法合建一个篱笆来隔离,自然就能多出一些空间来 下面两张图分别是DDB和SDB的俯视图和横截面示意图,大家看了自然就会明白

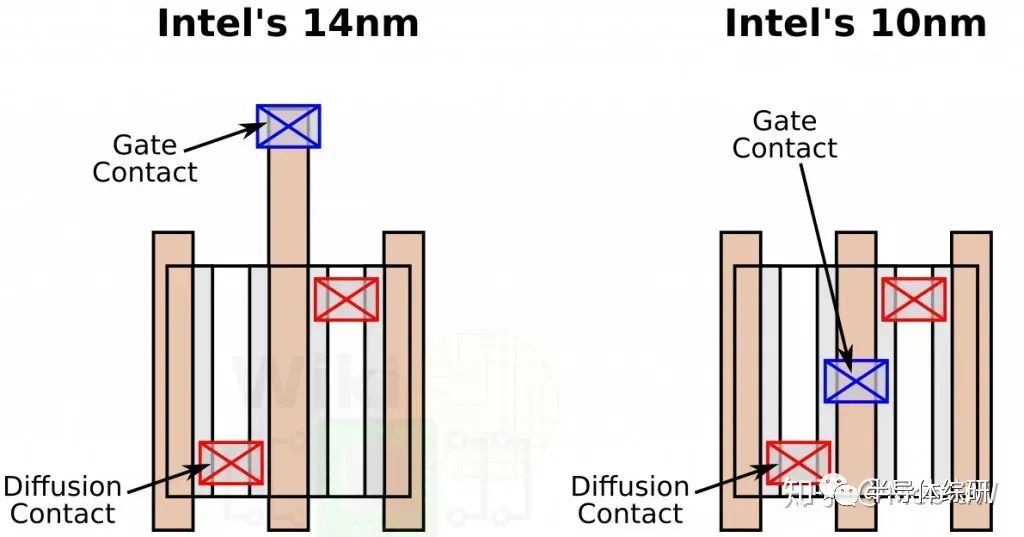

另外,一种叫COAG(Contact Over Active Gate)的技术。原本需要在空白地方制作栅极接触点会占用额外的空间,所以人们想办法把接触点的位置直接做到了栅极的上面,就可以节约大量空间。如下图所示:

这个想法当然是非常绝妙的。但可惜的是,由于各种原因,这个技术的良率一直做不好,直接影响了Intel先进工艺的开发进度。这也是他家工艺逐渐被台积电和三星赶上并超越的重要原因之一吧 以上就是几个缩小晶体管尺寸的常用技术方案了。其实还有其它很多微缩的方法,比如用金属钴(Co)代替铜,用空腔代替传统金属连线介电层等方案来缩小BEOL段的金属连线尺寸的方法。

不过看到这里,或许就会有很多朋友提出疑问:既然如此,是不是光刻技术在后续就不那么重要了? 当然不是这样。恰恰相反,光刻技术的演进(从光刻设备到光刻工艺)从来都没有停止过。半导体器件里实际的图形线宽也在不断缩小着。

审核编辑:黄飞

-

CMOS晶体管的尺寸规则2024-09-13 5851

-

有什么方法可以提高晶体管的开关速度呢?2024-01-12 2397

-

晶体管是怎么做得越来越小的?2023-12-19 1609

-

3D晶体管的转变2023-07-16 1717

-

什么是鳍式场效应晶体管?鳍式场效应晶体管有哪些优缺点?2023-02-24 14769

-

什么是达林顿晶体管?2023-02-16 2092

-

什么是晶体管 晶体管的分类及主要参数2023-02-03 2565

-

MIT用14000个碳纳米管晶体管造出16位微处理器2019-09-23 4002

-

概述晶体管2019-05-05 2830

-

数字晶体管的原理2019-04-09 2538

-

晶体管的分类与特征2018-11-28 2697

-

晶体管和IC的外形封装尺寸大全2012-08-03 8568

-

集成电路晶体管封装尺寸图2009-10-16 911

全部0条评论

快来发表一下你的评论吧 !