DDR仿真和测试完美对应的经典案例

存储技术

描述

作者:一博科技高速先生成员 黄刚

相信大家过完一个美美的春节后,学习的热情一定会暴涨,反正高速先生给大家分享技术文章的热情是非常高涨的哈!打从推出这个系列的仿真和理论相结合的话题后,文章受到了很多忠实粉丝的喜爱,大家纷纷表示既能学到理论知识,还知道怎么从仿真中去验证,甚至有一些小伙伴们已经深深的陷入到仿真里面去,无法自拔了。因此高速先生趁热打铁,在春节后再加推几期,继续围绕着这个话题分享文章!

经过高速先生对粉丝文章喜爱度的研究发现,DDR方面的话题始终受到大家的热捧,原因可能包括了大多数产品都会有DDR内存系统,然后DDR系统又是很关键且容易出问题的一个模块,还有就是DDR的原理和应用特别让人着迷等等吧。All right,那今天就再给大家分享一个DDR仿真和测试完美对应的经典案例吧!

不知道现在大家做的DDR4系统的指标是怎么样了?从高速先生和最近众多客户的配合来看,从一个通道的总容量和速率上都基本上拉到了极限,从单个颗粒的容量,很多已经从8Gb提升到了16Gb,运行速率也从typical的2400M拉到3200M了。下面要分享的这个案例就是这个的一个case!

这个客户的一个DDR通道是1拖5的结构,每个颗粒的16Gb是容量,需要跑到的速率是3200M,通过这个描述,就知道这个系统的PCB设计不会很好做!这个项目是我司设计部门的同事设计的,而且也有相关的内部指导可以遵照,因此设计完就去生产加工了。等板子贴片回来后,客户下载程序去测试时,就猛然发现运行不到额定的3200M的速率!

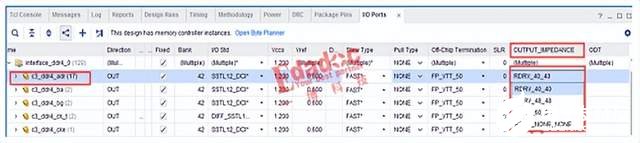

客户也测试了好几片板子,情况都差不多,大概只能运行到2400M左右,再往上就不稳定了。由于我们和这个客户合作比较久了,大家也都没有太慌,经过和客户详细的沟通,我们把调试的方向转到了主芯片的驱动配置上。这款型号主芯片客户用得比较多,驱动配置的页面,如下所示:

像这种一拖多的DDR系统,我们最先会把debug方向放在地址控制信号和CLK上面,这个原因在之前很多篇文章已经说过了。我们看到客户已经遍历了上面红框的驱动内阻,从可以选择的40,48,60等多种驱动选出了较好的40欧姆内阻驱动,但是依然不能稳定的跑到3200M上。连驱动内阻的配置都遍历过,感觉好像没有其他有效的设置了吧,真的要立马重新改板设计了?

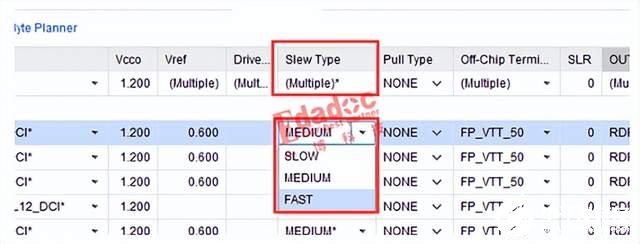

先别慌,还好高速先生也对这款芯片灰常的了解,除了传统的驱动内阻可以配置外,Slew Type也是一个很重要的点!没错,就是下面这个配置项!

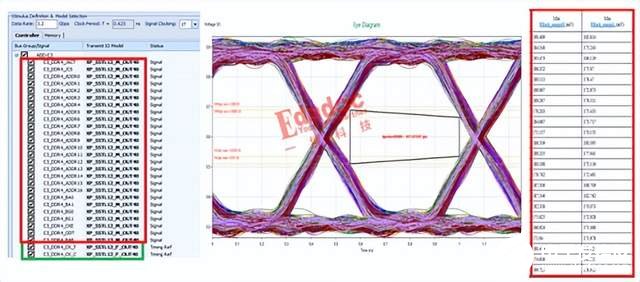

该芯片有FAST,MEDIUM和SLOW三个配置可以选择!而且我们也拿到了该芯片的仿真模型,模型比较齐全,也同样有这几项配置可以选,于是高速先生打算通过仿真去进行验证,看看能不能顺便把问题一并解决了。

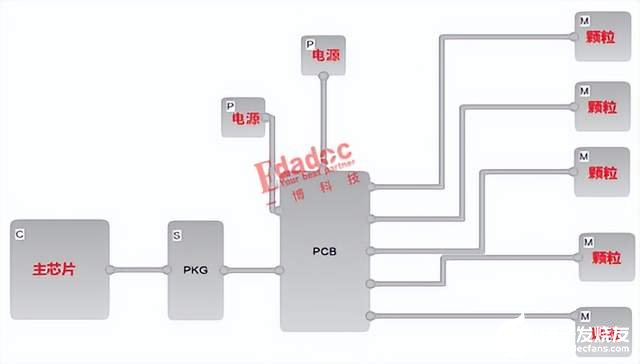

于是我们迅速在仿真软件把仿真拓扑搭起来,就是下面这样的拓扑!

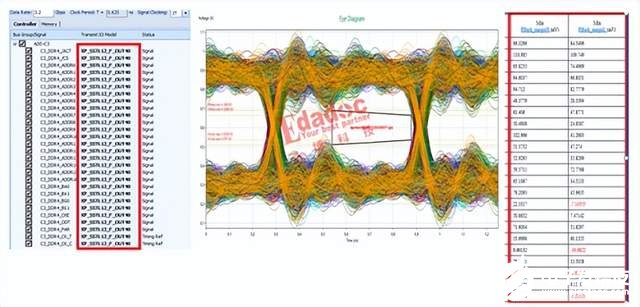

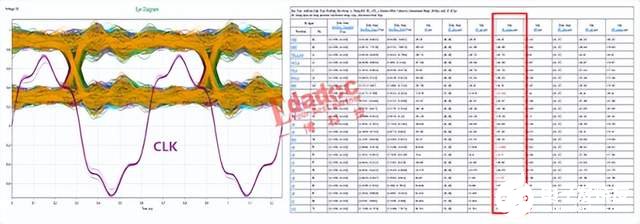

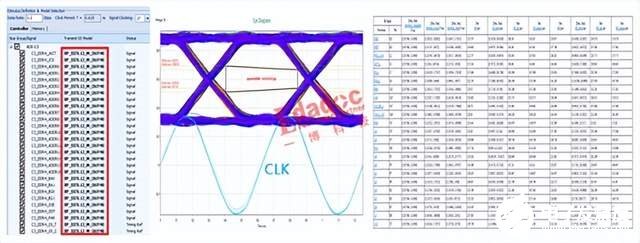

我们先按照客户原始的配置,地址控制和时钟CLK都是FAST模式,40欧姆内阻去选择仿真模型,如下所示:

发现最差的颗粒信号质量的确是有问题,存在明显的ring back,从而也导致时钟采样出现问题,同时也能发现,时钟采样的时序本身没有问题,只是地址控制信号质量的问题。

这和客户的测试结果也挺吻合的!

那我们就换成地址控制MEDIUM模式,时钟CLK还是FAST模式仿真看看,结果就变成下面这样了。好开森,地址控制信号的信号质量全部都没问题了!!!

是不是在仿真中意味着就ok了,人往往在最开心的时候容易受到暴击,的确,地址控制信号的信号质量都ok了,但是时钟又出来搞事了!地址控制信号的质量都没问题,

CLK时钟的信号质量也没问题,但是时序却出错了,从上升沿的采样位置能明显看到,建立时间裕量又不够了!

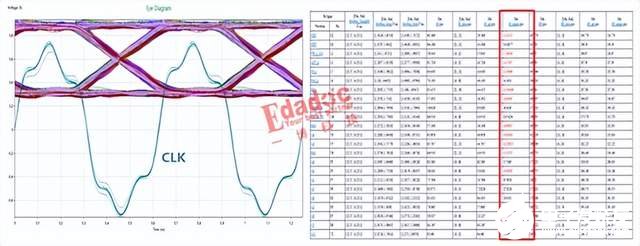

但是我们还是壮着胆子让客户试试这种地址控制MEDIUM模式,时钟CLK选FAST这样的配置,果不其然,客户很快就传来了测试结果!

的确,从仿真结果来看,单纯的地址和CLK的信号质量都是满足要求的,只是建立时间的时序裕量不足,我们知道,时序裕量问题的确也是可以通过降频来弥补的,因此我们对仿真的精度有了更大的信心!

好!最后再试一种组合,一定要成功!就是地址控制信号和CLK时钟都选用MEDIUM模式,我们先来看看仿真结果!这下厉害了,地址控制信号ok,上面的仿真已经知道,现在把CLK时钟也变成MEDIUM后,时钟本身满足信号质量的同时,时序也变ok了,结果列表没有出现裕量不足的提醒了,完美!

然后再反馈到调试去,客户终于传来了好消息!

最后总结下,这又是一个仿真和测试互相配合验证从而通过仿真指导调试来解决问题的经典案例,在初始配置调试不通过的时候要保持冷静,找到入口去尝试更多的芯片配置。从案例中我们展示了仿真和测试的配合,其实选择配置的过程也是理论应用于实际的过程,有了理论的支撑,我们才能更好的去选择仿真的配置和调试的配置,从而解决问题,大家都get到了吧!

审核编辑:黄飞

-

教大家对DDR4做仿真小凡 2022-09-13

-

关于DDR3高频电路的设计和测试疑问2017-10-26 2905

-

DDR调试不通?先别扔,这个操作可能帮你逆袭!2023-02-02 572

-

Quamtum-SI DDR3仿真解析2010-04-29 4839

-

基于Cadence的DDRⅡ仿真设计2012-02-13 621

-

DDR怎么学习,从仿真开始2018-09-15 6936

-

以DDR内存条为例教你进行SI仿真2023-02-07 3446

-

如何利用ADS仿真软件辅助进行DDR的电路仿真?2021-05-17 16509

-

DDR压力测试内容2021-06-24 1883

-

DDR测试项总结及详细步骤2021-06-26 4316

-

DDR DIMM双面弹测试治具介绍2022-09-08 2413

-

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板2022-10-10 9482

-

DDR I/II总线的仿真分析方法2022-10-21 719

-

DDR设计和仿真技术详解2022-10-24 925

-

从数字硬件工程师“跨界”DDR仿真与测试之路2023-02-11 2387

全部0条评论

快来发表一下你的评论吧 !