泰瑞达创新测试策略,助力车规芯片实现零质量缺陷目标

泰瑞达创新测试策略,助力车规芯片实现零质量缺陷目标

描述

电子发烧友网报道(文/李弯弯)近几年,汽车电动化、智能化迅速发展,这使得汽车上使用的芯片数量越来越多、金额越来越大。每辆车上用到的芯片数量几乎翻倍,一些高端车型使用的芯片数量甚至超过1000颗,每辆车上所使用的金额比重也大幅提升。

然而,车规时代基本追求零质量缺陷目标,车规产品全流程都要进行严格的质量把控,不同环节都有不同的质量管理标准,如AECQ100、IATF 16949、ISO26262等。对于企业来说,如何低成本设计、生产出高质量的车规产品,离不开高效测试解决方案的强力助攻。

质量问题带来的各种显、隐性成本

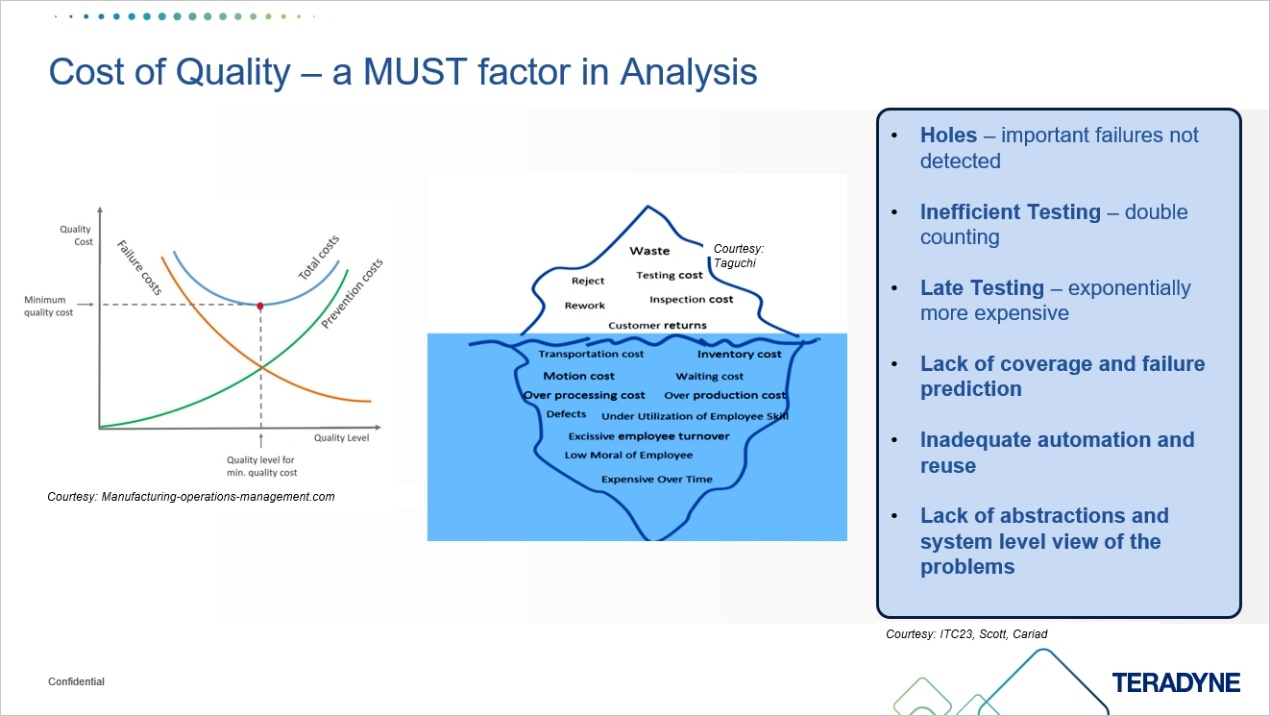

“质量问题,会带来各种显性或隐性成本。”在日前的泰瑞达年度媒体见面会上,该公司中国区总经理Felix Huang先生向媒体表示。如下图所示,最左侧横坐标是质量等级,纵坐标是质量带来的成本。可以看到,红色这条线表示,质量等级越高,后面器件带来失效的成本就会降低;绿色这条线表示,为了追求质量要做一些预防性的提前检测,因此为了追求高质量,额外会带来成本的增加。实际上,每家企业都会考虑成本和质量的平衡点。

Felix Huang先生解释说:“虽然都是装在车上,不同芯片的质量和成本要求不一样。比如,用在自动驾驶和智能座舱上的主控芯片,它们的质量要求必然不同,自动驾驶对质量要求更高,因为涉及到安全性的问题。其他的还有MCU、传感器等质量要求也会有区别。”

如上图中间的冰山图,海平面之上是能够看到的显性的成本,如质量问题带来的客退、测试成本;海平面之下是一些隐性成本,如果质量控制不好会带来很多成本,如库存成本、运输成本,再往下甚至会引起人员变动带来的成本。Felix Huang先生认为,隐形带来的成本对社会的影响远远超过显性成本。

此外,如果测试方案不好,也会到来很多问题,比如:有一些失效问题没办法检测出来;由于测试方案不好,需要多次测试,增加测试工序;有些问题在前面就应该识别,结果到后面才识别出来,从而增加生产和装配成本等。在Felix Huang先生看来,在产品设计的初期就应该考虑好测试的设计和策略,这样才能有效避免上述问题。

如何达成车规要求的零质量缺陷目标

如何才能达成车规要求的零质量缺陷目标呢?Felix Huang先生认为,首先是要考虑测试策略,即在开始设计芯片的时候,就要想要达到0 DPPM的效果,在设计阶段到最终量产阶段每个环节是怎样的,如何去保证质量;其次是流程怎么做,即在实现这个流程的过程中,如何进行多步骤协作、多人协作,如何做到尽可能自动化,减少人为因素带来的问题;最后是需要什么样的工具来支撑,是否有可靠的工具能够做实时性、可预测性、智能性分析。

具体来看,在测试策略方面,需要有一个比较灵活的测试流程来尽量优化质量成本。在完成芯片的过程中有多个检测阶段:1、Wafer Sort(晶圆测试),也就是在晶圆阶段通过测试机检测有没有坏的Die;2、Partial Assembly,最终芯片会装配在PCB板上,这个阶段要对PCB板装配进行检测;3、Final Test(成品测试),即在芯片完成之后切割Die,之后进行封装,对封装也需要做检测;4、System Level Test,这个是把芯片安装到最终应用的系统板上,需要做一个系统级测试。针对上述每个阶段的测试,泰瑞达都有不同的机台可以覆盖。

泰瑞达能提供较灵活的测试策略(FLEX TEST)。从上图可以看到,两侧都有箭头,也就是说测试的侧重点可以左移,也可以右移。什么意思呢?很多芯片上的缺陷都希望能够尽早发现,如果很多问题在晶圆测试阶段就能够检测出来,到了成品测试时就不需要再去检测,只需要去检测封装时Die与Die之间互连可能带来的问题。

对于一颗芯片来说,其测试成本相较于工艺、封装占比较小,将测试项更多的移到前面,越早发现问题,就可以省去后面封装带来的成本。从成本的角度来看,可以考虑检测是不是能够往前移一点。当然有些不能移的,就只能在后面添加上去。

要实现这样一个FLEX测试,对测试的要求其实很高,首先是要求它的机台本身要求非常好的稳定性、可重复性;其次是要求其测试能力和覆盖率要达到要求。

测试流程方面,它并不像表面看上去那么简单,不仅仅是筛出芯片的好和坏。它需要不断分析数据,分析完数据后,才能确定哪些项目要往移。这里面需要非常多的技术和工具支撑。Felix Huang先生介绍说:“泰瑞达内部有一个专门的软件工具PortBridge,早期IC设计人员和ATE测试人员很难沟通,PortBridge起到了一个沟通桥梁的作用。EDA的设计人员、DFT人员可以通过Mentor Graphics的理念,用EDA工具直接连接我们的测试机直接验证设计向量。”

PortBridge这个软件装集成在IG-XL开发环境里面,通过EDA工具访问测试机控制晶圆测试、成品测试和SLT,根据它们的结果实时在线做调试。这使得在设计阶段就可以直接看ATE的测试结果,并反馈给Fab,其作用主要是在早期阶段有助于调试良率。

此外,在ATE开发测试程序上,泰瑞达也探索出了高效的方法和工具。从1995年到2020年,测试程序复杂度越来越大。最早测试一颗SoC混合芯片可能只有200个测试项,代码量大概一两千行,现在芯片要测试更加复杂的功能及不同的场景,代码量大概到了2万行。以前这个阶段一个或几个工程师就能基本完成,如今不仅仅是芯片复杂度增加,开发周期也要求越短越好,基本上都需要多人开发,开发测试程序基本都是一个团队。Felix Huang先生告诉媒体:“因为需要协同不同地方的人开发,最后再整理调试,这对一些工具、自动化、智能化提出了要求。在这方面,我们有多人协同分布式处理开发工具Git,以自动把版本做合并。此外,还有一些不同的工具写成脚本,也有在过程中不断优化的工具。”

可以看到,测试的整个测试流程相当复杂的,从第一阶段开始跟芯片设计师谈早期的测试方案;第二阶段测试程序的设计,包括代码、调试等;到第三阶段把每个工程师调的不同流程整合构建在一起,形成一个完整的解决方案;第四阶段对代码做标准化,拿掉冗余的部分等;最终得到质量达标、成本低、又好用的方案发布生产。

在工具方面,首先是IG-XL软件,是ATE行业中用户最广,评价最高同开发软件,其实用性、易用性和稳定性都处于业界领先水平。泰瑞达所有的Soc测试设备都采用这个开发环境,便于用户开发。

其次是Oasis,它是基于IG-XL软件的一个辅助工具,可以检测开发的代码质量,比如,在Offline阶段运行Oasis工具,可以自动看不同工程师写出来的代码有没有错、有没有冗余。

还有一款全流程管理软件DevOps,这是一款完全自动化的全流程管理软件,基于IG-XL开发软件和Oasis辅助软件来保证代码调试过程的质量。工程师开始开发一个测试程序的时候,从Offline阶段就会自动调用Oasis中的Offline检测工具,生成一个报告,将问题发到相关工程师的邮箱,直到把报告中的的问题全部修复以后才会进入到下一个阶段。

另外,Felix Huang先生重点谈到公司的一款数据分析工具UltraEDGE。在整个见面会上,Felix Huang先生多次强调数据,整个流程从前到后流动的就是大数据,海量的数据支撑来达到0 DPPM。这款工具可以在前面的测试结果出来之后,进行数据分析和反馈。

UltraEDGE具体如何工作呢?如上图,晶圆从中间刻蚀机出来之后上右侧的ATE测试机。晶圆测试完成后,大量数据进入UltraEDGE,在里面可以自建一些FDE Fault Detect Engine工具,进行质量和数据统计;也可以在上面安装第三方数据分析软件,比如OptimalPlus、PDF数据管理软件,在其中进行加密和机器学习,对抓取到的原始数据进行分析。之后形成晶圆图,在晶圆上的多个Die中,绿色表示通过,红色表示失效,蓝色表示可能有一些是边缘性的问题。把一些潜在的缺陷问题体现出来,反馈给Foundry,从而进行工艺的调整和改善。UltraEDGE最终目的是提升良率,降低成本。

总结

如今汽车电动化、智能化是未来趋势,车规芯片的市场需求将会越来越大。同时车规芯片对质量的要求也更高。对于芯片企业来说,选择合适的测试方案,有助于企业以更低成本打造出高质量的产品,并能够以更快速的时间实现上市。泰瑞达拥有全覆盖的测试机台,能够针对不同企业不同芯片设计合适的测试策略,同时它也创新性研发出各种工具,使得测试的各个环节更加高效,真正助力芯片企业达成高质量低成本目标。

-

泰瑞达与合肥工业大学“半导体测试技术联合实验室”2024-06-06 1206

-

泰瑞达Jason Zee:新能源汽车市场快速发展,优秀的测试策略提升芯片测试效率2023-12-26 2017

-

兆易创新全系列车规级存储产品累计出货1亿颗2023-04-13 1362

-

车规芯片验证的流程与展望2023-02-13 2197

-

英飞凌举行各项质量项目,向实现“零缺陷”的质量终极目标不断前进。2020-09-16 3044

-

买助力车电池当心返厂货2010-01-14 807

-

电动助力车铅酸蓄电池生产的过程控制2009-11-07 1047

-

什么是电动助力车?电动助力车国家标准及内容2009-11-06 7721

-

电动助力车蓄电池2009-11-05 613

-

德曼高能电动助力车电池2009-10-29 656

-

电动助力车充电器电路图2009-05-29 3598

全部0条评论

快来发表一下你的评论吧 !