SDC约束文件中常见的基础命令总结

描述

本文记录SDC约束文件中比较复杂的一些命令,包括时钟分频、时序例外、多周期约束、半周期约束、多时钟约束等。感觉项目中能用到的基础命令差不多就总结完了。

时钟分频

时钟信号穿过时序单元分频之后,需要人为设置generated clock,工具才能够正确推导分频之后的时钟。因为EDA工具在STA时,时钟信号不能穿透时序单元传播。

命令:

create_generated_clock -divide_by 2 -name CLKG -source [get_ports CLK] [get_pins FF1/Q]

set_clock_latency value [get_clocks CLKG] #设置延时

set_clock_uncertainty value [get_clocks CLKG] #设置不确定性

set_clock_transition value [get_clocks CLKG] #设置转换时间

除-divide_by之外,还可以采用-edges更精确的表明相对于master clock,generated clock的时钟跳变边沿。

False Path

某些情况下,设计中的确存在某些路径,但是这些路径之间的时序是不可能的,或者不是真实的,就要设置false path,让工具不再对该路径进行STA(注意只是不进行时序分析,路径还是存在的)。比如跨时钟域之间的路径,不会跳变的路径等,或者不可能的路径等。命令为:

set_false_path

互斥时钟

多个时钟是同步的,但是逻辑是相互排斥的,比如通过MUX二选一的时钟,他们之间的时序路径也不需要分析,为了让工具不再优化两时钟之间的时序,可以用两种命令约束:

方法1:

set_false_path -from [get_clocks CLK1] -to [get_clocks CLK2]

方法2:

set_clock_group -logically_exclusive -group CLK1 -group CLK2

-logical_exclusive表示两个时钟在逻辑上是不能同时存在的。如果物理上不能同时存在,比如同一个时钟源定义了两个时钟,就要采用-physically_exclusive。

异步时钟

两个设计的时钟来自于两个不同的晶振,时钟源没有任何关系,频率不确定,相位不确定,这两个时钟就叫异步时钟,工具无法对异步时钟进行时序分析,也没必要进行时序分析。但是设计人员要确保信号在异步时钟域之间的传输时不出现亚稳态。一般采用打两拍、握手、fifo等跨时钟域处理方式。

命令为:

set_clock -asynchronous -group CLKA -group CLKB

set_case_analysis

用于约束固定0/1,或者只有上升沿/下降沿的端口,在这个端口散出的路径中,就只有0/1,或者只分析上升沿/下降沿。在MMMC设置中,经常用这个设置芯片的不同工作模式。

多周期设计

在设计中,当两个寄存器之间的组合逻辑路径里,数据传输花费的时间多于一个时钟周期,就需要为这个组合逻辑路径声明为多时钟周期路径。

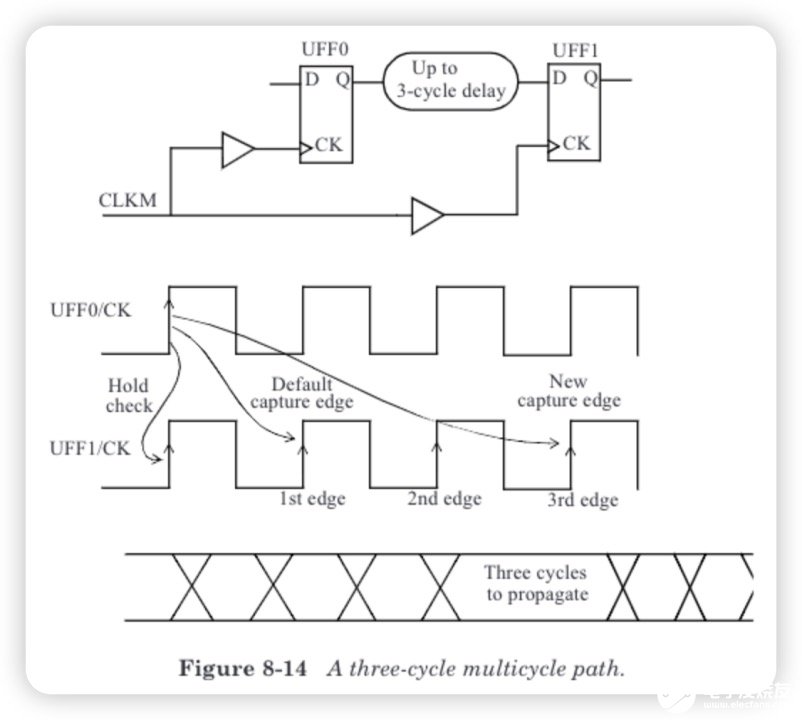

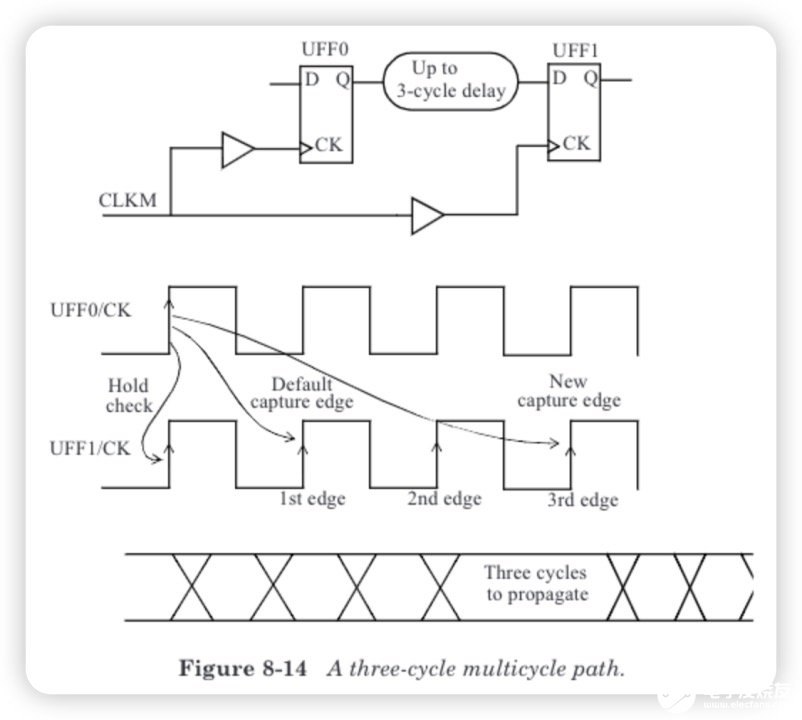

上图中,两个寄存器之间的组合路径需要3个时钟周期。对建立时间的约束命令为:

create_clock-nameCLKM -period 10 [get_portsCLKM]

set_multicycle_path 3 -setup -from[get_pins UFF0/Q] -to [get_pinsUFF1/D]

接下来考虑hold时间检查,默认的hold检查是setup之前的有效沿(2nd edge),但是实际上数据不需要经过这么久的延时,实际上hold检查的合理有效沿需要提前2个周期(setup-1),因此hold约束命令为:

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

此外,如果该多时钟周期路径分为两个部分A和B,其中A的延时为3 clock cycles,B的延时是一个标准的时钟周期,那么可以只用-through选项约束慢速的部分。命令:

set_multicycle_path 3 -setup -throug SLOW

set_multicycle_path 2 -hold -through SLOW

Half-Cycle Paths

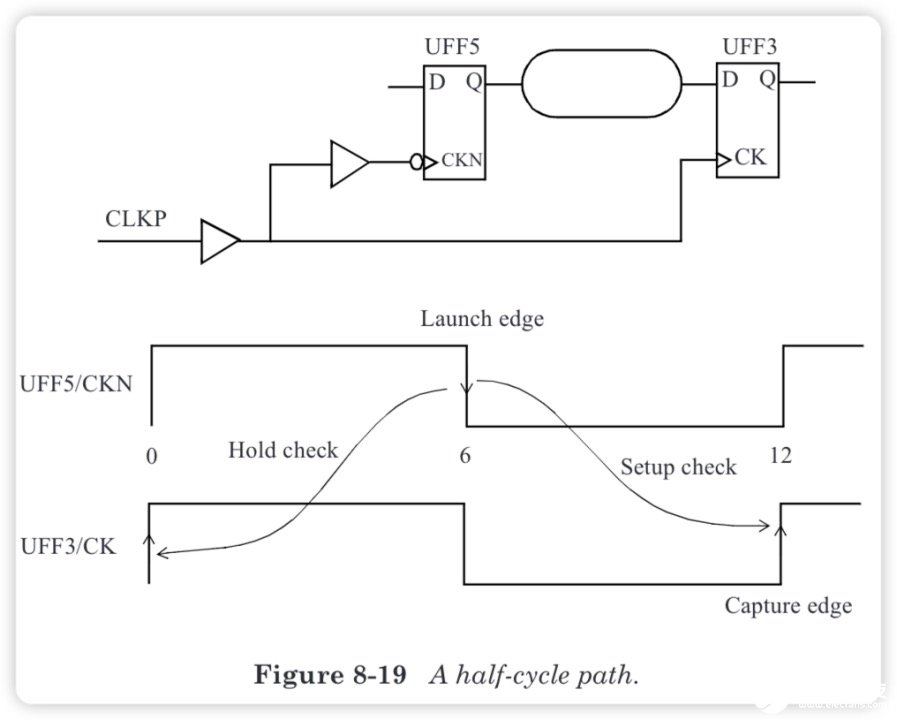

当设计中同时存在上升沿和下降沿出发的场景,就很可能存在half-cycle path。比如上升沿出发的寄存器到下降沿触发的寄存器或者下降沿出发的寄存器到上升沿触发的寄存器,如下所示。

建立时间中,数据的Arrive Time等于下降沿的6ns延时加上数据的延时,Require Time为12ns的时钟周期。即数据只有半个时钟周期的时间,因此对建立时间的约束更苛刻了。

保持时间的含义是在时钟沿跳变时,上一个状态不能变化太快。如上图所示,保持时间的检查的有效沿为caputre edge的上一个上升沿,由于launch edge已经有半个周期6ns的延时了,因此数据总是在6ns之后才来的,因此保持时间的裕量特别大。

多时钟约束

设计内部包含多个时钟,但是所有时钟都通过一个时钟源分频得到,这种是同步时钟,相位都是固定的。工具在分析时序时,会自动计算两时钟信号相邻最近的相位的时间差,作为STA检查中的Require Time。

在输入/出端口,一个输入/出对应着多个时钟的输入,这种需要对该端口进行多约束。

多时钟输入延时

create_clock CLKA #内部时钟

create_clock CLKB #外部时钟

set_input_delay 1 -clock CLKB -max 【get_ports A】

其中CLKA为待优化模块内部的采集端口A数据的时钟,CLKB为待优化模块外部驱动数据进入端口A的虚拟时钟。

多时钟输出延时

create_clock CLKA #内部时钟

create_clock CLKB #外部采集时钟B

create_clock CLKC #外部采集时钟C

set_output_delay 1 -clock CLKB -max 【get_ports A】

set_output_delay 1 -clock CLKC -add_delay -max 【get_ports A】

Removal/Recovery Timing

可以理解为复位信号的“Setup/Hold Time”。

审核编辑:黄飞

-

时序约束实操2024-04-28 3773

-

时序分析的设计约束(SDC)2022-11-08 10562

-

聊聊ASIC设计约束与SDC命令2023-07-11 1283

-

ASIC设计约束与SDC命令介绍2023-07-12 2216

-

Linux中常用的压缩和解压缩命令介绍2023-07-31 2844

-

时序约束 专版2013-05-16 2752

-

Linux系统中常见的压缩命令工具概述2019-07-09 1286

-

常见的约束命令有哪几种呢2021-11-02 3186

-

总结嵌入式系统开发中常见的存储器及其特点2021-12-17 1496

-

FPGA的reset信号需要加什么SDC约束呢?2023-04-23 2364

-

请问时序约束文件SDC支持哪些约束?2023-08-11 780

-

如何将Altera的SDC约束转换为Xilinx XDC约束2018-11-27 6073

-

时序分析的设计约束SDC怎么写呢?2023-06-18 6617

-

时序分析基本概念—SDC概述2023-07-03 8912

-

ASIC设计约束与SDC命令2023-07-09 1595

全部0条评论

快来发表一下你的评论吧 !