二极管器件在ESD防护中的作用

描述

二极管在早期IC电路的ESD防护中一直扮演着重要角色。即便现在二极管依然在ESD防护中发挥着重要的作用。这期就讲一下二极管在ESD防护中的作用。在ESD防护中所应用的二极管分为两种:一种为二极管器件,一种为寄生二极管。这一期先讲一下二极管器件。

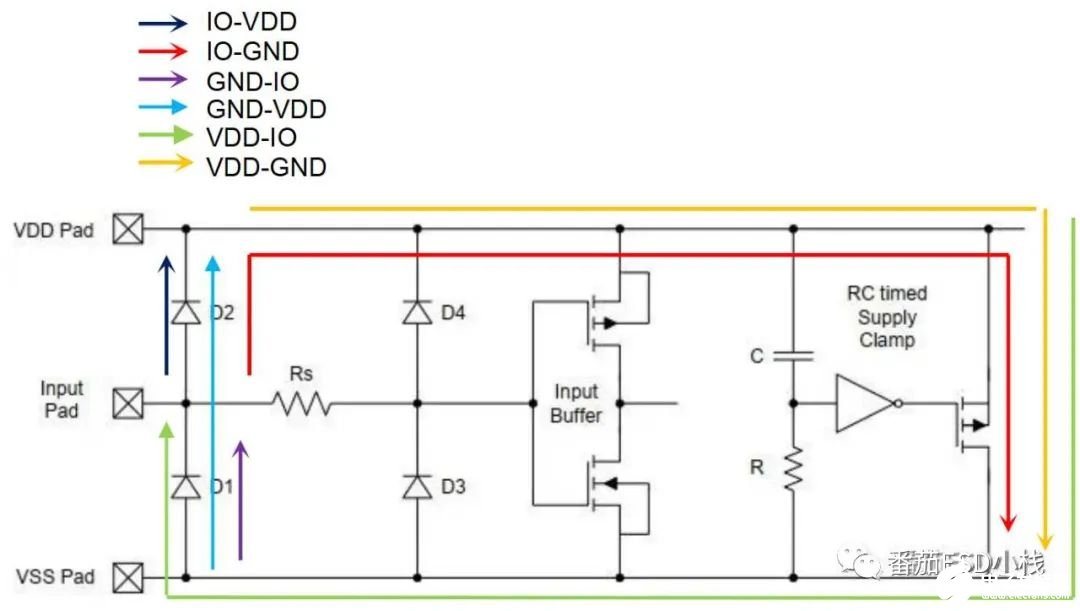

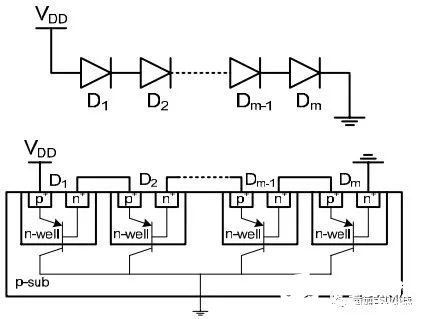

早期工艺都是使用单个反偏二极管作为ESD防护器件。但是这种设计方法只适用于大线宽工艺。随着工艺的进步,现阶段的ESD防护策略已经不建议二极管反偏击穿泄放ESD电流,因为现在的工艺下需要更大面积才能避免二极管发生热击穿。(随着线宽的减小热击穿与雪崩击穿的界限也愈加模糊) 一.端口的ESD防护 现阶段二极管通常与GCNMOS一起构成ESD防护网络,二极管应用于端口,GCNMOS作为Power Clamp,具体电路如下图所示。

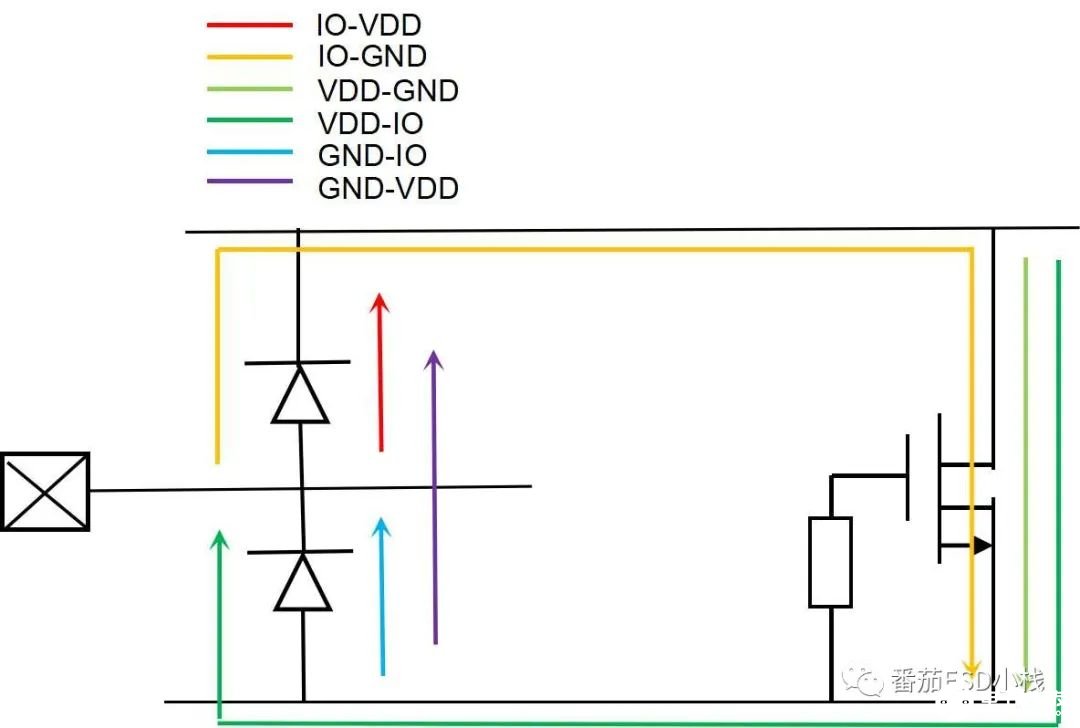

图一.二极管+GCNMOS ESD网络工作原理图。 整个ESD网络的工作原理如图所示,整个网络中,二极管都工作在正向导通的情况下。通过二极管将IO端口的ESD泄放到VDD-Rail上,亦或是将GND-Rail上的ESD电路泄放到IO。当ESD电流进入VDD-Rail,RC触发单元开启NMOS沟道,形成泄放通路。(Power Clamp 只能被VDD-Rail上的ESD触发开启,具体细节可看前几期浅谈GCNMOS )如下图所示,笔者还见过另外一种ESD网络。

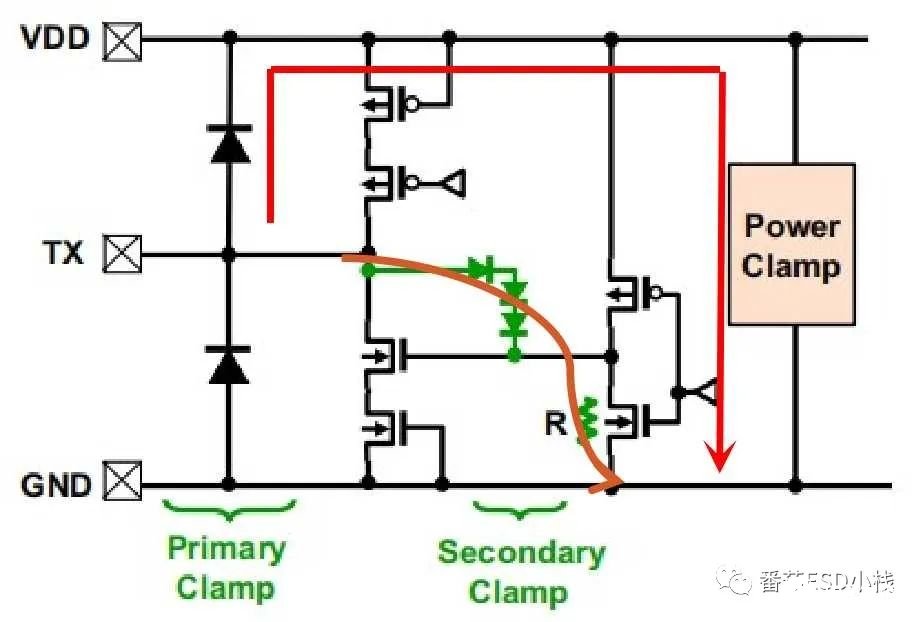

图二.二极管+GGNMOS ESD网络工作原理图。 图一的ESD网络属于频率触发机制,而该ESD网络属于电压触发机制。端口到GND的泄放路径的Trigger Voltage为正偏二极管+ GGNMOS,这种设计会提升ESD网络的Trigger Voltage。一般用于多电压域共地电路,如果多电压域采用GCNMOS作为Power Clamp,那么每个电压域都需要一个RC触发电路,面积不划算。 二.Gate Clamp 还可以用二极管实现Gate Clamp 技术。该技术简而言之就是使用二极管将MOS管的源/漏与栅端进行连接,利用二极管的钳位特性保护易出现失效的MOS管。

图三.Gate Clamp应用实例。 通过控制二极管串的数量,调整Gate Clamp的Design Window使其在正常工作时关闭,发生ESD时开启。要求其开启电压要大于Absolute Max的1.1倍,小于栅漏的BreakDown Voltage 。从而实现对Main driver中NMOS的保护。

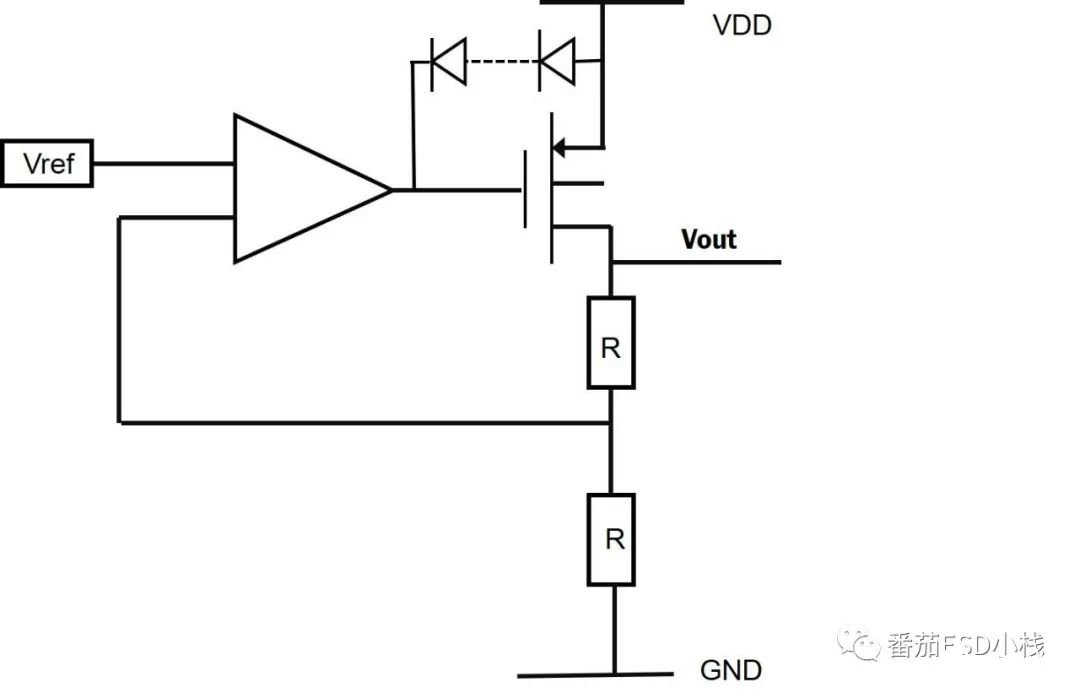

图四.LDO中Gate Clamp的应用。 另外笔者也对电源管理芯片中LDO的功率管设计过Gate Clamp技术,因为使用场景中VDD上会存在浪涌,为了保护LDO的功率管,在PMOS的源端与栅端连接了二极管串。通过控制二极管的数量,确保正常工作时VDD与误差放大器的压差无法开启Gate Clamp。当VDD发生浪涌时,通过Gate Clamp钳住功率管的VGS,起到保护的作用。(这个方案后续作废了,这里只是为从ESD保护的角度为读者提供思路,便于理解。) 三.二极管串 二极管串也可以作为Power Clamp,如图所示。

图五.二极管串及刨面图。

使用二极管串作为Power Clamp的工作原理与Gate Clamp类似,通过调整二极管的数量,控制二极管串的开启电压位于Design Window内。但是这种设计目前有两个弊端:

1.二极管是典型的Non-Snap-Back器件,其开启后IV特性还会表现出一定斜率,所以其防护性能不如GGNMOS等Snap-Back型器件。

2.二极管串与衬底间存在寄生三极管,会构成达林顿组态,从而导致开启电压的进一步降低。为了保持足够高的开启电压,需要串联更多的二极管,但是更多的二极管又会增强达林顿组态。所以二极管串作为Power Clamp的设计并不多见。

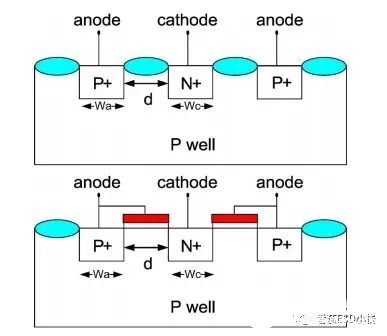

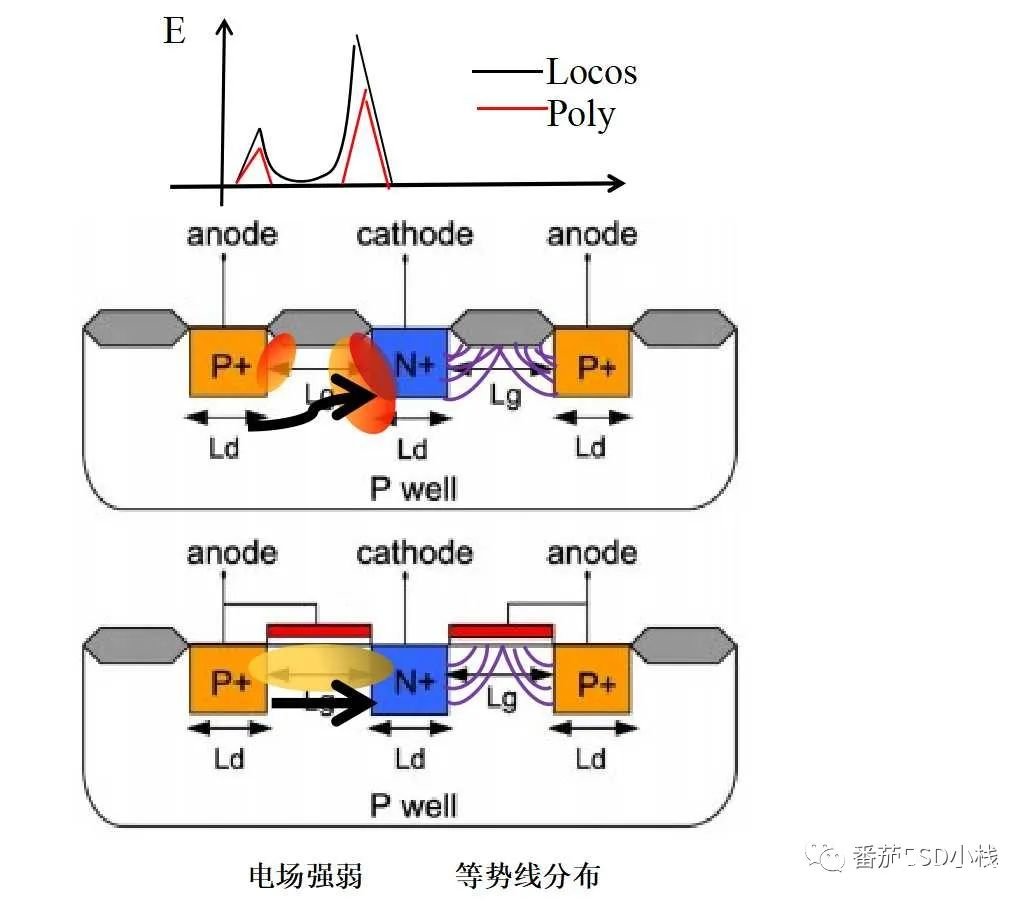

四.Locos-Bound 二极管与Polysilicon-Bound二极管 常见的二极管都是STI或者LOCOS作为隔离结构,但是现阶段为了提高ESD能力,出现了以Poly作为隔离结构的Polysilicon-Bound,具体如图所示。

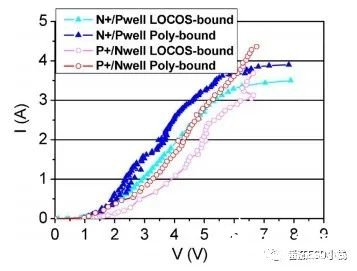

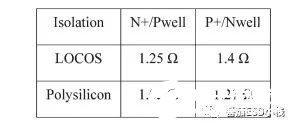

图六.Locos-Bound diode与Polysilicon-Bound diode。 Locos-Bound diode阴极与阳极有源区间采用LOCOS作为隔离结构,而Polysilicon-Bound diode阴极与阳极间采用多晶硅作为隔离结构。后者具有更加优秀的电流承载能力与更小的开启电阻,Polysilicon-Bound diode的二次击穿电流It2与开启电阻Ron都优于传统Locos-Bound diode。

图六.Locos-Bound diode与Polysilicon-Bound diode IV曲线对比。

图七.Locos-Bound diode与Polysilicon-Bound diode 开启电阻对比。

图八.Locos-Bound diode与Polysilicon-Bound diode电场分布图。 无论Locoss-Bound diode还是STI-Bound diode都会因为氧化物隔离而在有源区边缘引入应力,从而造成晶格适配形成势垒,使得电场在有源区与隔离的接触面更为集中。另一方面氧化物隔离的存在会使得电场线分布更加密集。反之,Polysilicon-Bound diode 整个N-Well较为均匀,晶格缺陷与位错较少。电场分布均匀,且电场线在有源区边缘也较为均匀。这使得Polysilicon-Bound diode具有均匀的电场分布和更加优秀的载流子迁移率。更为直观解释便是Polysilicon-Bound diode的载流子迁移路径更短(不需要绕过氧化物隔离),阱电阻更低,所以过电流能力强,开启电阻低。但是相对的,Polysilicon-Bound diode的击穿电压会略低于Locos-Bound diode(从数据上看差距并不明显)。

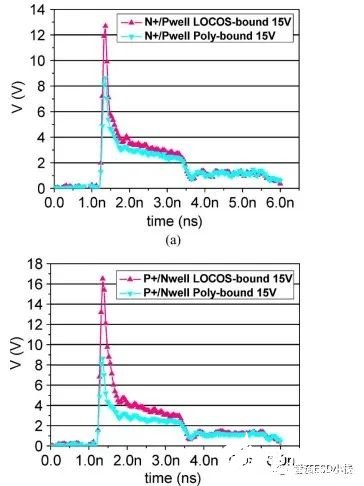

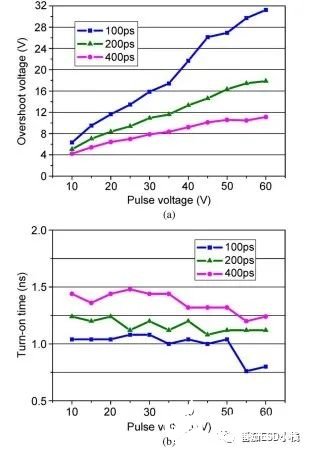

同时得益于器件内异质结电容的减少(异质结容值较小,只对ps级别的CDM放电产生影响),Polysilicon-Bound diode表现出更优异的CDM防护性能。如图所示,Polysilicon-Bound diode在VFTLP下的过冲电压远低于Locos-Bound diode,同时其对高频CDM具有良好的开启时间。

图九.Locos-Bound diode与Polysilicon-Bound diode在VFTLP下的过冲电压。

图十.Polysilicon-Bound diode在VFTLP不同上升脉冲下的过冲电压与开启时间。 针对CDM放电,开启时间的重要性远大于泄电流能力。所以Polysilicon-Bound diode针对CDM放电具有更加优异的表现。目前笔者所接触的国产工艺中还没有见过Fab提供Polysilicon-Bound diode的标准单元,可能SMIC的先进工艺会提供该二极管的pdk。相较于SCR笔者认为这种二极管推广难度更低,也确实能在一定程度上提高ESD性能。

审核编辑:黄飞

-

ESD二极管在电压箝位的应用2018-10-17 2047

-

ESD静电二极管,如何正确选择合适的型号?2018-10-19 4955

-

ESD保护二极管,一种有效的ESD静电保护器件2018-10-30 3214

-

TVS管与ESD保护二极管在应用中的不同2020-09-24 3454

-

ESD二极管,在便携式电子产品中的应用2021-07-16 3780

-

TVS二极管与ESD二极管之间的区别是什么2021-04-08 26754

-

ESD静电二极管的原理是什么2022-06-01 10312

-

ESD静电保护元件对比(压敏电阻/TVS/ESD静电二极管)2022-07-05 5503

-

防护元器件|ESD静电二极管优势、选型总结说明2022-09-14 2200

-

ESD防护之ESD静电二极管2022-11-01 2552

-

ESD二极管能否代替TVS管?2023-06-13 5221

-

ESD静电二极管有什么作用?ESD静电二极管的应用领域2023-12-29 2657

-

简述TVS二极管在ESD防护中的特点及优势2024-01-03 1661

-

esd二极管和tvs二极管差别2024-01-11 3642

-

ESD保护二极管的作用和应用2024-09-13 3585

全部0条评论

快来发表一下你的评论吧 !