未来,集成电路的发展到底会是什么样子?

制造/封装

描述

未来,集成电路的发展到底会是什么样子的呢?我们满怀期待。 我们需要了解一些关于科学的历史,至少在自己研究的领域要深入了解。 今天,我们无数次地探索、迷途、失败和成功,将得到未来人们热情、客观、公正的评定。

上面两句话,是对电子集成技术历史和未来的认知,也是写这篇文章的初衷。

这篇文章,我们回顾历史,缅怀电子集成技术的先贤,正是他们的发明或发现改变了电子集成技术的历史,也改变了今天我们生活的世界。

同时,我们展望电子集成技术的未来,满怀希望,未来可期,并对电子集成技术的未来进行合理的预期。

文章最早发表于2022年4月21日,今日稍作修正,重新分享给读者。

集成的历史

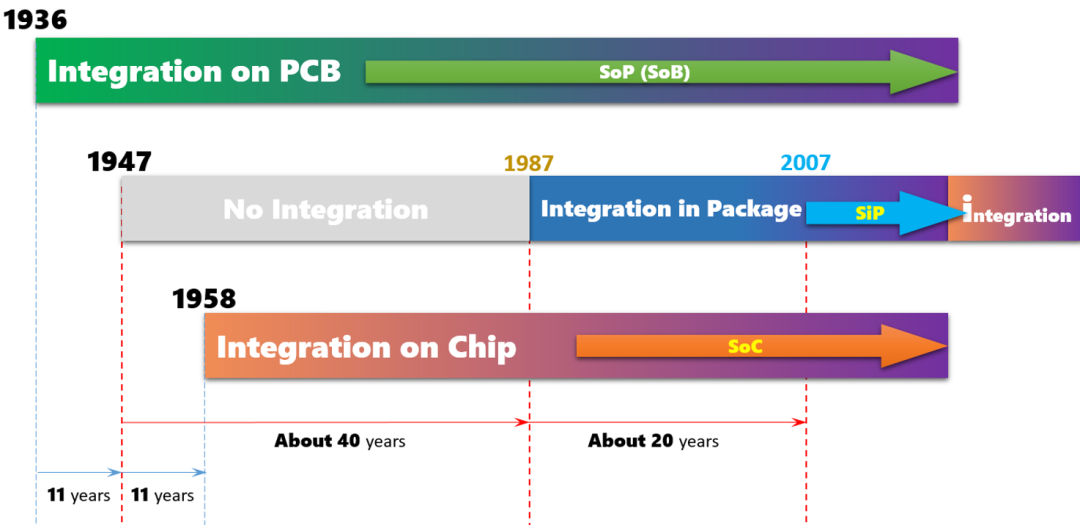

1936、1947、1958 是电子集成技术历史上至关重要的三个年份。

1936

1936年,奥地利人保罗 • 爱斯勒(Paul Eisler)发明了世界上第一块PCB,安装在一台收音机里面。

这块看似简陋的PCB却开创了一个时代,电气互连(interconnection)的平面工艺时代,并对二十多年后出现的集成电路的平面工艺产生了启迪式的影响。

正是因为平面工艺,集成电路才能不断提高互连密度,并追寻摩尔定律步伐,走到今天的辉煌,遍布现代文明的方方面面。

爱斯勒当时获得了几项关于蚀刻工艺的专利,蚀刻最终演变成众所周知的光刻工艺,今天得到广泛使用,是芯片制造中最为关键的技术。

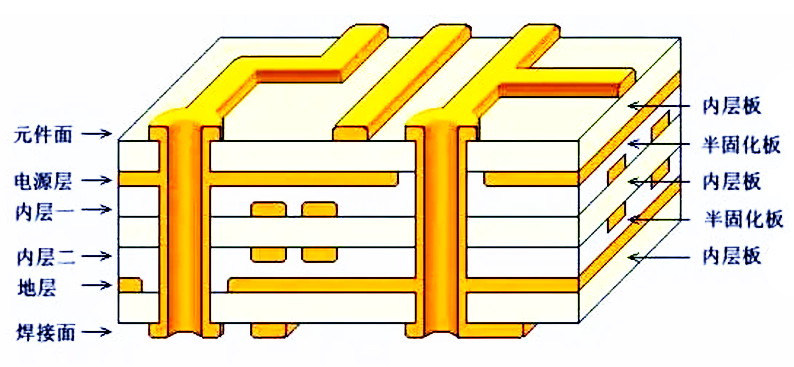

在PCB出现之前,电子元器件之间的连接是依靠电线直接连接完成的。 外行人都可以看出,这种依赖电线直接互连的方式,其密度是难以提升的。 而以平面工艺为基础的PCB,其密度可以得到极大的提高,目前最先进的PCB工艺,其布线密度已经可以达到10um线宽/线距,也就是说,在1mm的空间内,可以排布50根金属布线,更直观的说法就是10um金属布线的宽度只有人类头发丝直径的1/5~1/10。

今天,PCB上的布线密度和组装密度也逐渐趋于极限,多年来已没有明显的提升,并且受芯片封装尺寸和引脚密度影响,PCB上的器件组装密度也难以继续提高。

人类认识世界,必定是和自身相近的尺度开始,人类改造世界,也是为了自身服务,其创造的产品也必然和自身的尺度相适应。 在电子集成技术的三个层次中,PCB的尺度最接近人类自身的尺度。因此,PCB从诞生之初直到现在,依然在人类世界中扮演着重要的角色。 1947 1947年是技术史一个非常重要的年份,因为这一年,晶体管被发明出来了。 晶体管神奇性在于,这是人类发明的尺度可以不断缩小而功能保持不变的功能单元,今天的晶体管其尺度仅为最初的亿万分之一,而其功能竟然能神奇地保持不变,因此,这无疑是人类科技史上最伟大的发明。

晶体管是集成电路的基本单元,我们称之为功能细胞,没有晶体管的发明,就不可能发明集成电路。

晶体管发明9年后,贝尔实验室的肖克利、巴丁、布拉顿三人,因发明晶体管同时荣获1956年诺贝尔物理学奖。

晶体管虽然很神奇,但比较脆弱,需要保护,因此在晶体管发明的同一年,电子封装也出现了,其首要任务就是对晶体管进行保护,并通过引线进行晶体管内部和外部的电气连接,晶体管的发明同时也开创了微电子封装的历史。

今天,先进封装技术如火如荼,成为业内关注的焦点,头部厂商都在积极研发先进封装技术,从台积电到三星,从Intel到AMD,从苹果到华为...... 人们难以想象,一直作为配角的封装,今天竟然也能站在舞台的中央。

究其原因,还是因为其功能发生了重大的改变,电子封装从原本的芯片保护、尺度放大、电气互连三大基本功能,在进化为先进封装后,增加了提升功能密度、缩短互连长度、进行系统重构三大新功能。

原本属于边缘技术的封装在提升了这三大独门绝技之后,竟然可以号令武林,成为半导体江湖中人人关注、炙手可热的宝典。

这就如同一个从穷乡僻壤边远乡村长大的孩子,默默无闻,通过持续不懈地努力,掌握了先进的技术和非凡的能力,碰上合适的机会,终有一天脱胎换骨,并成就一番事业。

是的,封装的发展历史竟然也是如此的励志!

1958

杰克 • 基尔比身高两米,性情温和,是德州仪器一名工程师,他一直认为作为功能单元的晶体管、电阻、电容等元器件可以在一块芯片上制作出来,并为此做出了不懈的努力。

终于,在晶体管发明11年后的1958年,基尔比发明了地球上第一款块IC集成电路,内含5个元器件。

基尔比成功地实现了把所有元器件集成在一块半导体材料上的构想。

罗伯特 • 诺伊斯风度翩翩,热情四溢,并且富有远见,是一位科技界和商业界的奇才。他在基尔比的基础上发明了平面工艺集成电路,使半导体产业由“发明时代”进入了“商用时代”。

作为工程师,诺伊斯研究出二氧化硅扩散技术和PN结隔离技术,并创造性地在氧化膜上制作出铝连线,使元件和导线连接一体,从而奠定了集成电路的平面工艺、为工业大批量生产打下了坚实的基础。

我想诺伊斯一定是受了保罗·爱斯勒的启发,将源于PCB上的平面工艺应用到了集成电路上,从而奠定了集成电路大规模制造的基础。

作为企业家,诺伊斯和摩尔一起创办了两家硅谷最传奇的公司:仙童和英特尔。

基尔比因为发明集成电路而获得2000年的诺贝尔物理学奖,颁奖词中写到:集成电路的发明为现代信息技术奠定了基础。

诺伊斯1990年因为心脏病突发去世,从而与诺贝尔奖无缘,基尔比在领奖的时候说,如果诺伊斯还活着,一定会和他一起分享诺奖。

有时候,人生的成功就在于你是否能被别人活得更久一些。

事实上,现在的集成电路基本上走的是罗伯特 • 诺伊斯的技术路线。基尔比在半导体锗上制作出了多个元器件,元器件之间的互连用的还是飞线;诺伊斯采用了半导体硅作为基底,并且元器件间的金属互连也是通过平面工艺制作在硅片上。

六十多年后的今天,一平方毫米的芯片上可以集成1亿只以上的晶体管,单个芯片上的晶体管数量已经达到数百亿量级。

下图依次是苹果公司的M1,M1 Pro,M1 Max,M1 Ultra芯片。

M1 芯片拥有 160 亿个晶体管,M1 Pro 拥有 337 亿个晶体管,M1 Max 拥有 570 亿个晶体管,M1 Ultra上的晶体数量多达1140亿。

今天,我们用手指在手机上轻松点击几下,就能完成各种操作和任务,不由得感慨技术的的进步,也由衷地感谢那些做出伟大发明的技术先贤们。

下面我们给出一张图,比较全面地概括了电子集成技术发展的历史:

是的,1936、1947、1958 是电子集成技术历史上至关重要的三个年份。

粒子物理标准模型的奠基人,已故物理学家史蒂芬 • 温博格说过:Learn something about the history of science, or at a minimum the history of your own branch of science.

了解一些关于科学的历史,至少在你研究的领域要了解,就作为这篇文章前半部分的尾声吧!

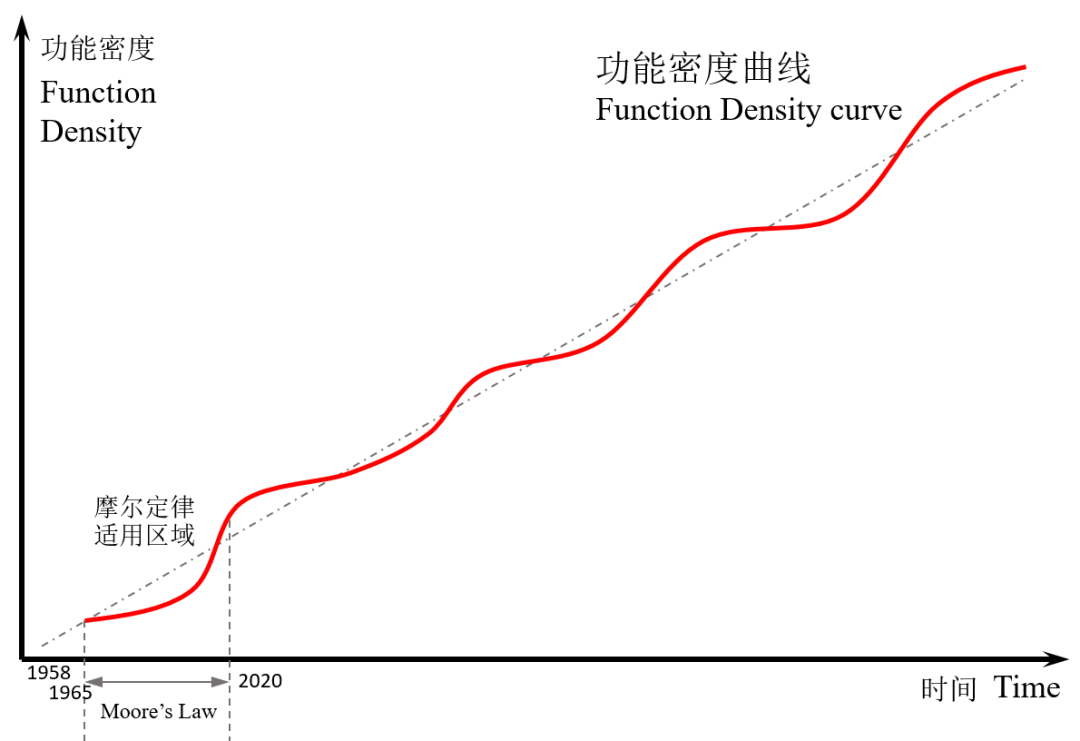

集成的未来 人类既无法改变历史,也难以掌控未来,那生命的意义又何在呢? 答案或许就是:相信未来! 那么,集成的未来会是什么样子呢? 探寻更小的功能细胞 从集成电路发明以来,作为功能细胞的晶体管已经缩小了亿万倍。 功能细胞的逐步缩小,有没有尽头呢?我个人认为,集成的尽头是:原子。 我们知道,硅基半导体,1nm³中包含50个硅原子,并以此推断出7nm芯片中,单个晶体管包含的硅原子数量约为5000万个。 随着晶体管工艺尺寸的缩小,单个晶体管中包含的硅原子数量肯定会越来越少。那么,少到什么是尽头呢? 新型的晶体管,例如单原子晶体管,其最小结构宽度仅为一个原子,通过操作单个原子来控制晶体管的导通和关断。 据称,单原子晶体管的能耗将只有硅基晶体管的万分之一(1/10000),这对未来应用是一个决定性的优势。 打个比方,如果以单原子晶体管为功能细胞的芯片成功量产,这就意味着,现在每天一充的手机,可能需要几个月甚至几年才充一次电,想一想,待机焦虑完全消失,充电宝成为历史文物,这会是什么样的使用体验? 不过,我们需要注意的可就是如何保护自己的眼睛和身体了! 放大一下我们的视野,针对人类现有的文明来说,文明的尽头也是原子,如果打破原子,则必将带来文明的毁灭! 功能密度增长的持续性 在《基于SiP技术的微系统》一书的第一章中,我提出了功能密度定律(Function Density Law),作为摩尔定律失效后,对电子集成技术未来的一种合理预期。 其内容为:对于所有的电子系统来说,沿着时间轴,系统空间内的功能密度总是在持续不断地增大,并且会一直持续下去(For all electronic systems, along the time axis, the function density in system space is constantly increasing and will continue.) 下图所示为功能密度曲线,从曲线中我们可以看出,在电子集成技术发展的初期,电子系统的功能密度随时间的变化是按照摩尔定律增长的,其曲线呈现指数增长趋势。随着摩尔定律的逐渐失效,其曲线逐渐平缓,但功能密度依然保持增长。

从长远来看,功能密度曲线是一条单调增长的波动曲线,随着新技术的不断涌现,在不同的历史阶段,其增长的斜率是不同的,甚至在某些特定的区间,可以以指数规律进行增长。 摩尔定律的指数增长规律决定了其物理意义上的不可持续性,而功能密度定律则是可以长期持续的。 电子集成技术的未来,必将遵循功能密度定律,系统空间内的功能密度会持续增加。 由PPA进化到PPV 今天,我们判定集成电路先进性的重要标志是单位面积内集成的晶体管数量,在未来,判定的标准将变成单位体积内集成的功能单位(Function UNITs)的数量。 做集成电路设计,有一个很重要的指标:PPA,分别指Power, Performance, Area。随着摩尔定律的失效,实现PPA指标也变得越来越难。因此,在后摩尔时代,PPA指标将进化成PPV指标,即Power, Performance, Volume。判断的标准也由单位面积变成了单位体积。 这里我们所说的Volume,通常是指系统空间,电子集成先进性的判断标准从单个芯片面积变为整个系统空间。 在前面的文章中,我提出了Cubic IC的概念,对未来的芯片形态做了预期。Cubic IC简称CIC,是一种新型的集成电路设计思路。 关于CIC详细的解读,请参考本公众号前面的原创文章:集成电路设计的“新思路”,或许,未来的集成电路真的就是文中所描述的样子。 在几乎穷尽了元素周期表中的元素之后,集成电路的发展必将穷尽系统空间的每一个角落,其功能密度将会持续增加...... 未来,集成电路到底会是什么样子的呢?让我们拭目以待。

审核编辑:黄飞

-

【自由畅想】未来的传感器会是什么样子的?2014-08-15 29249

-

请问电容滤波电路经过电容滤波之后会是什么样子?2019-09-17 5594

-

集成电路883与集成电路883b到底有哪些区别呢2021-11-01 2603

-

未来环保汽车会是什么样?2010-04-07 2031

-

我国集成电路的发展现状到底是什么样子?2018-07-25 14195

-

未来的工厂会是什么样子的呢?人工智能(AI)在未来的工厂的作用概述2018-05-19 11749

-

集成电路的未来发展2018-08-28 13268

-

PCB板的内部到底是什么样子2018-11-25 22674

-

乘坐自动驾驶汽车到底什么感觉?未来的汽车会是什么样的?2019-04-01 1781

-

未来存储技术的发展是什么样的2020-09-18 1697

-

未来的智慧城市会是什么样子2021-09-16 2114

-

来自未来的手机将会是什么样子2022-01-11 4932

-

发光的乐器在黑暗中会是什么样子2022-11-14 752

-

下一代硅光子技术会是什么样子?2023-07-05 1470

-

Chiplet的未来会是什么样子呢?2023-08-03 1849

全部0条评论

快来发表一下你的评论吧 !