D触发器变体来了,速看!

描述

什么是DRE触发器?

FF_DRE是一个具有异步设置(SET)和重置(RST)输入的边缘触发的D触发器(D Flip-Flop)

在任意时刻,当SET或RST为TRUE时会忽略CLK信号而设置或重置Q信号,RST比SET具有优先权,即RST和SET同为TRUE时,Q被重置为0。

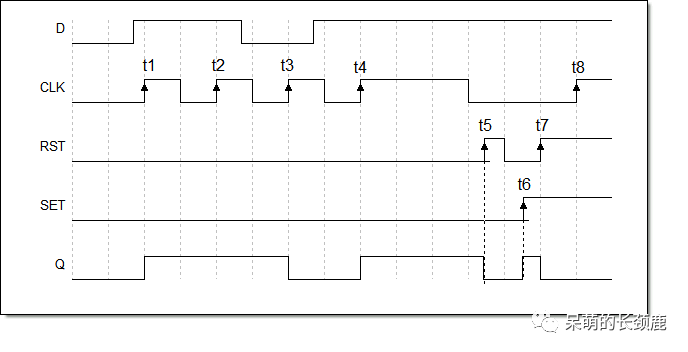

时间图如下:

特征表如下:

其中: CLK:时钟, RST:重置, SET: 设置 , D:输入 , Q:输出

- 假设最初 输入都为0,输出 Q = 0;

- 在t1处,RST=SET=0,D=1 ,输出Q=1;

- 在t2处,RST=SET=0,D=1 ,输出Q=1;

- 在t3处,RST=SET=0,D=0 ,输出Q=0;

- 在t4处,RST=SET=0,D=1 ,输出Q=1;

- 在t5处,RST=1 ,尽管D=1,但输出Q=0;

- 在t6处,RST=0,SET=1,输出Q=1;

- 在t7处,RST=SET=1,RST具有优先权,输出Q=0;

- 在t8处,RST=1,尽管CLK上升沿,但输出Q=0;

源代码如下:

FUNCTION_BLOCK "FF_DRE"

TITLE = 'FF_DRE'

{ S7_Optimized_Access := 'TRUE' }

VERSION : 0.1

VAR_INPUT

SET : Bool;

D : Bool;

CLK : Bool;

RST : Bool;

END_VAR

VAR_OUTPUT

Q : Bool;

END_VAR

VAR

edge : Bool;

END_VAR

BEGIN

IF #RST OR #SET THEN

#Q := NOT #RST;

ELSIF #CLK AND NOT #edge THEN

#Q := #D;

END_IF;

#edge := #CLK;

END_FUNCTION_BLOCK

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

d触发器是电平触发还是边沿触发2024-08-22 3409

-

d触发器有几个稳态 d触发器和rs触发器的区别2024-02-06 6463

-

什么是D触发器,D触发器如何工作的?2023-06-29 52610

-

D触发器不同应用下的电路图详解2023-01-06 10368

-

D触发器Verilog描述2012-02-22 4611

-

J-K触发器组成D触发器电路图2010-09-24 8987

-

D触发器组成T和J-K触发器电路图2010-09-20 22099

-

D触发器,D触发器是什么意思2010-03-08 5438

-

D触发器/J-K触发器的功能测试及其应用2009-02-14 5581

-

D触发器2008-10-20 3261

-

JK触发器 D触发器 RS触发器 T触发器 真值表2007-09-11 20528

全部0条评论

快来发表一下你的评论吧 !