RAM的两种应用:统计计数和位宽转换

电子说

描述

应用1 统计计数

在进行模块设计时,我们经常需要统计报文的数量,以供软件(or 主机)读取,有些统计仅仅用于debug,有些统计是协议要求,有些统计是为了便于功能实现。

当需要统计的数量较多时,为了降低功耗和减少面积,我们通常采用RAM去实现。

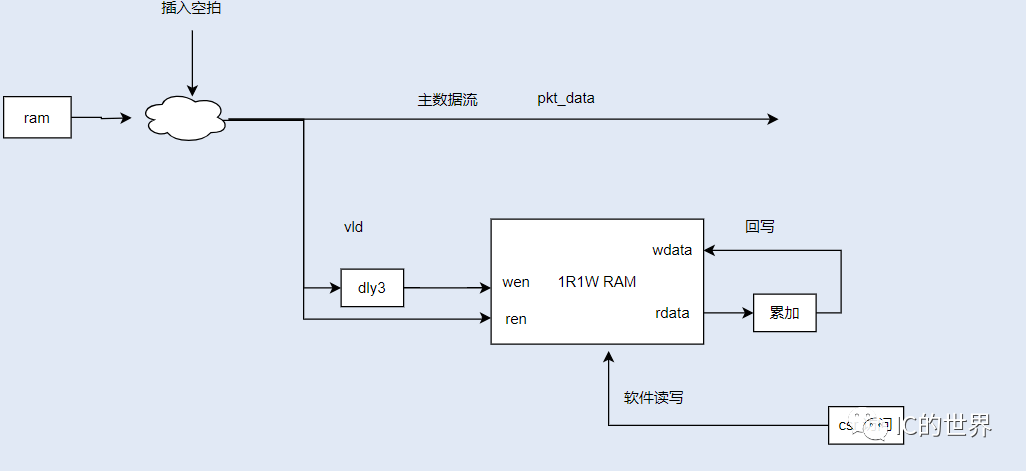

如下案例中,统计有效数据包的个数。

假设数据中存在pkt_id,pkt_id为0~63,则ram的深度为64。pkt_id用于作为读写地址。RAM读延时为3个时钟周期。

有数据来临时,pkt_vld作为读使能,读出当前包计数rdata,三个周期后,rdata加1回写到ram。

如下图所示:需要有三个注意事项

NOTE1:需要有读写保护,因为可能出现连续4个周期内,pkt_vld为1,且pkt_id相同,此时会出现同一个周期对相同的地址进行读写,因此需要RAM需要添加读写保护模块,保证数据能够正确写入,且读出的都是最新值,否则就会出现统计错误。

NOTE2:图中既有软件读、又存在硬件读,且硬件读优先级更高,软件读优先级低,因此为了保证软件读能够在有效周期内得到响应,因此需要在主数据流上插入空拍,避免出现软件读长时间无法响应而产生超时。

应用2 位宽转换

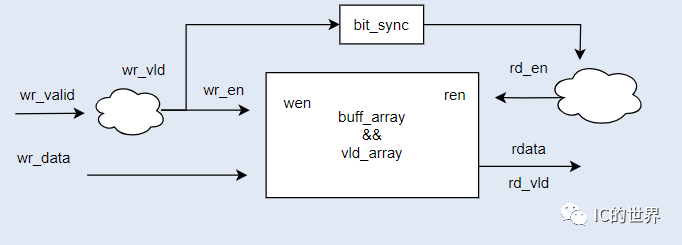

在进行模块设计时,我们经常需要进行数据位宽的转换,常见的两种转换场景有同步时钟域位宽转换和异步时钟域位宽转换。本文将介绍异步时钟域位宽转换

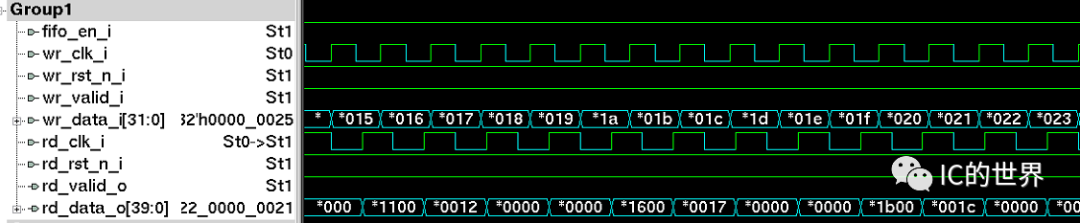

异步时钟域的位宽转换读时钟和写时钟属于两个时钟。如下案例中,数据位宽由32bit转40bit,写时钟频率156.25MHz,读时钟频率125Mhz,写数据为32bit,读数据位宽为40bit,通过计算得到入口数据速率和出口数据速率保持一致(156.2532==40125)。

存储模块是由寄存器搭建的。那么需要多大存储模块呢?32和40的最小公倍数为160,极限场景下,只需要160bit的寄存器作为存储就够了,但是读操作通常晚于写操作,并且考虑到时钟有抖动有偏移,为了避免溢出,稍微增加一部分缓存,我们可以采用320bit作为存储模块。因此写侧32bit写10次,读侧40bit读8次,读写两侧所需的时间相等。

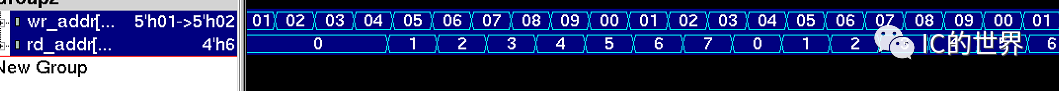

注意事项:写地址(wr_addr)跳转范围是09,读地址(rd_addr)跳转范围07。

如图所示:

buff_array为320bit的数据存储。

vld_array为80bit的有效标志位存储:vld_array[n]为1表示buff_array[4n+3:4n]存在4bit的有效数据。

always @(posedge wr_clk or negedge wr_rst_n) begin

if (~wr_rst_n) begin

buff_array <= {DATA_FIFO_DEPTH{1'b0}};

vld_array <= {VALID_FIFO_DEPTH{1'b0}};

end else begin

if (wr_en) begin

buff_array[ wr_addr*32 +: 32] <= wr_data_i;

vld_array[wr_addr*8 +: 8] <= {8{wr_valid_i}};

end

end

end

reg [10-1:0] rd_valid_bus;

reg [40-1:0] rd_data_bus;

always @(*) begin

rd_data_bus[40-1:0] = buff_array[ rd_addr*40 +: 40];

rd_valid_bus[10-1:0] = vld_array[rd_addr*10 +: 10];

end

integer i;

reg [40-1:0] rd_data_valid_mask;

always @(*) begin

for(i = 0; i < 40; i = i + 1) begin

rd_data_valid_mask[i] = rd_valid_bus[i/4];

end

end

always @(posedge rd_clk or negedge rd_rst_n) begin

if (~rd_rst_n) begin

rd_data_o <= {40{1'b0}};

rd_valid_o <= 1'b0;

end else begin

if (rd_en) begin

rd_data_o <= rd_data_bus & rd_data_valid_mask;

rd_valid_o <= |rd_valid_bus;

end else begin

rd_data_o <= {40{1'b0}};

rd_valid_o <= 1'b0;

end

end

end

审核编辑:汤梓红

-

测量开关电源转换效率的两种不同方法2022-08-09 5982

-

IC设计:ram的应用-异步时钟域位宽转换2023-11-23 1794

-

OpenCV两种不同方法实现粘连大米分割计数2024-01-22 2951

-

基于FPGA的HDTV视频图像灰度直方图统计算法设计2012-05-14 6025

-

AVR的两种位操作及比较2016-09-06 6712

-

STC12系列单片机的定时器有两种计数速率2021-11-25 1476

-

求分享S32G2内存映射系统计数器的地址2023-05-12 593

-

一种使用IP方法的独特统计计数器2017-09-18 798

-

FPGA设计中的RAM的两种实现方法2018-06-08 21068

-

统计信号连接到定时器的两种模式2020-06-08 3520

-

电平转换电路的两种设计方法2022-08-19 5199

-

FPGA设计中这两种情形该怎么约束2023-09-07 1288

-

IC设计:RAM的应用-统计计数2023-11-17 1287

-

浅析多晶硅锭中位错存在的两种来源2024-03-27 1977

-

同步计数器和异步计数器的区别2024-05-24 8416

全部0条评论

快来发表一下你的评论吧 !